首先來說一下USB這個(gè)大家都知道的東西吧:

USB通用串行總線,是應(yīng)用在計(jì)算機(jī)領(lǐng)域的接口技術(shù)。USB接口具有傳輸速度快,可以廣泛地應(yīng)用在各類的高速數(shù)據(jù)傳輸當(dāng)中,相比于大家熟悉的串口數(shù)據(jù)傳輸要快出不知道多少倍了。

我們最常見的當(dāng)屬USB2.0和USB3.0,這兩個(gè)之間可以通用,但是也有區(qū)別:

1.USB3.0的速率是5Gbps,而USB2.0的速率是480Mbps。

2.從USB外觀上來看,USB2.0通常是白色或黑色,而USB3.0則改為藍(lán)色接口。

3.從USB插口引腳上來看,USB2.0采用4針腳設(shè)計(jì),而USB3.0則采取9針腳設(shè)計(jì),相比而言USB3.0功能更強(qiáng)大。

總結(jié)來說就是USB2.0很通用,因?yàn)楹芏?a href="http://www.xsypw.cn/v/tag/1247/" target="_blank">電腦上可能沒有USB3.0的接口,但是一定有USB2.0的接口,而且USB2.0的傳輸速度也能滿足一般條件下的高速數(shù)據(jù)傳輸。

1.先附上所設(shè)計(jì)的實(shí)物圖(想要電路pcb文件咨詢博主),然后針對實(shí)物圖一點(diǎn)點(diǎn)展開:

所選用的芯片是Cypress 公司的EZ-USB FX2 是世界上第一款集成USB2.0 的微處理器,它集成了USB2.0 收發(fā)器、SIE(串行接口引擎)、增強(qiáng)的8051 微控制器和可編程的外圍接口。FX2 這種獨(dú)創(chuàng)性結(jié)構(gòu)可使數(shù)據(jù)傳輸率達(dá)到480MBit/s。在FX2中,智能SIE 可以硬件處理許多USB1.1 和USB2.0 協(xié)議,從而減少了開發(fā)時(shí)間

和確保了USB 的兼容性。該器件具有如下特性:

(1)內(nèi)嵌480MBit/s 的收發(fā)器,鎖相環(huán)PLL,串行接口引擎SIE集成了整個(gè)USB 2.0 協(xié)議的物理層。

(2)內(nèi)嵌可工作在48MHz 的增強(qiáng)型8051,該8051 控制器具有以下特征:

具有256Byte 的寄存器空間,兩個(gè)串口,三個(gè)定時(shí)器,兩個(gè)數(shù)據(jù)指

針。

四個(gè)機(jī)器周期(工作在48MHz 下時(shí)為83.3ns)即組成一個(gè)指令周

期。

特殊功能寄存器(包括I/O 口控制寄存器)可高速訪問。

應(yīng)用USB 向量中斷,具有極短的ISR 響應(yīng)時(shí)間。

只用作USB 事務(wù)管理,控制,不參與數(shù)據(jù)傳輸,較好地解決了

USB 高速模式的帶寬問題。

(3) “軟配置”——USB 固件可由USB 總線下載,片上不需集成ROM。

(4) 擁有四個(gè)FIFO 接口,可工作在內(nèi)部或外部時(shí)鐘下。端點(diǎn)和FIFO 接口

的應(yīng)用使外部邏輯和USB 總線可高速連接。

(5) 一種單片USB 2.0 外設(shè)解決方案,不需要外部的協(xié)議物理層,F(xiàn)X2 把所有的功能集成在一個(gè)芯片上。

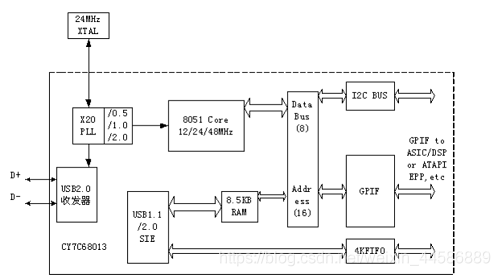

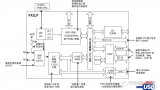

然后下面這幅圖片是FX2 控制器的內(nèi)部結(jié)構(gòu)圖(參照了小梅哥的圖片,在此安利一波小梅哥的FPGA,真的很好)。

對于FX2 來說,可以通過兩個(gè)不同的模式將 FX2 連接至 FPGA。這兩個(gè)模式分別為通用可編程接口( GPIF)模式和從設(shè)備 FIFO 模式。

(1)GPIF 模式:在該模式下, FX2 作為外部系統(tǒng)的主設(shè)備使用,它所生成的所有控制信號(hào)用于對外部系統(tǒng)進(jìn)行讀和寫操作。當(dāng)外部系統(tǒng)不能作為 FX2 的主設(shè)備(例如,圖像傳感器與 FX2 相連接的 USB 攝像機(jī)應(yīng)用)時(shí),通常優(yōu)先使用 GPIF 模式。在這種情況下,接口實(shí)現(xiàn)的復(fù)雜操作將由 FX2 執(zhí)行。

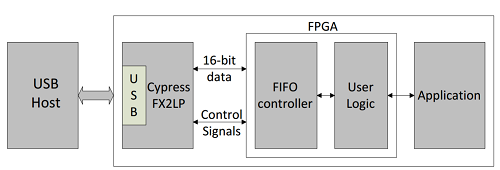

(2)從設(shè)備 FIFO 模式(通常所用的模式,注重了解):在該模式下,連接至 FX2 的外部系統(tǒng)能夠生成讀和寫控制信號(hào),因此,它能作為FX2 的主設(shè)備使用。在基于FPGA 的應(yīng)用中,F(xiàn)X2 一般被配置為從設(shè)備 FIFO 模式。下圖為FX2 使用從設(shè)備FIFO 接口與外部FPGA 連接時(shí)的系統(tǒng)框圖。

簡單地說,在從設(shè)備FIFO模式下,F(xiàn)X2 中的8051 固件只是配置Slave FIFO 相關(guān)的寄存器。配置完成之后FPGA就可以按照Slave FIFO 的時(shí)序與主機(jī)進(jìn)行通訊,通訊過程中不需要8051 固件。就相當(dāng)于FPGA控制一個(gè)外設(shè)(比如就像控制一個(gè)串口一樣簡單)

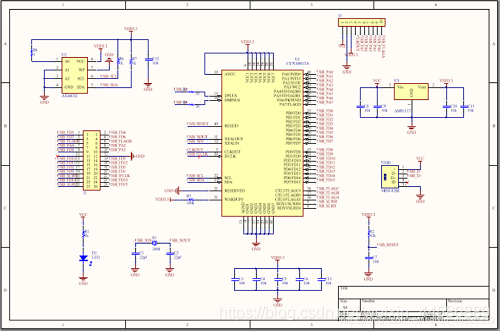

通訊原理搞明白之后就是根據(jù)引腳設(shè)計(jì)電路,原理圖如下圖所示:

2.下面就介紹如何具體控制USB2.0模塊了:

Cypress 提供了一個(gè)基本的開發(fā)工具包,供用戶開發(fā)USB 應(yīng)用,名為ySuiteUSB3.4,網(wǎng)上關(guān)于USB2.0開發(fā)的資料也有很多,包括安裝 FX2 的開發(fā)軟件以及安裝USB2.0模塊的驅(qū)動(dòng)程序,并且很重要的是在使用FPGA 控制USB2.0模塊之前要對 USB2.0 芯片燒寫固件(不同的應(yīng)用模式下,所燒寫的固件是不一樣的)。想要資料可以咨詢博主。

在配置完成之后可以通過官方網(wǎng)站提供的例程和上位機(jī)軟件,使用FX2 芯片上的8051 完成數(shù)據(jù)在OUT 和 IN 端點(diǎn)間的搬運(yùn)工作,在整個(gè)數(shù)據(jù)傳輸?shù)倪^程中不需要有外部的設(shè)備(FPGA和STM32等控制器),通過USB2.0模塊內(nèi)部就可以完成數(shù)據(jù)的傳輸。但是實(shí)際工程中往往是將下位機(jī)采集到的數(shù)據(jù)通過USB2.0模塊傳輸?shù)缴衔粰C(jī)中,所以只通過USB2.0模塊自身的數(shù)據(jù)回環(huán)實(shí)驗(yàn)是沒有多大意義的,所以接下來就介紹如何通過FPGA來控制數(shù)據(jù)的傳輸。

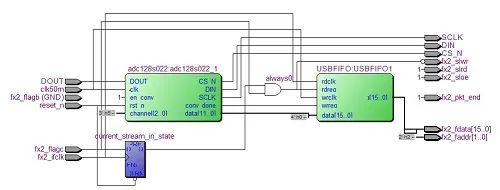

測試USB2.0模塊輔助了AD模塊(點(diǎn)擊這里),將AD模塊采集回來的數(shù)據(jù)通過FPGA送到USB2.0模塊上,然后USB2.0模塊將數(shù)據(jù)傳輸?shù)诫娔X上,完成數(shù)據(jù)的高速采集,如下圖所示是程序的RTL視圖,從RTL視圖可以直觀地看到USB2.0模塊的使用方法:

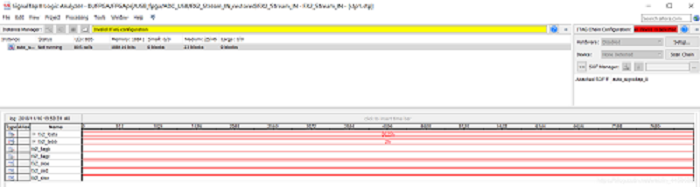

其中關(guān)于讀取USB2.0模塊的數(shù)據(jù)可以直接通過FPGA軟件中的Signal Tap II邏輯分析儀來進(jìn)行抓取,如圖所示:

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:怎樣通過FPGA軟件去讀取USB2.0模塊的數(shù)據(jù)

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603385

原文標(biāo)題:怎樣通過FPGA軟件去讀取USB2.0模塊的數(shù)據(jù)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

TUSB121x USB2.0電路板指南

ARK3399 USB2.0 PC攝像頭控制器規(guī)格書

德州儀器USB2.0設(shè)備用晶體的選擇和規(guī)格

FPGA + USB2.0 PHY USB3300 實(shí)現(xiàn)高速USB2UART

USB 2.0信號(hào)質(zhì)量測試

CYUSB3014是否會(huì)自動(dòng)調(diào)整工作模式USB3.0還是USB2.0?

請問ESP32-S3 USB HOST是否支持USB2.0?

FCX3 OV5640 usb2.0下添加1200*1200 15fps會(huì)出現(xiàn)空間不足錯(cuò)誤,如何解決?

Fcx3 usb2.0攝像頭分辨率問題求解

矽力杰USB2.0接口ESD保護(hù)方案

源碼系列:基于 FPGA 的 USB2.0 設(shè)計(jì)

USB2.0型號(hào)模擬轉(zhuǎn)換USB3.0輸出

stm32f302在調(diào)試USB的時(shí)候發(fā)現(xiàn)USB只支持USB2.0的高速設(shè)備,為什么?

基于FPGA技術(shù)的USB2.0接口設(shè)計(jì)實(shí)踐

怎樣通過FPGA軟件去讀取USB2.0模塊的數(shù)據(jù)

怎樣通過FPGA軟件去讀取USB2.0模塊的數(shù)據(jù)

評(píng)論