什么是RISC-V

大家聽過最多的處理器架構(gòu)可能就是x86和ARM,x86架構(gòu)主要用在PC端,ARM主要用在移動終端。學(xué)習(xí)嵌入式的小伙伴肯定都知道ARM,但是ARM是國外的,設(shè)計一款A(yù)RM架構(gòu)的芯片,需要經(jīng)過ARM公司的授權(quán),同時會產(chǎn)生一些費(fèi)用,這也帶來了一個問題:假如有一天ARM公司不授權(quán)怎么辦?

RISC-V架構(gòu)就是為了解決這個問題的!RISC-V最早在2010年起源于加州大學(xué)伯克利分校,由于受夠了現(xiàn)有處理器架構(gòu)的復(fù)雜性和相關(guān)知識產(chǎn)權(quán)的限制,伯克利大學(xué)決定發(fā)明一種全新的、簡單且開放免費(fèi)的指令集架構(gòu)。

從名字可以看出,RISC-V就是RISC的第五代指令集架構(gòu)。而RISC-V目標(biāo)就是“成為一種完全開放的指令集架構(gòu),可被任何學(xué)術(shù)機(jī)構(gòu)或商業(yè)組織自由使用”。

RISC-V指令集

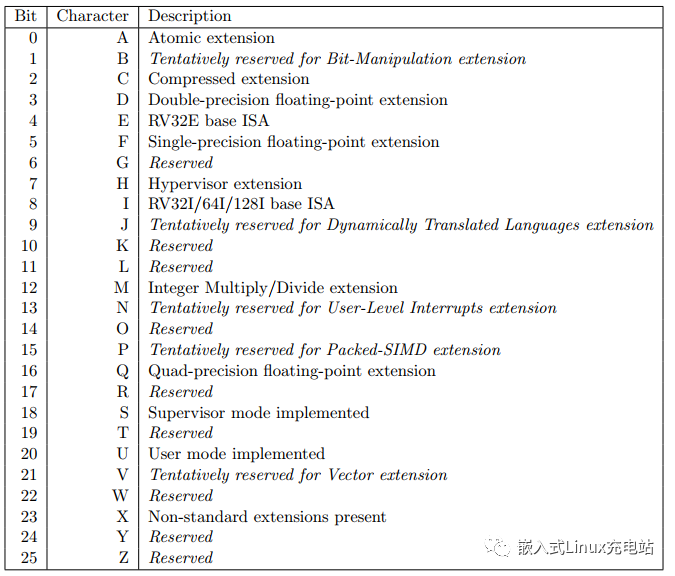

RISC-V指令集由“基本指令集 +擴(kuò)展指令集”組成。基本指令集是必選的,擴(kuò)展指令集是可選的。意思就是可以根據(jù)你的實際需求,選擇需要使用的指令。例如在一個項目中,如果不需要用到壓縮指令,那么就不需要把壓縮指令添加進(jìn)來,從而做到定制化,這也是RISC-V的一大特點。

RISC-V指令集有RV32I、RV32E、RV64I、RV64E、RV64I等等,RV代表RISC-V,32/64代表32位或64位,I和E都是基本指令集,在I和E的基礎(chǔ)上,可以添加D(雙精度浮點擴(kuò)展)、M(整數(shù)乘除法)、A(原子擴(kuò)展)、C(壓縮擴(kuò)展)等擴(kuò)展指令。例如,在RV64I基礎(chǔ)上,添加原子、整數(shù)乘除法、雙精度浮點、壓縮指令,則該指令集稱為RV64IMADC。

基本指令集和擴(kuò)展指令集描述如下:

-

內(nèi)核

+關(guān)注

關(guān)注

3文章

1374瀏覽量

40311 -

Linux

+關(guān)注

關(guān)注

87文章

11312瀏覽量

209738 -

指令

+關(guān)注

關(guān)注

1文章

607瀏覽量

35746 -

RISC

+關(guān)注

關(guān)注

6文章

462瀏覽量

83762 -

架構(gòu)

+關(guān)注

關(guān)注

1文章

515瀏覽量

25491

發(fā)布評論請先 登錄

相關(guān)推薦

正式的RISC-V基礎(chǔ)指令集架構(gòu)與特權(quán)架構(gòu)規(guī)范來了,RISC-V基金會已正式批準(zhǔn)

【RISC-V開放架構(gòu)設(shè)計之道|閱讀體驗】RISC-V基礎(chǔ)整數(shù)指令集

RISC-V基礎(chǔ)整數(shù)指令集

RISC-V指令集的特點總結(jié)

RISC-V和arm指令集的對比分析

RISC-V的指令集位寬的幾點學(xué)習(xí)心得

RISC-V指令集概述

RISC-V指令集架構(gòu)微控制器相關(guān)知識

印度確立RISC-V為國家指令集 中國CPU指令集還在孤芳自賞

RISC-V指令集的起源與發(fā)展歷史

risc-v中國峰會直播:如何優(yōu)化RISC-V指令集架構(gòu)的代碼密度?

簡單講講RISC-V指令集CPU的參數(shù)

risc-v是什么意思 指令集介紹

risc-v是什么意思 指令集介紹

評論