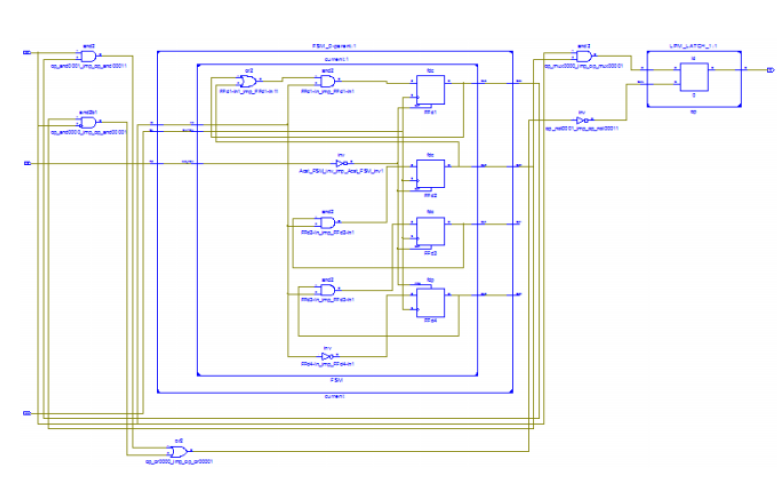

//有限狀態機分割設計,其實質就是一個狀態機分割成多個狀態機,或者說多個

//狀態機的協同設計來實現一個較為復雜的狀態跳轉設計,例如說玩游戲的一個

//狀態跳轉,玩家 A 操作的時候是一種狀態,玩家 B 操作的時候又是另外的一

//種狀態。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2018/11/02 10:14:11

// Design Name:

// Module Name: FSM_div

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module FSM_div(

clk, X, rst, Z,state1,state2

);

input clk, X, rst;

output Z;

parameter S0 = 2'b00, S1= 2'b01,

S2 = 2'b10,SA = 2'b11, S3 = 2'b00, S4 = 2'b01,

S5 = 2'b10,SB = 2'b11;

output reg [1:0] state1,state2;

reg [1:0] next_state1,next_state2;

always @( posedge clk )begin

if(rst) begin

state1 <= S0;state2<=SB;end

else begin

state1 <= next_state1;

state2 <= next_state2;end

end

always @(state1 or X) begin

case(state1)

S0:begin if(X) next_state1<=S1;

else next_state1<=S0;end

S1:begin if(X) next_state1<=S1;

else next_state1<=S2;end

S2:begin if(X) next_state1<=S1;

else next_state1<=SA;end

SA:begin if(X)

begin

if(state2==S4 || state2==S5)

next_state1<=S1;

else next_state1<=SA;

end

else if(state2==S3)

next_state1<=S0;

else next_state1<=SA;

end

endcase

end

always @(state1 or state2 or X) begin

case(state2)

S3:begin if(X) next_state2<=S4;

else next_state2<=SB;end

S4:begin if(X) next_state2<=SB;

else next_state2<=S5;end

S5:begin if(X) next_state2<=SB;

else next_state2<=S3;end

SB:begin if(!X)

begin

if(state1==S2)

next_state2<=S3;

else next_state2<=SB;end

else next_state2<=SB;

end

endcase

end

assign Z = (state2 == S5)?1:0;

endmodule

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

有限狀態機

+關注

關注

0文章

52瀏覽量

10327 -

狀態機

+關注

關注

2文章

492瀏覽量

27539 -

fsm

+關注

關注

0文章

35瀏覽量

12824 -

CLK

+關注

關注

0文章

127瀏覽量

17169

發布評論請先 登錄

相關推薦

什么是有限狀態機呢

在嵌入式,機器人領域,由于多的復雜邏輯狀態,我們編寫程序的時候不得不考慮很多種情況,容易造成功能間的沖突。有限狀態機(finite-state machine),簡稱狀態機,是一種表示有限

發表于 12-20 06:51

fsm有限狀態機pdf

利用 VHDL 設計的許多實用邏輯系統中,有許多是可以利用有限狀態機的設計方案來描述和實現的。無論與基于 VHDL的其它設計方案相比,還是與可完成相似功能的 CPU 相比,狀

發表于 06-04 10:33

?75次下載

有限狀態機的建模與優化設計

本文提出一種優秀 、高效的 Verilog HDL 描述方式來進行有限狀態機設計 介紹了 有限狀態機的建模原則 并通過一個可綜合的實例 驗證了 該方法設計的有限狀態機在面積和功耗上的優勢。

發表于 03-22 15:19

?1次下載

VHDL有限狀態機設計-ST

EDA的有限狀態機,廣義而言是指只要涉及觸發器的電路,無論電路大小都可以歸結為狀態機。有限狀態機設計在學習EDA時是很重要的一章。

發表于 06-08 16:46

?3次下載

初學者對有限狀態機(FSM)的設計的認識

有限狀態機(FSM)是一種常見的電路,由時序電路和組合電路組成。設計有限狀態機的第一步是確定采用Moore狀態機還是采用Mealy狀態機。

發表于 02-11 13:51

?4304次閱讀

如何使用FPGA實現序列檢測有限狀態機

有限狀態機是絕大部分控制電路的核心結構, 是表示有限個狀態以及在這些狀態之間轉移和動作等行為的數學模型。有限狀態機是指輸出取決于過去輸入部分

發表于 11-04 17:17

?12次下載

基于事件驅動的有限狀態機介紹

? 一、介紹 EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計原則是:簡單

基于事件驅動的有限狀態機介紹

EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。

一個基于事件驅動的有限狀態機

EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計原則是:簡單!EFSM的使用者只需要關心:

有限狀態機分割設計

有限狀態機分割設計

評論