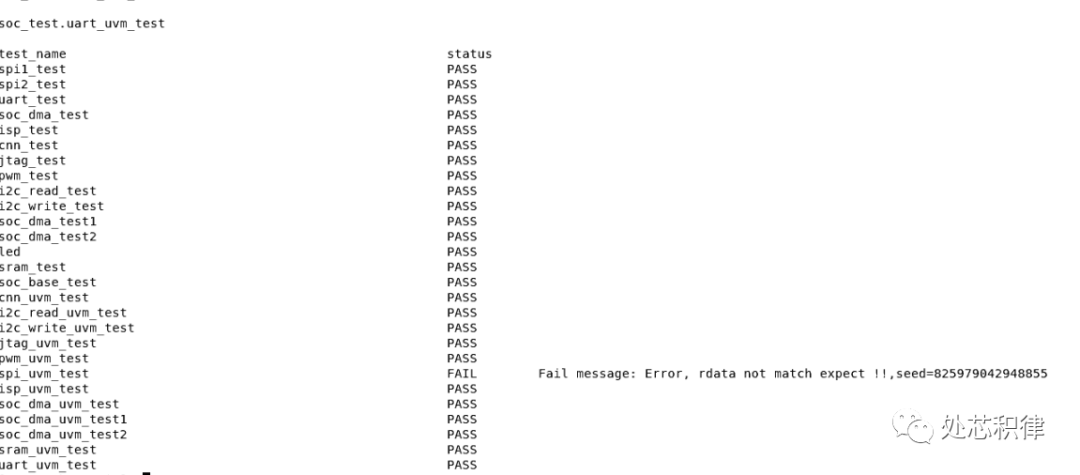

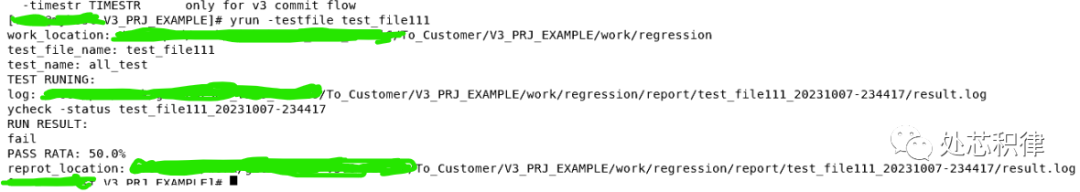

yrun是處芯積律自研的regression腳本,yrun都有哪些東西呢?

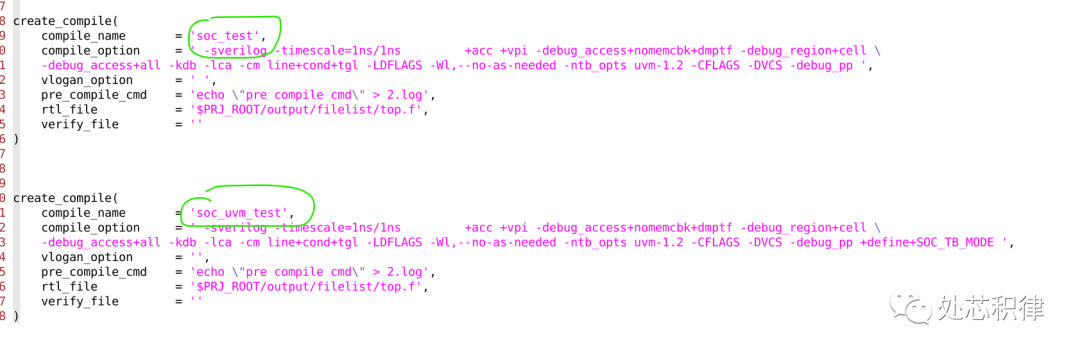

1.通過 cmpfile 將不同版本的compile需求集中管理

2. 通過 testfile 將test集中起來管理。

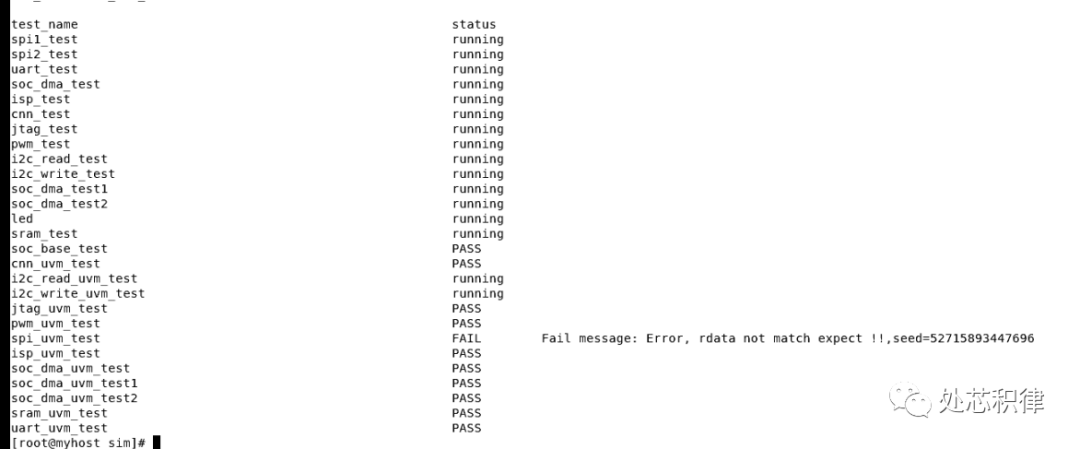

3.可以通過 yrun 跑 testfile里面的test 的regression

yrun -testfile soc_test

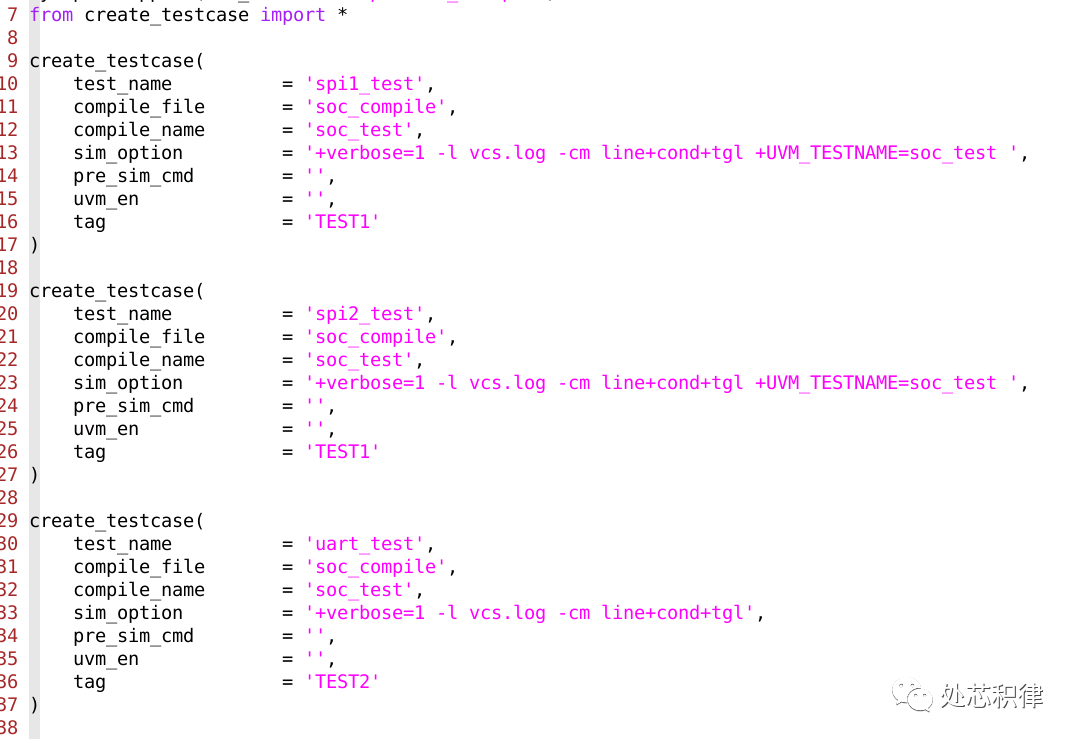

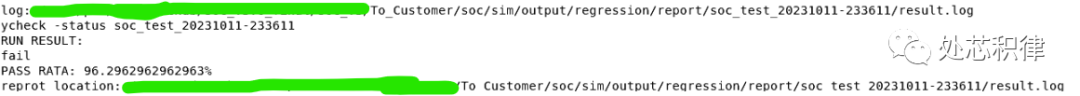

4. 可以通過ycheck 檢查 歷史regression的狀態

中間狀態

跑完狀態

更多內容!請看下面項目介紹

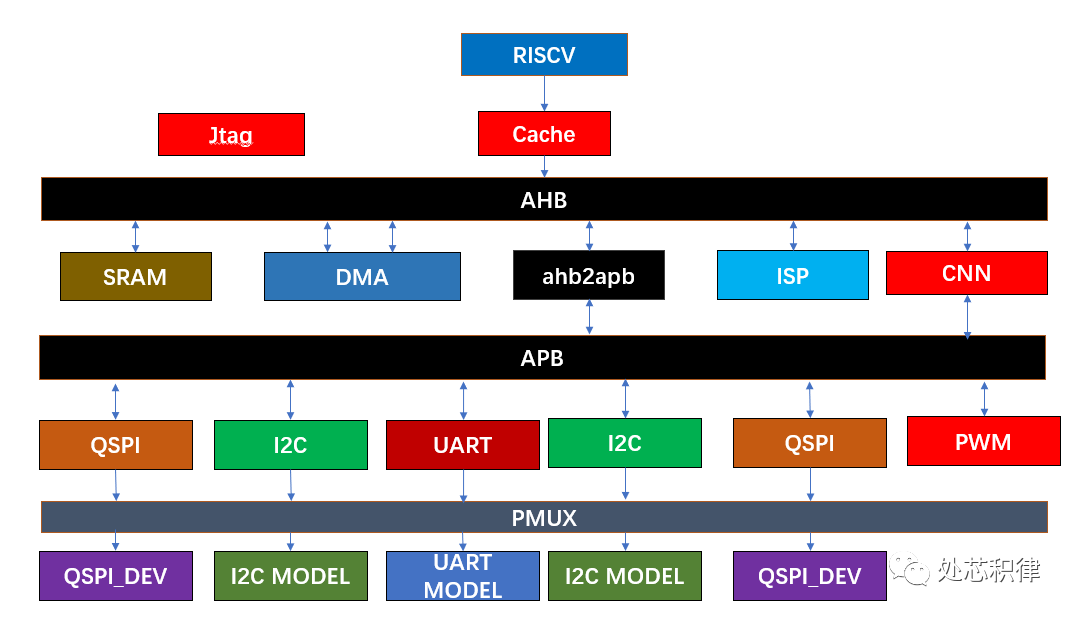

SOC3.0 項目都有哪些東西:

模塊升級

SOC V3.0在2.0項目的基礎上增加了Jtag、iCache、CNN 和PWM模塊。

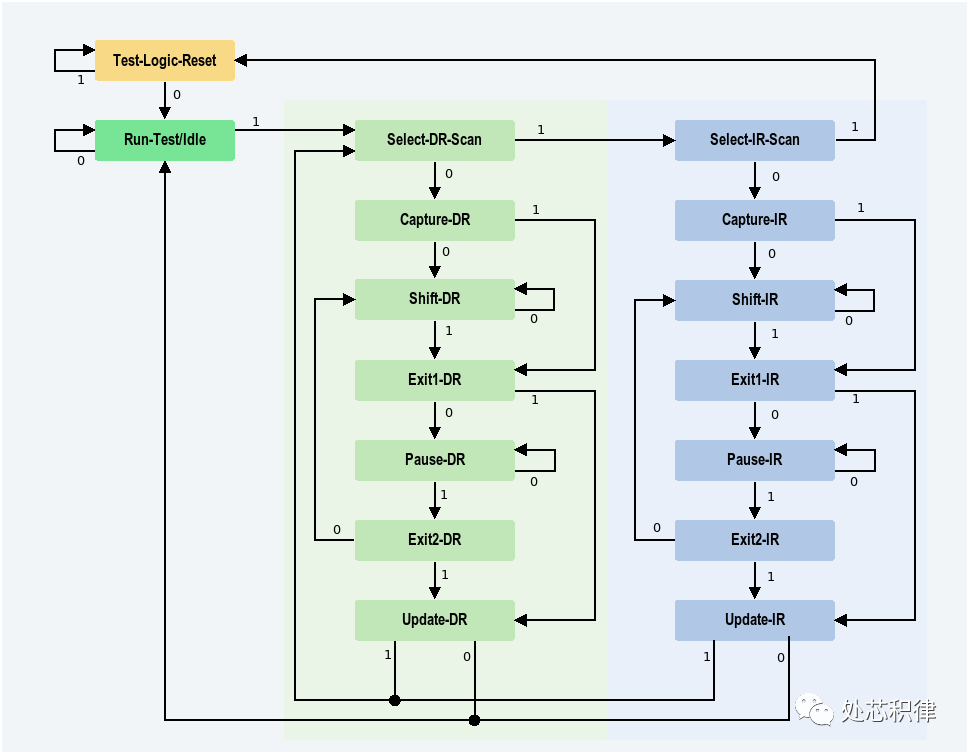

Jtag:

Jtag是聯合測試工作組(Joint Test Action Group)的簡稱,目前最主要用在集成電路的測試,也可以通過JTAG結合DM(Debug Module) 實現芯片的調試,為軟件開發者提供了一個芯片內部的后門。

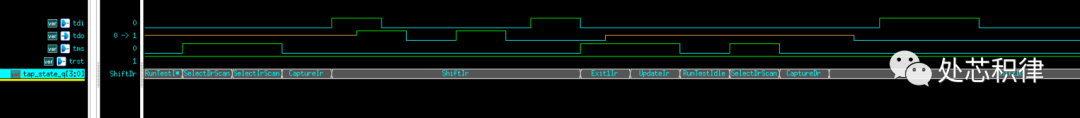

Jtag 狀態機

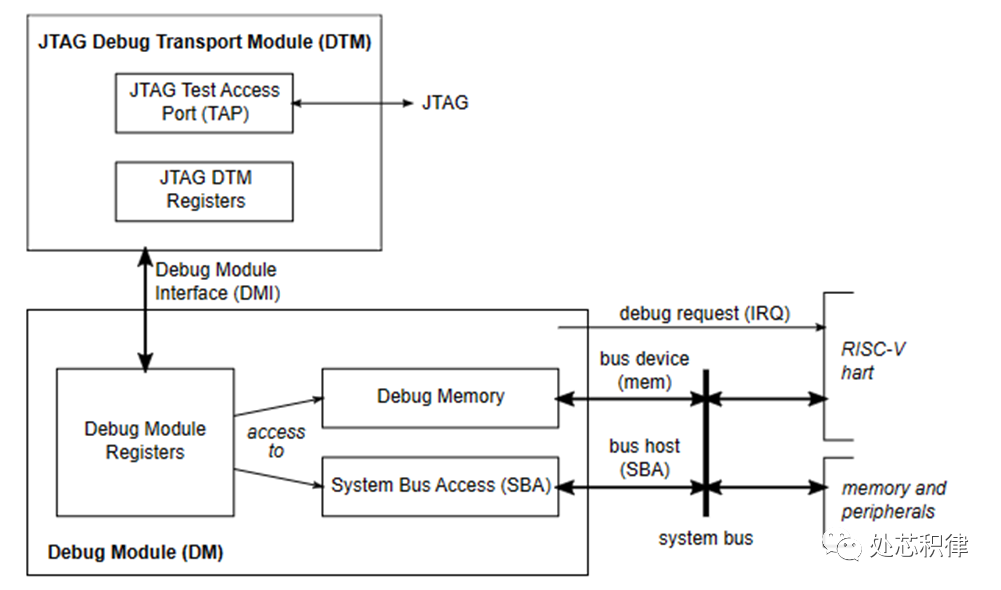

DM(Debug module):

DM 稱為調試模塊,該電路集成在芯片內部,方便開發者編程、調試、異常處理等功能,已經是芯片不可或缺的電路。

下圖是RISCV的debug module。

上述JTAG和DM在我們SOC V3.0里面已經集成。

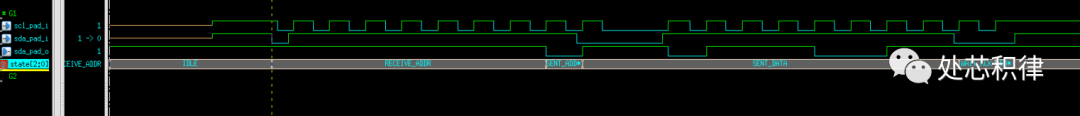

以下是我們在環境中跑的test的部分波形:

CNN:

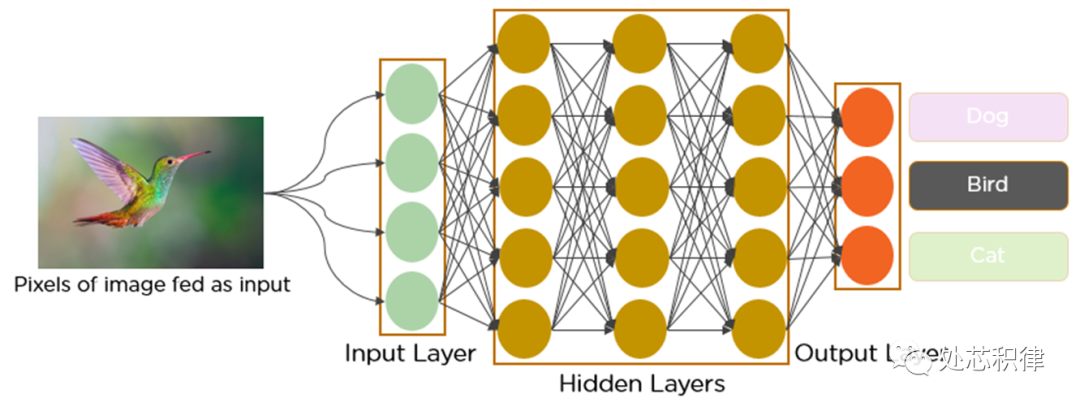

CNN是Convolutional neural network (CNN)的簡稱,在圖像識別、語音識別、大語言模型中廣泛的使用。

CNN的應用

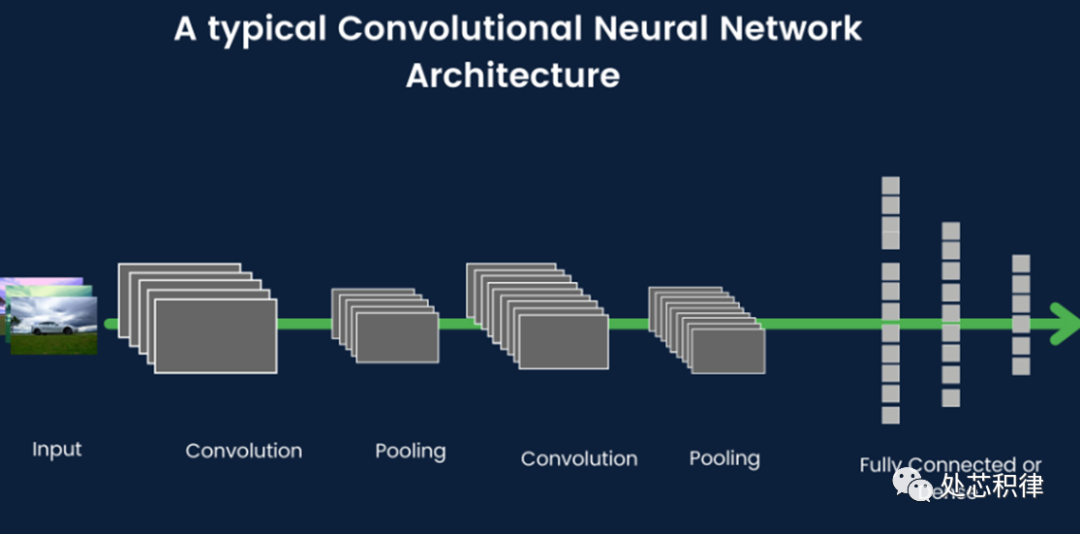

典型的CNN結構由卷積層、池化層、連接層組成。

典型的CNN網絡

在我們的SOC V3.0里面,我們集成了一個簡單的CNN網絡。

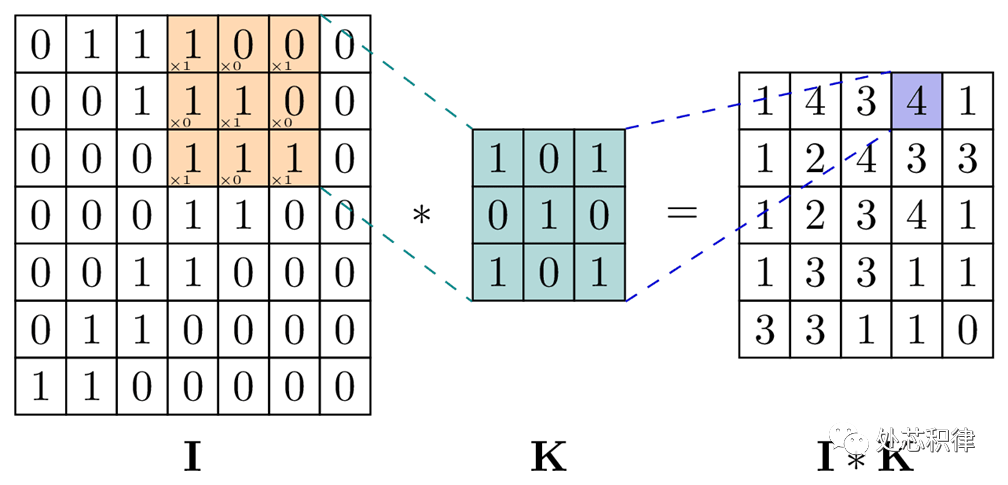

其中包含卷積運算、池化運算、線性運算。

卷積運算

PWM:

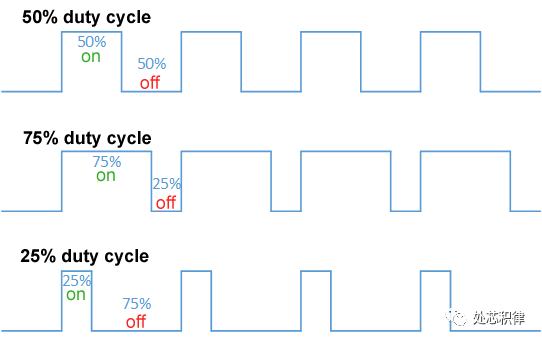

PWM是Pulse Width Modulation的簡稱,在燈光調節、電機控制等各個領域有廣泛的應用。

PWM控制不同占空比

在我們SOC V3.0中,我們集成了PWM模塊。

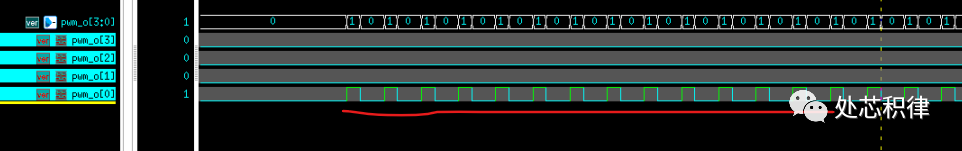

下面是我們PWM模塊跑出來的波形。

工具升級

在SOC V3.0的環境上,我們研發了yrun 、ycheck、ygpt 等腳本工具。

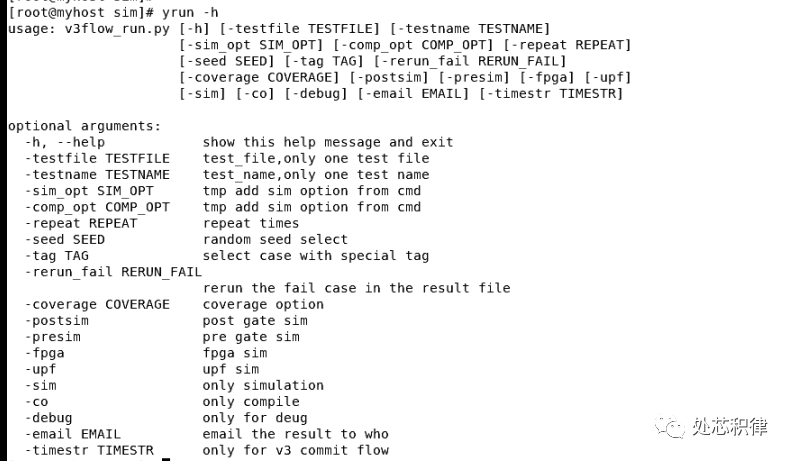

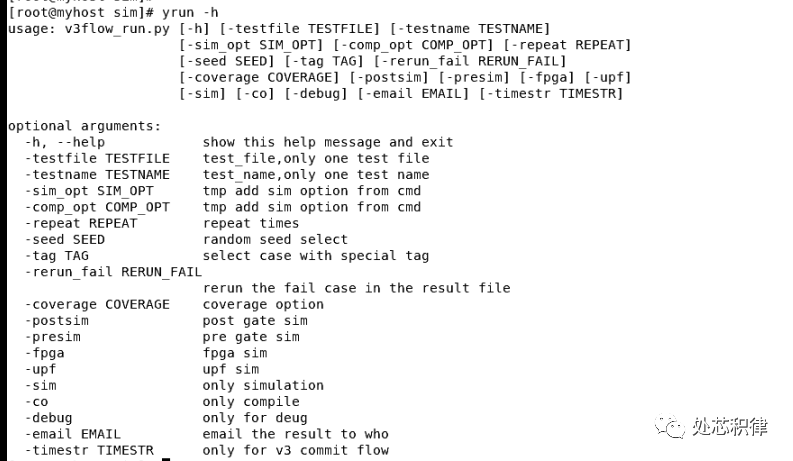

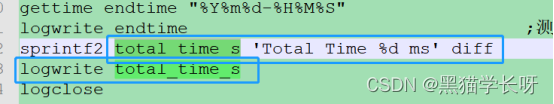

yrun:

yrun支持跑編譯、仿真、回歸等多個功能。

?

?

詳細功能介紹:

簡潔的test 添加機制;

simulation和compile 分開管理;

支持只編譯模式;

支持只simulation模式;

支持特定的 test list的 regression;

支持同時跑不同的regression;

支持 simulation 進行時在終端上打印log;

支持simulation 在后臺運行;

支持特定 test list 中 特定test的 simulation;

支持 fail test的rerun機制;

支持中間查看特定regression的運行狀態;

支持將regression的結果通過mail的方式發給指定的用戶;

支持將regression的fail test的error 顯示在regression的結果中;

支持用戶定義FPGA simulation,Gate lever simulation,UPF simulation等。

在SOC V3.0里面,我們提供了yrun使用的demo,用戶可以根據自己的需要將yrun應用到自己的IP和SOC驗證環境中。

注意!!! 在我們提供的demo里面,yrun的源代碼是提供給大家的。SOC V3.0驗證環境里面的yrun由于做了更多的開發,我們對部分代碼進行了加密處理。

ycheck: ycheck 是用于檢查regression的狀態使用。

使用方法如下:

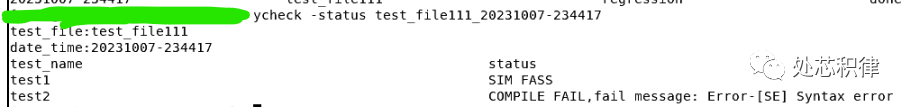

ygpt: ygpt是將GPT引入到芯片的研發中,通過GPT讀取代碼,用戶可以根據自己需求向GPT獲取信息。例如:制定 testplan,寫 testbench 等等。

下面是ygpt 使用的案例:

驗證環境升級

目前我們SOC V3.0 包含了 :

基于UVM的IP驗證方法學

基于C的SOC驗證方法學

基于UVM的SOC驗證方法學

基于Formal的驗證方法學

下面我們詳細介紹: 基于UVM的IP驗證方法學 在我們日常的IP驗證中,IP分為10大類,他們是:

通信IP:如USB、Ethernet、PCI Express等。

存儲IP:如存儲控制器、閃存控制器等。

數字信號處理IP:如圖像處理等。

模擬IP:如模擬-數字轉換器(ADC)和數字-模擬轉換器(DAC)等。

安全IP:如加密引擎、隨機數生成器等。

時鐘IP:包括時鐘生成器和分配網絡,用于同步和時序控制。

外設IP:包括各種外設,如UART、SPI、I2C等,用于與其他設備進行通信。

自定義IP:一些芯片制造商或設計團隊可能會開發自定義的IP。

在這些IP里面,我們根據驗證采用的不同策略可以將其歸為四大類:

第一類 : 協議類IP,如USB,UART,時鐘IP等;

第二類 : 算法類IP,如ISP,CNN等;

第三類 : 處理器IP,如CPU,GPU等;

第四類 : 模擬IP,如ADC,DAC等。

在我們SOC V3.0 項目中,我們開發了協議類IP的驗證環境和算法類IP的驗證環境。

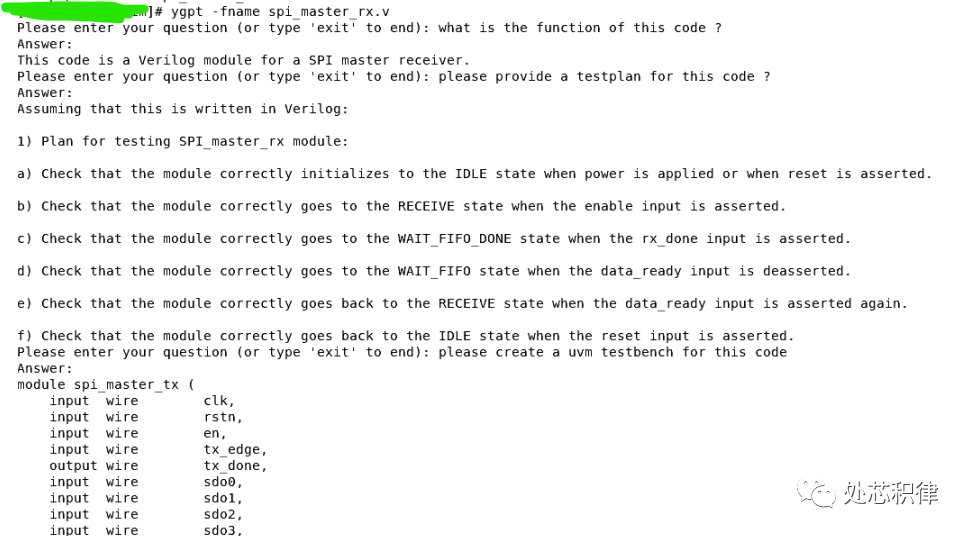

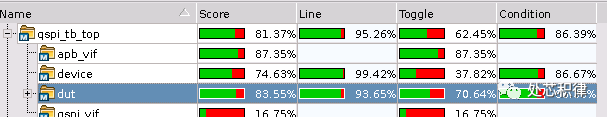

協議類IP 驗證環境—QSPI

QSPI 采用UVM驗證即可,其驗證框架如下

QSPI驗證環境

QSPI 驗證環境包括APB Agent,Register Model,Register Adapter, QSPI Scoreboard,QSPI Monitor,Sequencer 等。

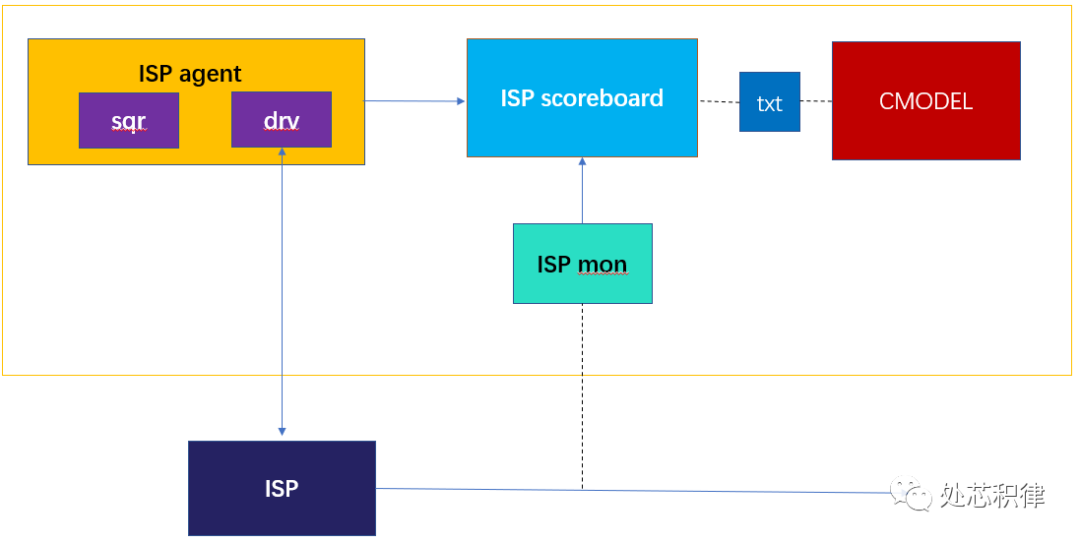

算法類IP 驗證環境—ISP

ISP 采用UVM+C的驗證方式,UVM和C的交互有多種方式,在ISP環境中,我們選擇將C編譯成可執行文件,然后通過UVM環境調用可執行文件生成帶有預期的數據的txt文件,UVM 環境通過讀取預期數據的txt文件與觀測到值進行比對,從而判斷設計的正確性。

ISP驗證環境

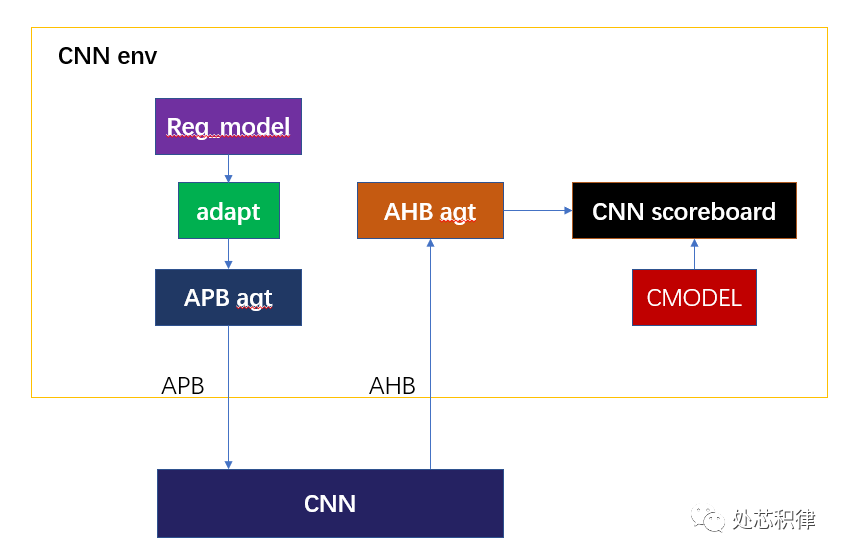

算法類IP 驗證環境—CNN

CNN也是采用UVM+C的驗證方式,不同于ISP,在CNN環境中,我們采用DPI的方式調用C文件,scorboard在拿到觀測數據之后,直接通過DPI 調用 C函數獲取預期的值。

CNN驗證環境

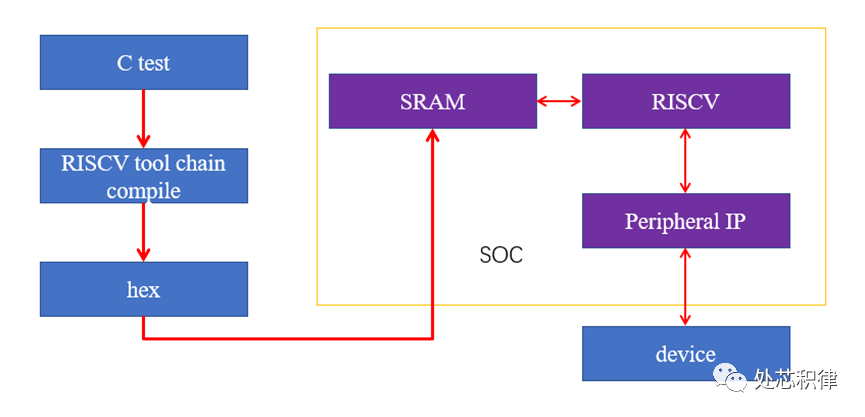

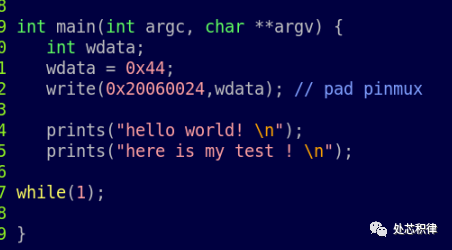

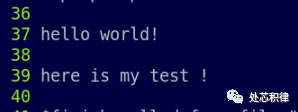

基于C的SOC驗證方法學

SOC環境集成了CPU,為了讓CPU能夠跑起來,一個簡單的做法是讓CPU直接吃指令執行,但是純粹的機器指令可讀性很差。采用C寫test,然后用工具鏈編譯成機器指令給CPU執行是一種常規的操作。 在SOC V3.0中,我們提供基于C的SOC驗證環境。

基于C的SOC驗證環境 我們提供了包括UART,I2C,SPI,CNN,ISP在內的諸多IP的C test。用戶可以通過仿真了解C的編譯和執行過程,對芯片的運行有個更加系統的理解。

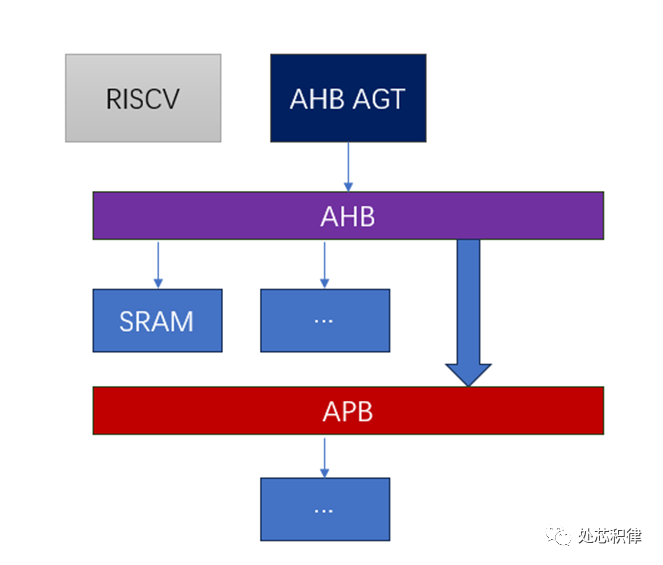

基于UVM的SOC驗證方法學

在SOC環境中,采用C生成機器碼讓CPU執行的過程會占用大量的仿真時間,特別是一些復雜的大芯片,另外考慮到IP驗證環境開發過類似的test,很多公司希望在SOC環境中能夠復用這些test,那么一套基于UVM的SOC驗證環境就非常有必要。

在我們SOC V3.0環境中,我們集成了基于UVM的SOC驗證環境,用戶在拿到我們代碼后,可以通過仿真了解了UVM是和如何SOC協同完成SOC驗證。

基于UVM的SOC驗證環境

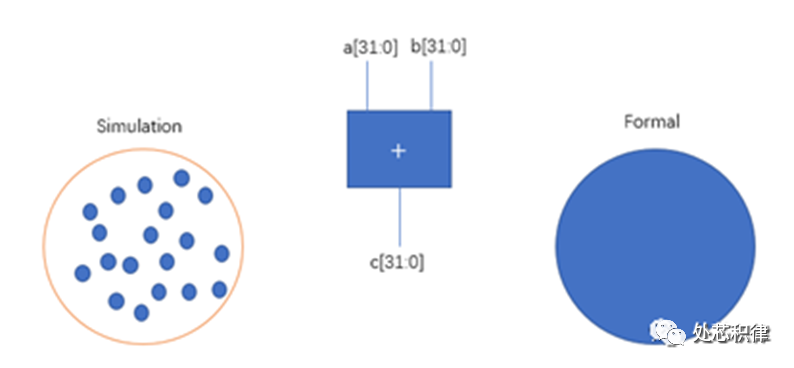

基于Formal的驗證方法學

采用simulation 只能打到部分的場景,這個過程不免有些bug遺漏。基于數學推算的Formal 可以完美的解決這個問題。  ? ?

? ?

在我們SOC V3.0中我們集成了一個基本的Formal驗證環境,方便大家理解Formal驗證的思想。

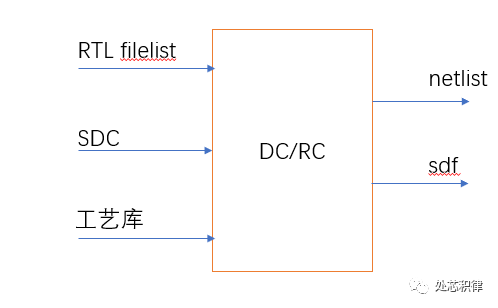

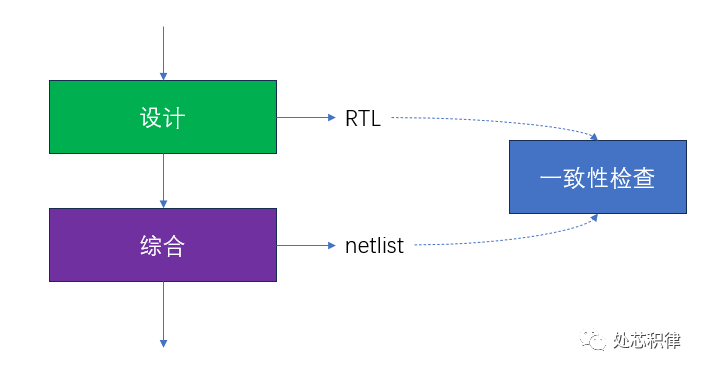

完善設計流程

芯片的前端設計涉及到語法檢查,綜合以及形式驗證。在SOC V3.0 里面,我們提供了語法檢查,綜合以及形式驗證的腳本及相關的工藝庫文件。

綜合過程

形式驗證

我們還做了哪些事情?

除上述之外,我們還在SOC V3.0中集成了SOC V1.1的改動:

補全了I2C_DEV 和UART_DEV;

2. 實現C代碼中字符串打印;

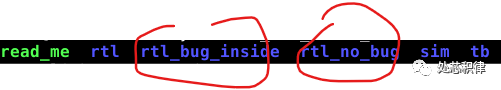

3. 完善的QSPI驗證計劃,驗證用例和coverage數據;

4. 提供了QSPI 和CNN的問題代碼,讓大家在debug中理解項目。

審核編輯:劉清

-

集成電路

+關注

關注

5388文章

11562瀏覽量

362018 -

PWM

+關注

關注

114文章

5190瀏覽量

214129 -

soc

+關注

關注

38文章

4173瀏覽量

218404 -

JTAG

+關注

關注

6文章

400瀏覽量

71707 -

狀態機

+關注

關注

2文章

492瀏覽量

27554 -

jtag接口

+關注

關注

0文章

34瀏覽量

13662 -

PWM模塊

+關注

關注

0文章

14瀏覽量

9438

原文標題:SOC3.0 regression腳本 yrun 有哪些東西?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

logistic regression代碼與調用sklearn庫中的logistic regression代碼

Multivariate Linear Regression多變量線性回歸

BI軟件的ETL用開源的好,還是自研的好?

蘋果自研射頻芯片?OPPO自研NPU芯片!芯片的國產替代需要跨越三個誤區!

繼蘋果使用自研ARM架構處理器后,三星將在電腦采用ARM自研芯片

OPPO放棄自研芯片,終止哲庫業務

自研MACSec與88E1548P對通測試

為什么要學習TTL腳本

自研的regression腳本yrun都有哪些東西呢?

自研的regression腳本yrun都有哪些東西呢?

評論