現(xiàn)在生成式人工智能已經(jīng)引爆新的智能革命發(fā)展的浪潮,計(jì)算能力支撐下的人工智能技術(shù)是人類的生產(chǎn)和生活方式改變著隨之而來(lái)的需求大量的計(jì)算能力,龐大的計(jì)算能力不足問(wèn)題如何解決,實(shí)現(xiàn)能源效率大幅提升,變得越來(lái)越迫切。

最近,清華大學(xué)教授吳華強(qiáng)和副教授高斌基于一體化存儲(chǔ)計(jì)算范例,在存儲(chǔ)存儲(chǔ)一體化芯片領(lǐng)域取得重大突破。《科學(xué)》(science)以《edge learning using a fully integrated neuro-inspired memristor chip》為題,在權(quán)威學(xué)術(shù)雜志《科學(xué)》(Science)上在線發(fā)表。

據(jù)介紹,記憶電阻器是繼電阻、電容器、感應(yīng)之后的第四電路的基本部件。即使斷電也能記錄通過(guò)的電荷,因此被稱為新的納米電子突觸零件。

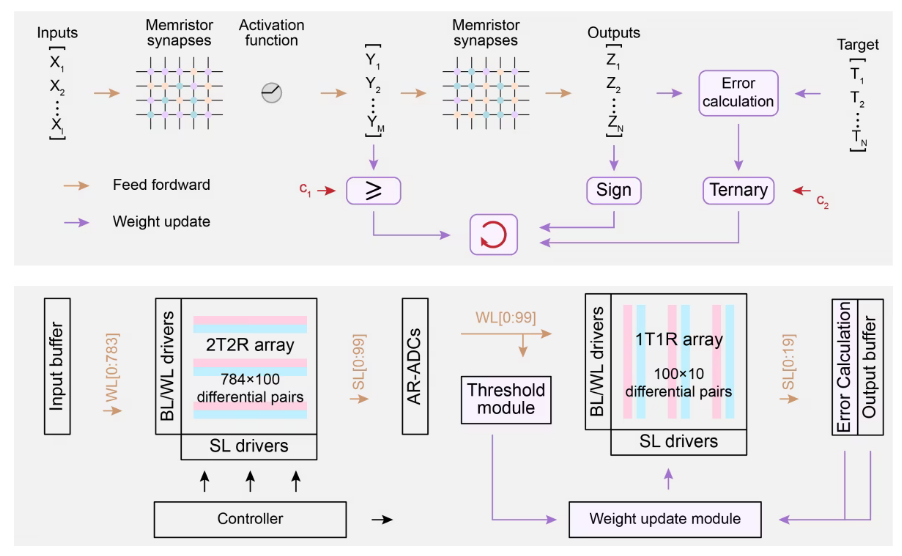

憶阻器存算一體技術(shù)從底層器件,配件、電路結(jié)構(gòu)計(jì)算和理論全面計(jì)算,傳統(tǒng)計(jì)算架構(gòu),馮諾伊曼是計(jì)算能力和提高能源效率的跨越式技術(shù)還能夠?qū)崿F(xiàn)終端設(shè)備可以利用的學(xué)習(xí)特點(diǎn),支持實(shí)時(shí)片上學(xué)習(xí),陪可以以地區(qū)為基礎(chǔ)的學(xué)習(xí)訓(xùn)練的邊緣新場(chǎng)景。

然而實(shí)現(xiàn)全系統(tǒng)集成的、支持高效片上學(xué)習(xí)的憶阻器芯片仍面臨較大挑戰(zhàn),至今還未實(shí)現(xiàn)的原因主要是傳統(tǒng)的逆轉(zhuǎn)宋訓(xùn)練算法所要求的高精權(quán)重更新方式和在利斯特的實(shí)際特性之間的兼容性比較不好的緣故。

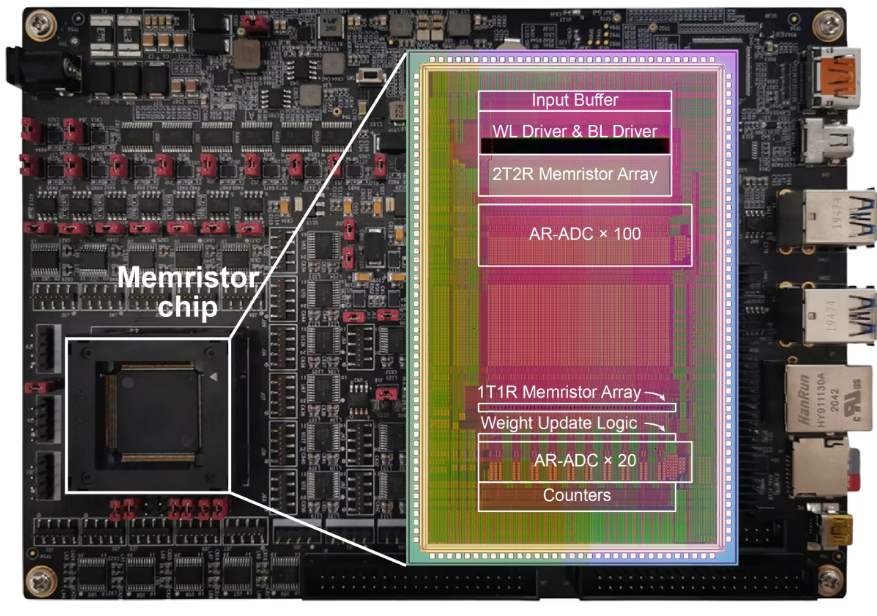

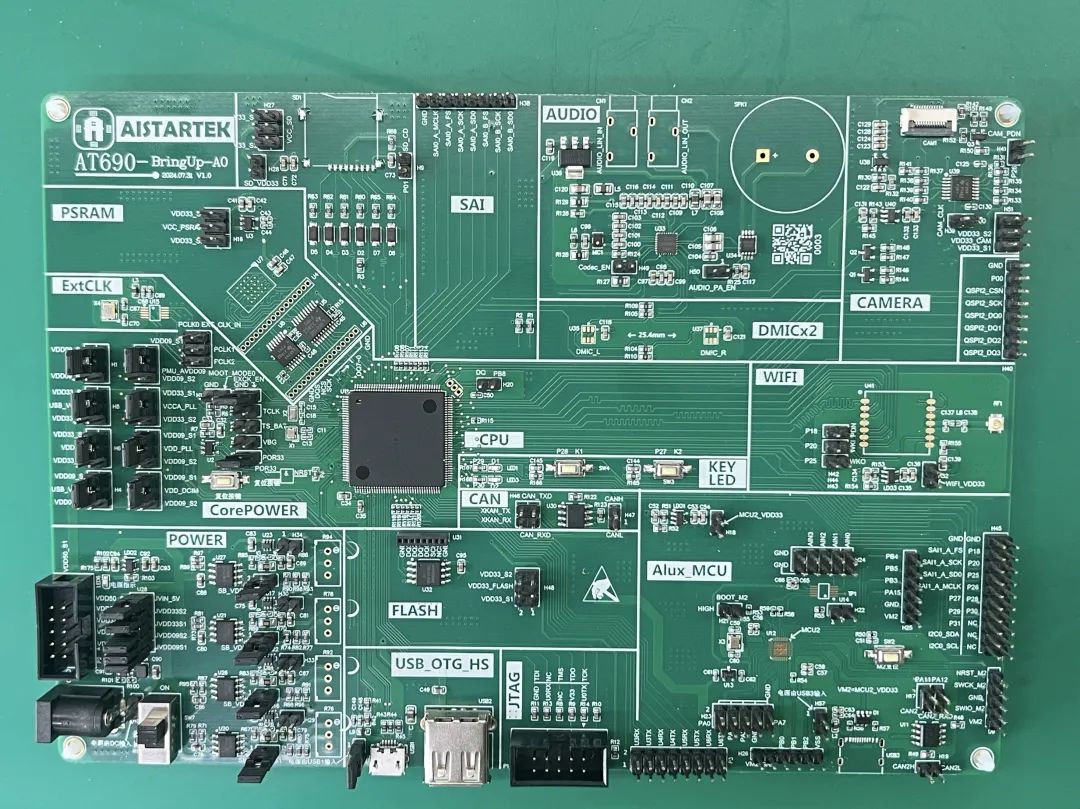

為解決上述挑戰(zhàn),該研究團(tuán)隊(duì)基于存算一體計(jì)算范式,創(chuàng)造性提出適配憶阻器存算一體實(shí)現(xiàn)高效片上學(xué)習(xí)的新型通用算法和架構(gòu)(STELLAR),大規(guī)模堵排列和模擬型憶的有效實(shí)現(xiàn)cmos外知道三維集成、算法、結(jié)構(gòu)通過(guò)整合方式的全過(guò)程協(xié)同創(chuàng)新,世界上最早研制出全系統(tǒng)集成,支持高效芯片學(xué)習(xí)的內(nèi)存集成芯片。

這個(gè)芯片是學(xué)習(xí)芯片所需的所有電路模塊,圖像分類,包括語(yǔ)音識(shí)別和控制等多種任務(wù)的芯片增量學(xué)習(xí)功能的驗(yàn)證,成功地完成了工作,高適應(yīng)性、高能源效率高的普遍性,展現(xiàn)出較高的準(zhǔn)確度等特點(diǎn)。

同時(shí),芯片具有能效的優(yōu)點(diǎn),在相同的作業(yè)中,芯片僅達(dá)到尖端技術(shù)專用集成電路(asic)系統(tǒng)能耗的3%,能效的瓶頸現(xiàn)象為馮·諾依曼傳統(tǒng)計(jì)算架構(gòu)提供了突破的新途徑

-

憶阻器

+關(guān)注

關(guān)注

8文章

73瀏覽量

19875 -

架構(gòu)

+關(guān)注

關(guān)注

1文章

515瀏覽量

25491 -

存算一體

+關(guān)注

關(guān)注

0文章

102瀏覽量

4308

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

直播預(yù)約 |開源芯片系列講座第24期:SRAM存算一體:賦能高能效RISC-V計(jì)算

存算一體化與邊緣計(jì)算:重新定義智能計(jì)算的未來(lái)

存算一體架構(gòu)創(chuàng)新助力國(guó)產(chǎn)大算力AI芯片騰飛

科技新突破:首款支持多模態(tài)存算一體AI芯片成功問(wèn)世

后摩智能首款存算一體智駕芯片獲評(píng)突出創(chuàng)新產(chǎn)品獎(jiǎng)

后摩智能推出邊端大模型AI芯片M30,展現(xiàn)出存算一體架構(gòu)優(yōu)勢(shì)

知存科技助力AI應(yīng)用落地:WTMDK2101-ZT1評(píng)估板實(shí)地評(píng)測(cè)與性能揭秘

探索存內(nèi)計(jì)算—基于 SRAM 的存內(nèi)計(jì)算與基于 MRAM 的存算一體的探究

我們?cè)跍y(cè)試憶阻器時(shí)到底在測(cè)試什么?#憶阻器 #類腦計(jì)算 #存算一體 #芯片 #GPU

知存科技攜手北大共建存算一體化技術(shù)實(shí)驗(yàn)室,推動(dòng)AI創(chuàng)新

憶阻器通向計(jì)算新未來(lái),自旋憶阻器進(jìn)一步降低能耗

英特爾最大神經(jīng)形態(tài)計(jì)算機(jī)研制成功

聚焦全國(guó)一體化算力體系構(gòu)建,憶聯(lián)以強(qiáng)大存力“引擎”釋放算力潛能

中國(guó)移動(dòng)近日正式推出全球首臺(tái)算力路由器—CATS Router

什么是通感算一體化?通感算一體化的應(yīng)用場(chǎng)景

清華團(tuán)隊(duì)研制成功,全球首顆支持片上學(xué)習(xí)憶阻器存算一體芯片

清華團(tuán)隊(duì)研制成功,全球首顆支持片上學(xué)習(xí)憶阻器存算一體芯片

評(píng)論