1.為什要區分AGND和DGND?

目前的信號處理系統一般需要混合信號器件,例如模數轉換器 (ADC)、數模轉換器 (DAC)和快速數字信號處理器 (DSP)。由于需要處理寬動態范圍的模擬信號,因此擁有高性能ADC 和 DAC 顯得更加重要。在惡劣的數字環境內,能否保持寬動態范圍和低噪聲與采用良好的高速電路設計技術密切相關,包括適當的信號路由、去耦和接地。

過去,一般認為“高精度、低速”電路與所謂的“高速”電路有所不同。對于 ADC 和DAC,采樣頻率一般用作區分速度標準。不過,以下兩個示例顯示,實際操作中,目前大多數信號處理 IC 真正實現了“高速”,因此必須作為此類器件來對待,才能保持高性能。DSP、ADC 和 DAC 均是如此。

所有適合信號處理應用的采樣 ADC(內置采樣保持電路的 ADC)均采用具有快速上升和下降時間(一般為數納秒)的高速時鐘工作,即使吞吐量看似較低也必須視為高速器件。例如,中速 12 位逐次逼近型 (SAR) ADC 可采用 10 MHz 內部時鐘工作,而采樣速率僅為500 kSPS。

Σ-Δ 型 ADC 具有高過采樣比,因此還需要高速時鐘。即使是高分辨率、所謂的“低頻”Σ-Δ工業測量 ADC(吞吐速率 10 Hz 至 7.5 kHz)也采用 5 MHz 或更高時鐘工作,并且提供高達 24 位的分辨率(例如 ADI 公司的 AD77xx 系列)。

更復雜的是,混合信號 IC 具有模擬和數字兩種端口,因此如何使用適當的接地技術就更加茫然。此外,某些混合信號 IC 具有相對較低的數字電流,而另一些具有高數字電流。許多情況下,兩種類型必須區分對待,才能實現最佳接地。

數字和模擬設計工程師傾向于從不同角度考察混合信號器件,本教程旨在確立適用于大多數混合信號器件的一般接地原則,而不必了解內部電路的具體細節。

2.接地層電源層

保持低阻抗大面積接地層對目前所有的模擬和數字電路都很重要。接地層不僅用作去耦高頻電流(源于快速數字邏輯)的低阻抗返回路徑,還能將 EMI/RFI 輻射降至最低。由于接地層的屏蔽作用,電路受外部 EMI/RFI 的影響也會降低。

接地層還允許使用傳輸線路技術(微帶線或帶狀線)傳輸高速數字或模擬信號,此類技術需要可控阻抗。

由于“母線 (buss wire)”在大多數邏輯轉換等效頻率下具有阻抗,將其用作“地”完全不能接受。例如,#22 標準導線具有約 20 nH/ 英寸的電感。由邏輯信號產生的壓擺率為 10mA/ns 的瞬態電流,在此頻率下流經 1 英寸該導線將形成 200 mV 的無用壓降 :

對于具有 2 V 峰峰值范圍的信號,此壓降會轉化為約 10% 的誤差(大約 3.5 位精度)。即使在全數字電路中,該誤差也會大幅降低邏輯噪聲裕量。

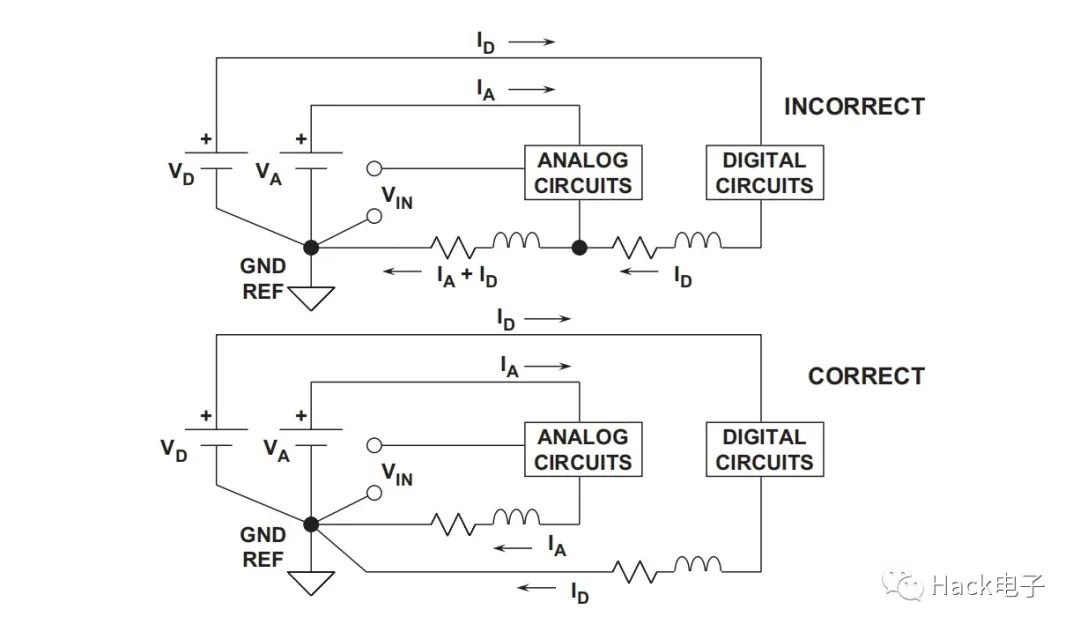

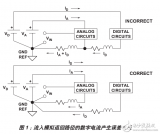

圖 1 為數字返回電流調制模擬返回電流的典型情況(頂圖)。接地返回導線電感和電阻由模擬和數字電路共享,這會造成相互影響,最終產生誤差。一個可能的解決方案是讓數字返回電流路徑直接流向 GND REF,如底圖所示。這就是“星型”或單點接地系統的基本概念。在包含多個高頻返回路徑的系統中很難實現真正的單點接地,因為各返回電流導線的物理長度將引入寄生電阻和電感,所以獲得低阻抗高頻接地就很困難。實際操作中,電流回路必須由大面積接地層組成,以便實現高頻電流下的低阻抗。如果無低阻抗接地層,則幾乎不可能避免上述共享阻抗,特別是在高頻下。

圖 1 :流入模擬返回路徑的數字電流產生誤差電壓

所有集成電路接地引腳應直接焊接到低阻抗接地層,從而將串聯電感和電阻降至最低。對于高速器件,不推薦使用傳統 IC 插槽。即使是“小尺寸”插槽,額外電感和電容也可能引入無用的共享路徑,從而破壞器件性能。如果插槽必須配合 DIP 封裝使用,例如在制作原型時,個別“引腳插槽”或“籠式插座”是可以接受的。以上引腳插槽提供封蓋和無封蓋兩種版本(AMP 產品型號 5-330808-3 和 5-330808-6)。由于使用彈簧加載金觸點,確保了 IC 引腳具有良好的電氣和機械連接。不過,反復插拔可能降低其性能。

3.低頻和高頻去耦

每個電源在進入 PC 板時,應通過高質量電解電容去耦至低阻抗接地層。這樣可以將電源線路上的低頻噪聲降至最低。在每個獨立的模擬級,各 IC 封裝電源引腳需要更局部、僅針對高頻的濾波。

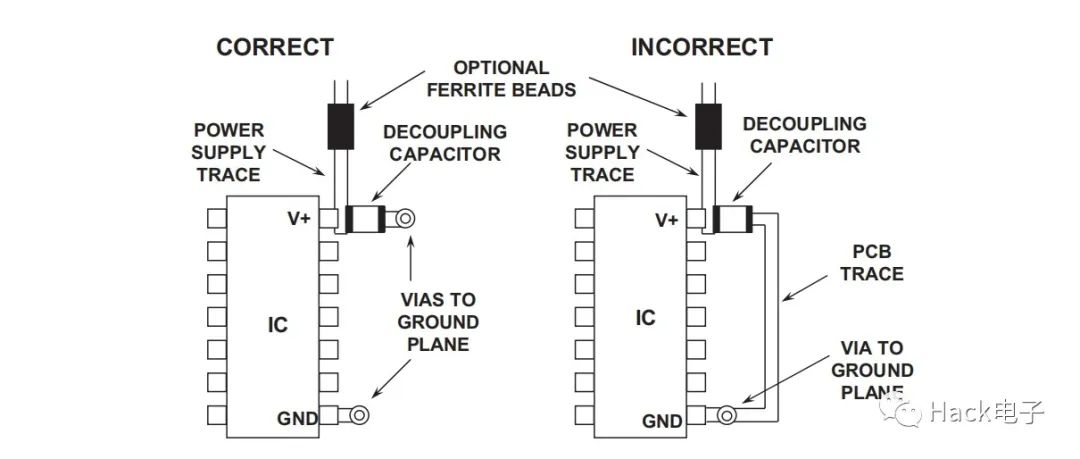

圖 2 顯示了此技術,圖示左側為正確實施方案,右側為錯誤實施方案。左側示例中,典型的 0.1 μF 芯片陶瓷電容借助過孔直接連接到 PCB 背面的接地層,并通過第二個過孔連接到 IC 的 GND 引腳上。相比之下,右側的設置不太理想,給去耦電容的接地路徑增加了額外的 PCB 走線電感,使有效性降低。

圖 2 :局部高頻電源濾波器通過較短的低電感路徑(接地層)提供最佳濾波和去耦

所有高頻(即≥ 10 MHz)IC 應使用類似于圖 2 的旁路方案實現最佳性能。鐵氧體磁珠并非 100% 必要,但會增強高頻噪聲隔離和去耦,通常較為有利。這里可能需要驗證磁珠永遠不會在 IC 處理高電流時飽和。

請注意,對于一些鐵氧體,即使在完全飽和前,部分磁珠也可能變成非線性,所以如果需要功率級在低失真輸出下工作,應檢查這一點。

審核編輯:劉清

-

emi

+關注

關注

53文章

3597瀏覽量

127899 -

模數轉換器

+關注

關注

26文章

3215瀏覽量

126906 -

數字信號處理器

+關注

關注

5文章

470瀏覽量

27375 -

PCB走線

+關注

關注

3文章

134瀏覽量

13959 -

GND

+關注

關注

2文章

539瀏覽量

38808

原文標題:搞清楚模數、數模轉換中的AGND和DGND(1-3)

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解模數、數模轉換器中的AGND和DGND

為什要區分AGND和DGND?搞清楚模數、數模轉換中的AGND和DGND

為什要區分AGND和DGND?搞清楚模數、數模轉換中的AGND和DGND

評論