1.超時判斷機制

在設計中,為了增加異常處理能力,保證設備的正常運行,常常需要進行超時判斷。

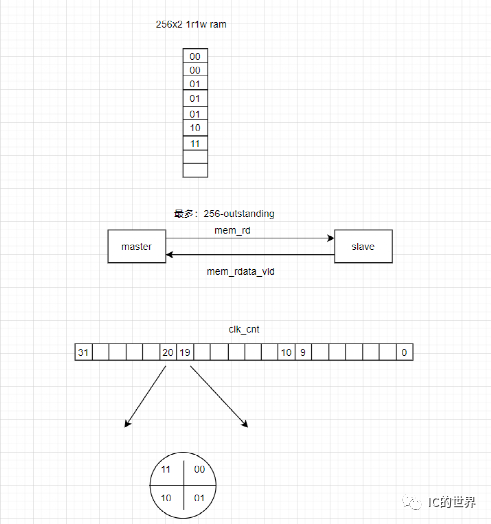

如下圖,當master發起mem讀請求后,收到讀返回數據時,進行超時判斷,如果超時,則數據丟棄,如果沒有超時,則數據正常接收。

2.超時機制實現

如果在數據發送過程中,發送者向接收者發送數據,通常需要接收者通知發送者自身是否可以接收數據

采用一個公共的32bit clk_cnt作為時間基準,根據不同的超時精度,采用32bit中的連續2bit,1GHz時鐘,每個周期1n,例如采用clk_cnt[20:19],可以記錄2^21ns級別的精度,即2ms級別的時間精度。

本文中master能夠發起256個outstanding(未完成)請求,req_id[7:0]從0到255,且工作時鐘clk為1Ghz,發起的mem讀請求,且在1us后都沒有收到數據,則認為超時。

步驟1:master發起mem_rd請求時,以req_id作為地址,將clk_cnt[20:19]作為data,寫入256x2 1r1w_ram中。

步驟2:當master收到讀返回數據時,以req_id作為地址從ram中讀取data,記作clk_cnt_record

步驟3:提取當前時刻clk_cnt[20:19],記錄為clk_cnt_now,如果clk_cnt_now-clk_cnt_record 的絕對值大于1,則表示超時。

案例:

clk_cnt_record 為 10,clk_cnt_now為00,則表示超時。

clk_cnt_record 為 10,clk_cnt_now為11,則認為不超時。

3.特點說明

優點:此類設計比較簡單,所需的邏輯資源較少,并且可以調節超時時間精度。

缺點:

如果超時時間過長,已經從clk_cnt_record翻轉了一圈再返回時,則無法判斷是否為超時。即clk_cnt_record(10)-->11-->00-->01-->10-->11(clk_cnt_now),實際已超時,但是判斷為沒有超時。

沒有讀返回數據時,無法判斷是否超時。

審核編輯:湯梓紅

-

數據

+關注

關注

8文章

7104瀏覽量

89290 -

IC設計

+關注

關注

38文章

1298瀏覽量

104133 -

時鐘

+關注

關注

11文章

1742瀏覽量

131634

原文標題:IC設計:一種簡單超時機制

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IC安全燒錄量產設計的一種機制

espconn_gethostbyname接口DNS解析超時機制要自己做嗎?

請問HAL庫的超時機制可以修改嗎?

Linux串口通信的超時機制

VxWorks共享看門狗定時機制該怎么設計?

分享一個非常簡單的內存數據庫

基于ARP緩存超時的中間人攻擊檢測方法

一種ad hoc網信任聲譽評估機制

基于公平心跳超時容錯機制

IC設計知識點:一種簡單超時機制

STM32程序超時設計

IC設計:一種簡單超時機制

IC設計:一種簡單超時機制

評論