【模擬電路設計】輸入偏置電流(Input Bias Current, IB)

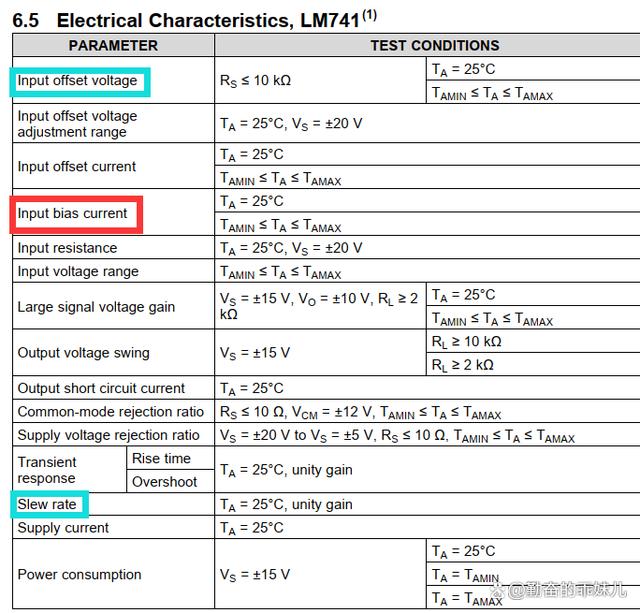

對于新手或者從事芯片封裝行業的人員經常拿到運放的技術手冊不會看,我們最近就以LM741 Operational Amplifier來進行講解,首先先看看圖1,里面涉及很多參數,也是挑選運放最重要的指標,而前面已經講述了Input Offset Voltage(輸入失調電壓)和Slew Rate(壓擺率),大概知道了他們的作用,對他們已經有了一個大概的認識,那今天我們主要講解的內容就是Input Bias Current(輸入偏置電流)。

圖1 LM741 Electrical Characteristics

01輸入偏置電流的理解

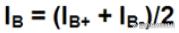

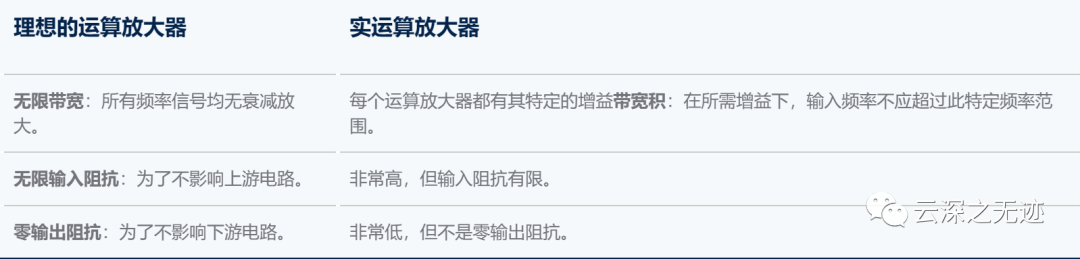

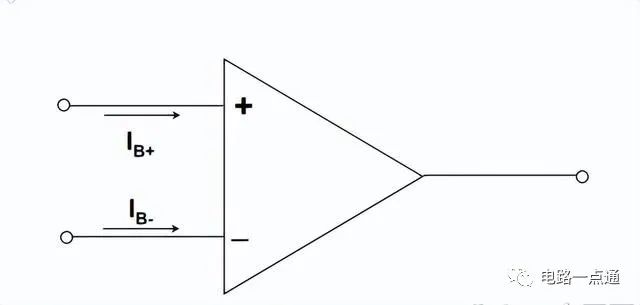

理論來說輸入應具有無窮大的阻抗,這意味著絕對沒有電流流入其中。然而,事實并非如此,所有運算放大器都會有電流流入。流過運算放大器輸入端的電流量稱為輸入偏置電流。輸入偏置電流就是當運放的輸出直流電壓為零時運放兩輸入端流進或流出直流電流的平均值。將輸入偏置電流指定為同相端輸入偏置電流IB+和反相端輸入偏置電流IB的平均值,如圖2所示。

圖2 偏置電流就是兩輸入端之和的平均值

輸入偏置電流與制造工藝有關系,CMOS和JFET輸入比標準雙極輸入有低得多的輸入電流。

輸入偏置電流會在輸入端產生額外的失調電壓降,從而導致輸出端出現失調誤差。對于大多數產品,此問題可以忽略不計,但在某些情況下需要重點考慮。當源阻抗較高時,需要關注輸入偏置電流。如果運算放大器具有高輸入偏置電流,它會加載源并且會看到低于預期的電壓。如果源阻抗很高,最好的解決方案是使用帶有CMOS或JFET 輸入的運算放大器。還可以通過使用緩沖級來驅動具有高輸入偏置電流的運算放大器來降低源阻抗。在雙極輸入的情況下,可以通過匹配輸入端的阻抗來消除失調電流。對于CMOS或JFET 輸入,偏移電流通常不是問題,也不需要匹配阻抗。

CMOS放大器的輸入偏置電流主要由ESD結構、保護二極管和連接到輸入的其他次級電路的泄漏電流決定。該泄漏電流的幅度很小——大約為皮安(pA),如圖3所示。

圖3 輸入級顯示了泄漏如何充當輸入偏置電流

而雙極結型晶體管 (BJT) 放大器的輸入需要基極電流以實現適當的偏置,因此 BJT 輸入偏置電流要大得多——大約為微安(μA)或納安(nA)。對于雙極運算放大器,當輸入差分晶體管導通時,少量電流在基極和發射極之間流動。換句話說,基極-發射極電流是偏置晶體管所需的電流量。該電流通常在納安或微安的范圍內。對于PNP輸入對,電流流出輸入晶體管,如圖4所示為雙極放大器的簡化PNP輸入級。對于軌到軌輸入雙極運算放大器,將使用額外的NPN輸入對,電流將流入NPN輸入級。因此,輸入偏置電流是BJT放大器的一個重要問題。

圖4 輸入偏置電流如何改變放大器輸出

問題1:那么你可能會有疑惑,既然CMOS放大器的輸入偏置電流幾乎可以忽略不計,為什么還需要BJT放大器?

回答1:在相同的靜態電流下,與CMOS晶體管相比,BJT具有更大的跨導(gm)。此外,BJT 之間的匹配也好很多,1/f噪聲也是如此。這三個優點對于高速精密放大器都是至關重要的;因此,BJT 輸入在高性能運算放大器和全差分放大器(FDA)中無處不在。

02輸入偏置電流的影響

輸入偏置電流會影響放大器的輸出。例如,如果有一個大電阻與運算放大器輸入串聯,則IB流過它并增加一個偏移量。例如,圖5中所示的原理圖。IB =10nA的電壓跟隨器電路(也稱為單位增益緩沖電路)中的1MΩ輸入電阻器會在電阻器上產生額外的10mV電壓降,從而導致10mV的輸出誤差。

圖5 輸入偏置電流在該單位增益電路中產生電壓偏移

為了消除IB產生的任何偏移電壓,有時電路設計人員會嘗試匹配運算放大器的同相和反相輸入端子所見的輸入電阻,如圖6所示。然而,如果偏置電流不匹配,產生的輸入失調電流(IOS)仍會產生額外的輸入失調電壓。IOS產生的這種偏移電壓會導致輸出誤差。

圖6 輸入電阻匹配可以降低輸入偏置電流的影響

今天的分享就到這里,若還需要了解其他內容,可以私信聯系我們,您的支持,將是我們前進的動力,歡迎點贊關注。

-

運算放大器

+關注

關注

215文章

4959瀏覽量

173235 -

運放

+關注

關注

47文章

1169瀏覽量

53166 -

芯片封裝

+關注

關注

11文章

508瀏覽量

30657 -

輸入偏置電流

+關注

關注

0文章

8瀏覽量

5895

發布評論請先 登錄

相關推薦

運算放大器的類型

運算放大器輸入偏置電流的理解和影響

運算放大器輸入偏置電流的理解和影響

評論