來源:內容由半導體行業觀察(ID:icbank)編譯自allaboutcircuit,謝謝。

在這個項目中,我們用 VHDL 語言創建一個 8 位算術邏輯單元 (ALU),并在連接到帶有輸入開關和 LED 顯示屏的定制 PCB 的 Altera CPLD 開發板上運行。

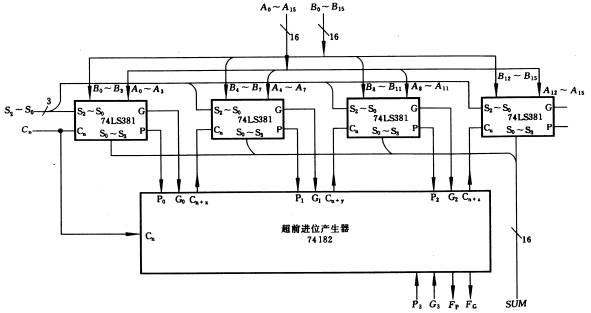

使用基于硬件的方法開發電子系統并不總是需要將各種晶體管和邏輯門物理連接到面包板或 PCB 上。可以使用離散邏輯構建算術邏輯單元(ALU),但隨著邏輯復雜性的增加,有更好的選擇。通過可編程邏輯器件和硬件描述語言(HDL),從簡單電路到高度專業化的處理單元的任何東西都可以在單個芯片內實現。

ALU項目概述

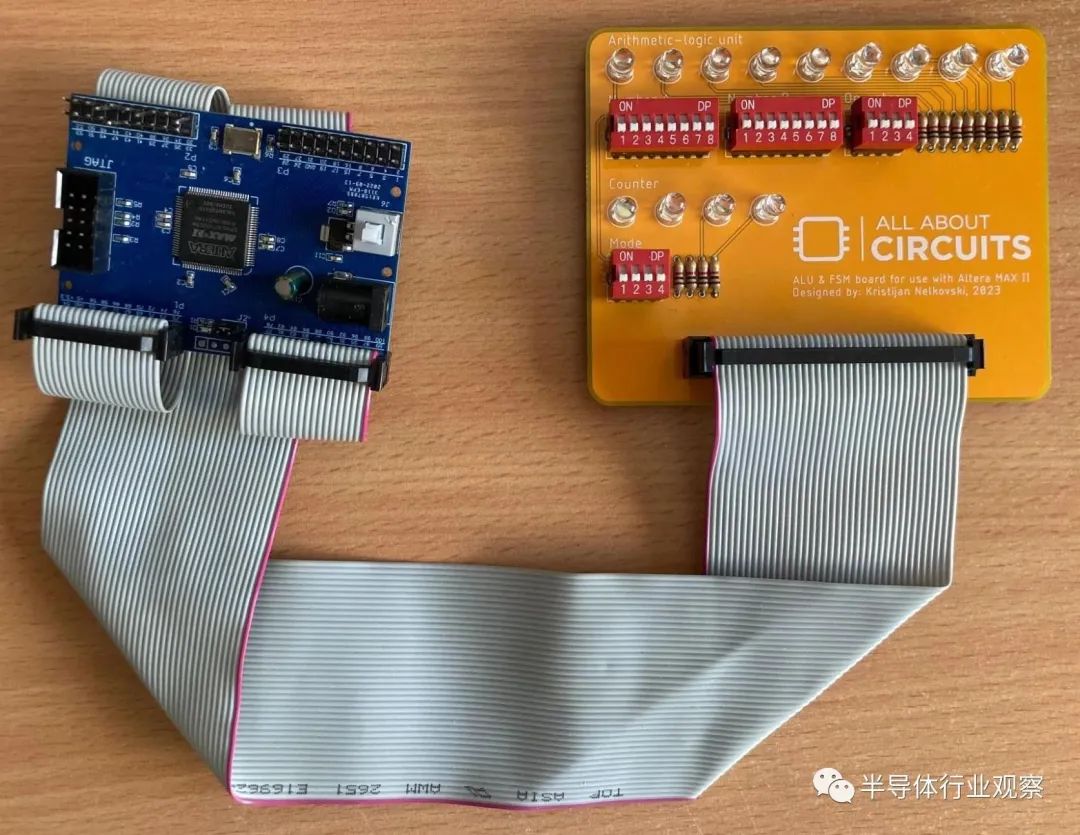

在這個項目中,我將逐步創建帶有輸入 DIP 開關和輸出 LED 的 8 位 ALU 電路,如圖 1 所示。我使用 VHDL 語言對 ALU 進行編碼,并在復雜可編程邏輯器件上運行它( CPLD)開發板。我的目標是介紹可編程邏輯,并為使用真實硬件而不僅僅是圖表和計算機模擬打開大門。

對于此項目,我構建了帶有 All About Circuits 品牌的定制印刷電路板 (PCB),如圖 2 所示。與更知名的現場可編程門陣列(FPGA ) 相比,CPLD 是一種更實惠但功能稍弱的可編程邏輯器件)。這兩種器件均可用于創建具有專用輸入和輸出的定制電子設計。

在內部,這些 CPLD 和 FPGA 組件包含可重新配置邏輯塊陣列,并封裝為獨立 IC,以便嵌入到您自己的設計中。制造商提供開發板,用于使用其技術和軟件環境進行學習、測試和實驗。我的 CPLD 使用了開發板。

什么是 ALU?

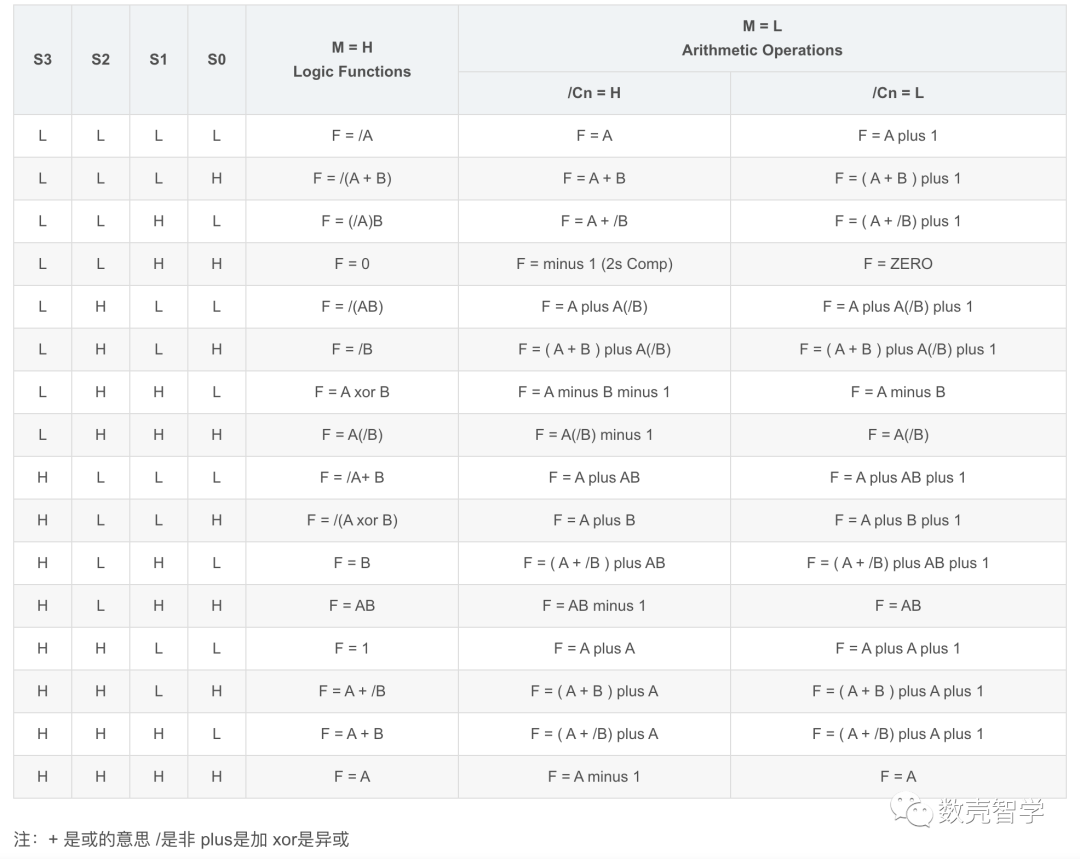

每個處理器的核心都有一個組合邏輯電路,它對整數二進制數執行算術和按位運算,稱為算術邏輯單元。我們將在這個項目中構建的電路是一個 8 位 ALU,它包含兩個 8 位操作數(輸入)、一個 8 位結果(輸出)和一個 4 位操作碼(輸入),該操作碼定義將執行什么操作(圖3)

ALU 通常包含狀態位(既作為輸入又作為輸出),為處理器提供有關上次執行操作的重要信息。該狀態信息可以包括結果是否為零或者結果是否溢出到最高有效位(MSB)之外。然而,我們的電路不需要它們,因此不會包含任何它們。

ALU 為學習 VHDL 編碼和 CPLD 編程操作提供了一個極好的起點。完成此項目后,您可以輕松擴展到更困難的應用程序。

項目詳情和參考資料

在這個項目中,我們將用VHDL語言創建一個8位算術邏輯單元(ALU),并使用Intel的Quartus Prime Lite Edition軟件(Altera現已成為Intel的一部分)在Altera Max II EPM240 CPLD開發板上運行它。該電路的代碼基于加州大學河濱分校發布的實驗室練習設計。

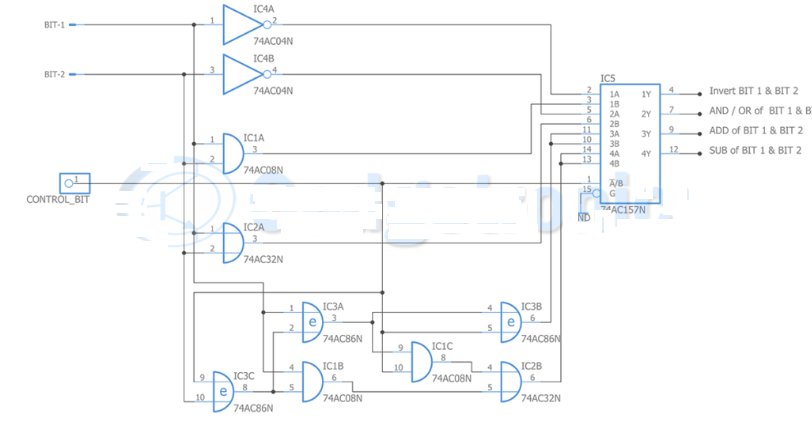

對于這個項目,您需要對編程和離散邏輯有基本的理解。查看AAC 對 VHDL和4 位離散邏輯 ALU 項目的介紹也會有所幫助。

注意:雖然我創建了一個用于該項目的“屏蔽”型板,但這里介紹的所有內容都完全適合面包板和穿孔板。

使用 Quartus Prime 為 Altera MAX II 開發板設置新項目

要開始處理我們的項目,我們需要下載并安裝 Quartus Prime Lite Edition 并創建一個文件夾來存儲所有項目。我從Intel的網站下載了該軟件,并在“Windows Documents”目錄中創建了一個名為“quartus”的文件夾。

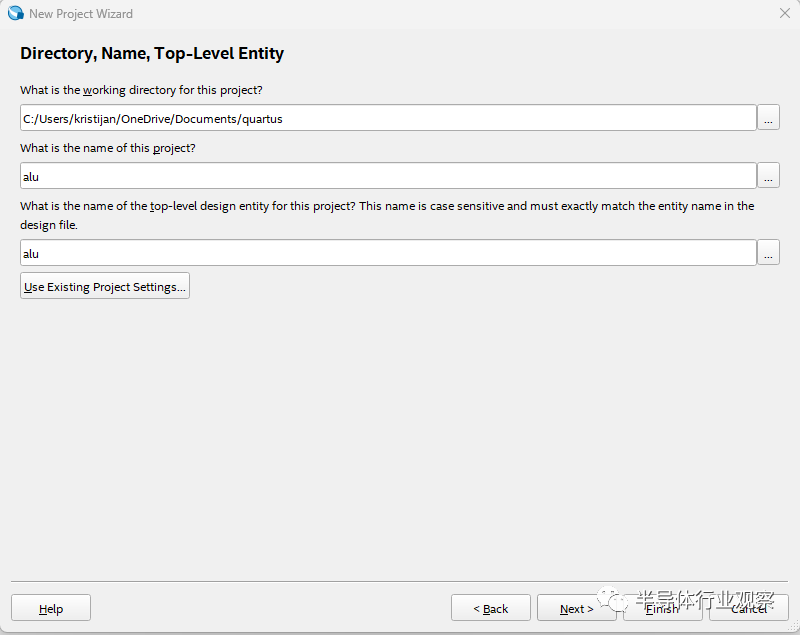

當我們運行 Quartus 時,我們需要做的第一件事是通過“New Project Wizard”建立一個新項目,該向導可以在“File -> New Project Wizard”下找到。然后,我們需要在名為“簡介”的第一個屏幕上單擊“下一步”。

如圖 4 所示,在名為“目錄、名稱、頂級實體”的第二個屏幕上,我們需要選擇之前創建的文件夾作為工作目錄,并為當前項目指定適當的名稱。我將這個項目命名為“ALU”。

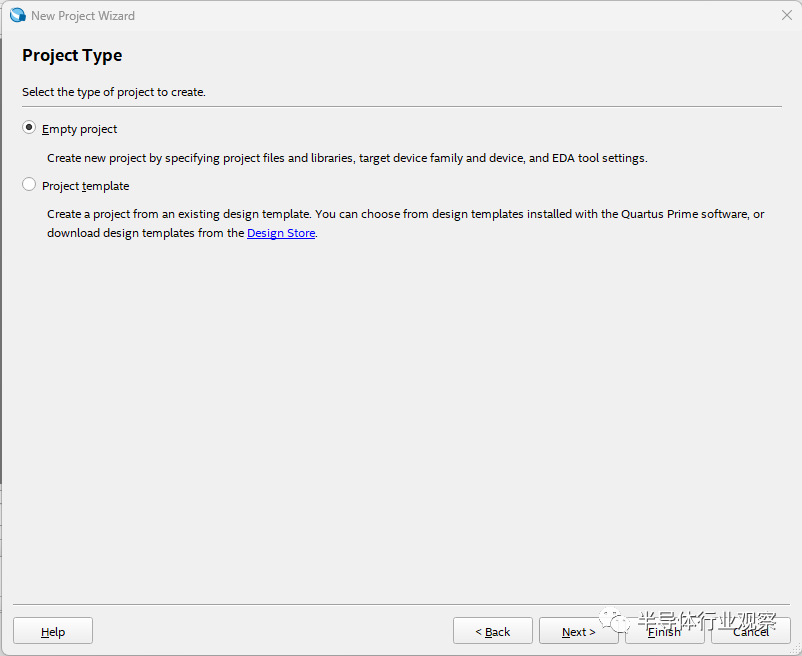

對于“項目類型”屏幕,我們需要選擇“空項目”并將下一個名為“添加文件”的屏幕保留為空(圖 5)。

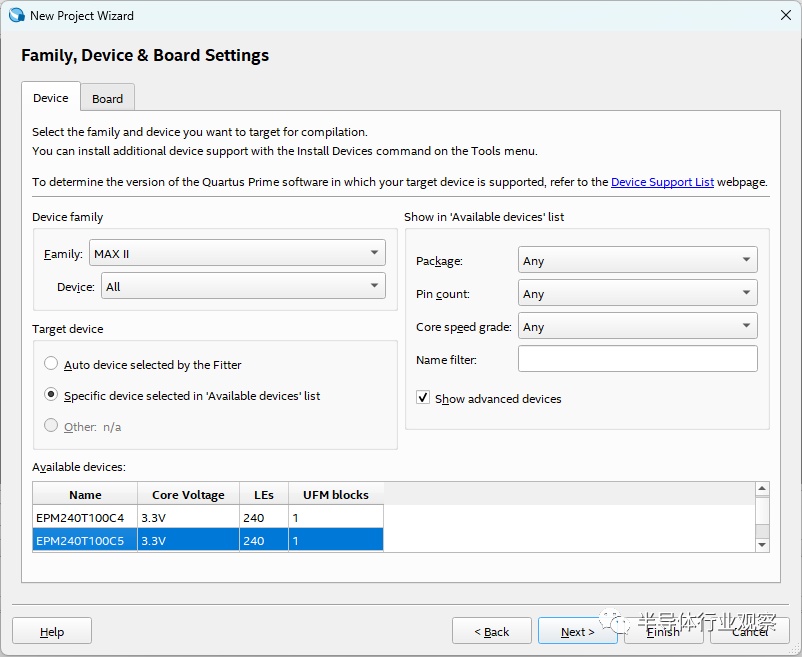

在“Family, Device & Board Settings”屏幕上,我們需要從“Device family”部分的下拉菜單中選擇“MAX II”(圖 6)。然后,從“Available devices”部分中選擇“EPM240T100C5”,因為這是 Altera MAX II EPM240 上的芯片。

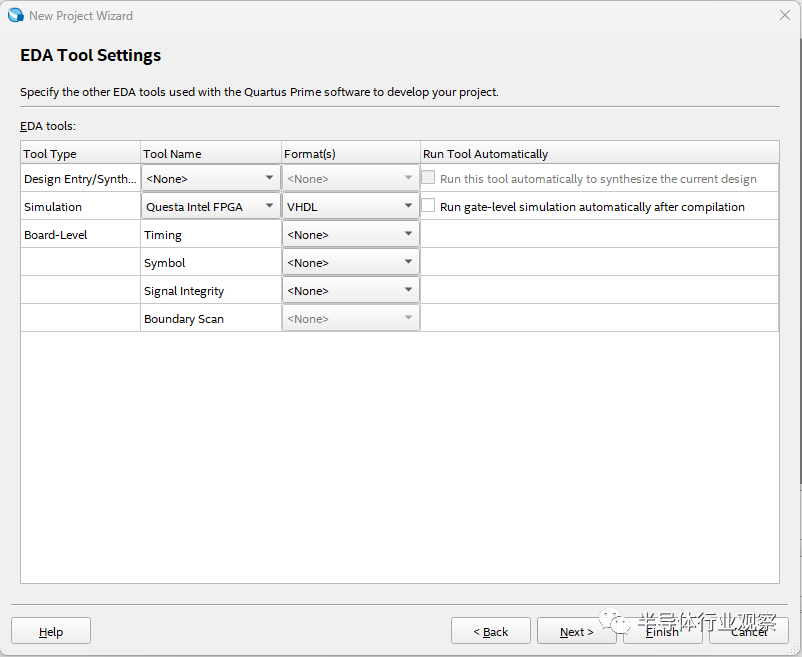

接下來,我們需要在“EDA Tool Settings”屏幕上將“Verilog HDL”更改為“VHDL”,單擊“下一步”,并檢查“Summary”中的一切是否正確(圖7)。之后,我們可以單擊“完成”按鈕,我們的新項目將被創建。

該項目打開后,我們需要在“項目導航器:層次結構”窗口中單擊實體的名稱,然后按“CTRL+N”并選擇“VHDL 文件”來創建一個新的 VHDL 文件。

該文件打開后,我們必須通過進入“文件 -> 另存為”將其另存為實體的 VHDL 文件。當所有這些完成后,我們就可以開始為 ALU 編寫代碼了。

聲明 VHDL 庫

與所有編程語言一樣,我們需要在 VHDL 代碼頂部做的第一件事是聲明將在項目中使用的庫。

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

USE ieee.std_logic_arith.ALL;

現在我們需要設計電路的架構或行為。我們將使用三個輸入或端口A、B和Sel創建一個流程。

在此過程中,我們可以調用“case-when”語句(類似于其他編程語言中的“switch-case”),在其中檢查端口SEL的狀態。SEL值是 ALU 的操作碼,決定在端口A和B接收的兩個 8 位數字之間需要執行哪個操作。

這是在語句的“when XXXX =>”部分完成的,其中XXXX代表SEL的二進制狀態(0000 到 1111 之間的位置)。每個狀態都分配給使用端口A和B上接收到的值執行的相應 ALU 操作。輸出在端口RES上寫出。

之后,我們可以結束“case”語句、流程和行為架構,并結束我們項目的代碼部分。

ARCHITECTURE behv OF alu IS

BEGIN

PROCESS (A, B, Sel)

BEGIN

CASE Sel IS

WHEN "0000" =>

RES <= "00000000"; -- no operation

WHEN "0001" =>

RES <= A + B; -- addition

WHEN "0010" =>

RES <= A + (NOT B) + 1; -- subtraction

WHEN "0011" =>

RES <= A + 1; -- add one to operand A

WHEN "0100" =>

RES <= A - 1; -- subtract one from operand A

WHEN "0101" =>

RES <= A(6 DOWNTO 0) & '0'; -- shift operand A to the left

WHEN "0110" =>

RES <= '0' & A(7 DOWNTO 1); -- shift operand A to the right

WHEN "0111" =>

RES <= NOT A; -- one's complement of operand A

WHEN "1000" =>

RES <= NOT A + 1; -- two's complement of operand A

WHEN "1001" =>

RES <= A AND B; -- logical and

WHEN "1010" =>

RES <= A OR B; -- logical or

WHEN "1011" =>

RES <= A NAND B; -- logical nand

WHEN "1100" =>

RES <= A NOR B; -- logical nor

WHEN "1101" =>

RES <= A XOR B; -- logical xor

WHEN "1110" =>

RES <= (NOT A) + (NOT B); -- random operation

WHEN "1111" =>

RES <= (A + B) AND (A OR B); -- another random operation

WHEN OTHERS =>

RES <= "00000000";

END CASE;

END PROCESS;

END behv;

在上面的代碼中,我包含了一些最常見的算術和邏輯運算以及一些隨機運算,并對它們各自的作用進行了評論。在這里您可以替換并包含您想要的任意算術或邏輯運算!

引腳映射

當我們的代碼完成后,我們需要做的第一件事就是編譯它。這可以通過進入“處理 -> 開始編譯”來完成。如果一切都正確編譯,我們不應該收到任何錯誤消息,盡管我們可能會收到一些可以忽略的警告。

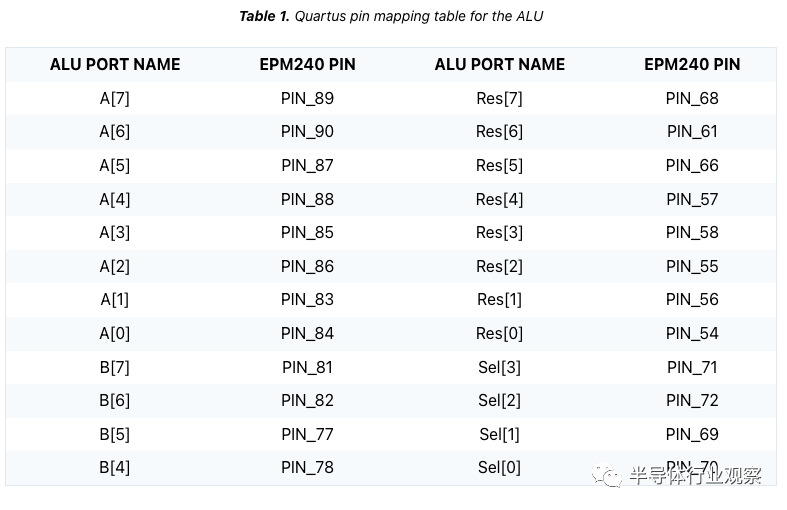

接下來,我們需要將之前為實體定義的端口連接到 Altera 開發板上的物理引腳。我們將通過 Quartus 的 Pin Planner 工具來完成此操作,該工具可通過“Assignments -> Pin Planner”訪問。

引腳規劃器工具包含:

所用芯片(本例中為 EPM240)的直觀表示。

描述每種引腳類型的引腳圖例。

包含來自我們實體端口的每個單獨節點的表。在此表中,我們可以通過將每個節點寫到“位置”列的相應行中,將其連接到專用引腳。

表 1 包含我生成的引腳分配表。

將代碼上傳到 Altera 開發板

將每個輸入和輸出分配給引腳后,我們需要再次編譯代碼。如果沒有彈出錯誤消息,我們可以繼續將其上傳到Altera MAX II。

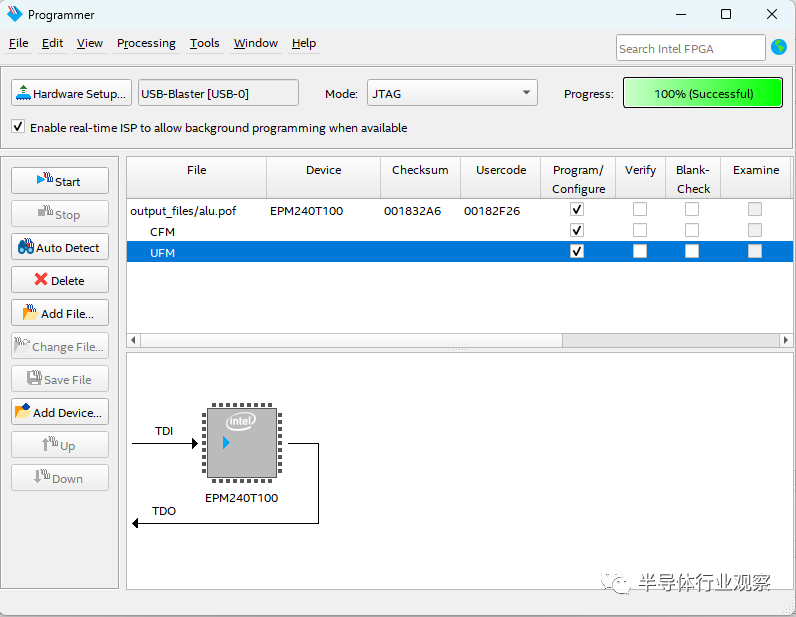

為此,我們首先必須通過板載桶形插孔將板本身連接到 5 V 電源。接下來,我們必須通過JTAG端口將其連接到 USB Blaster,然后使用迷你 USB 插孔將 USB Blaster 連接到我們的計算機(圖 8)。

之后,我們可以通過進入“工具->編程器”并選中“編程/配置”來運行編程器,如圖9所示。然后我們需要打開“硬件設置”并選擇“USB Blaster”作為我們的“可用硬件” item”(我們的程序員),然后單擊“Start”將我們的代碼上傳到 Altera MAX II。

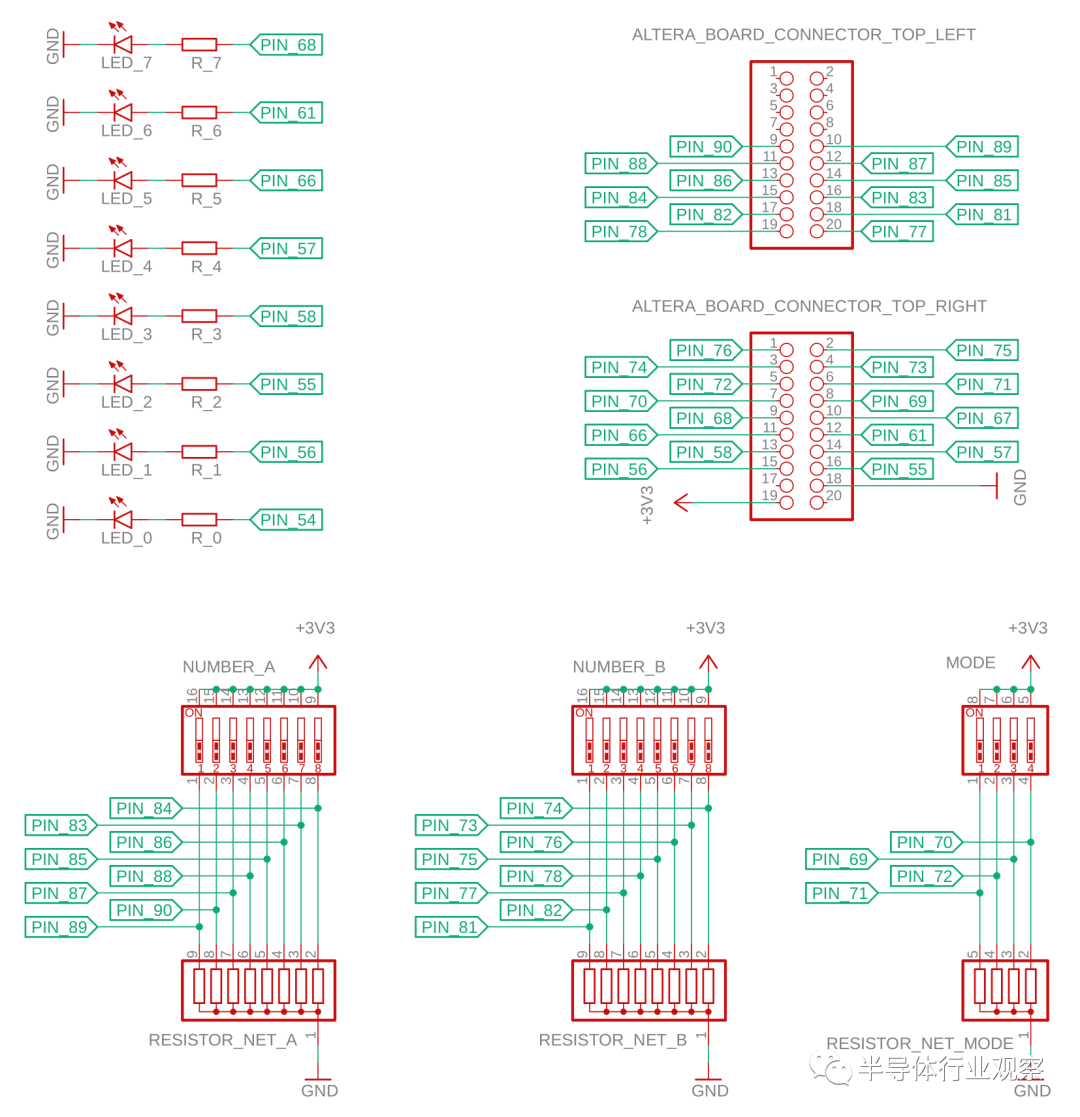

PCB電路圖

圖 10 的原理圖描繪了我們的電路圖。每個 LED 通過限流電阻連接到輸出引腳。連接到輸入引腳的 DIP 開關的每個觸點也通過電阻網絡下拉至地面(在定制 PCB 上,這些觸點隱藏在 DIP 開關下方)。

連接完所有內容并為 Altera 板供電 5 V 后,我們可以通過在操作數端口上輸入數字并將操作模式切換到我們喜歡的任何操作來看到 ALU 開始工作。LED 顯示結果,如上圖 1 所示。

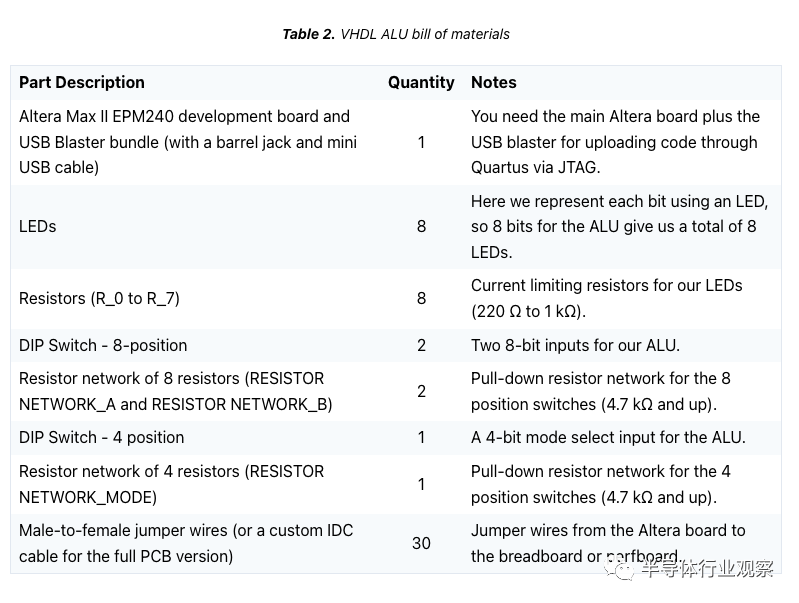

ALU 項目的 BOM

表 2 包含該項目的材料清單。

在這個項目中,我們用VHDL語言創建了一個8位ALU電路,并在CPLD開發板上運行它。在這里,我的目標是介紹可編程邏輯,并為使用真實硬件組件而不是圖表和計算機模擬來使用 FPGA 組件打開大門。

如果您復制此項目,您可以輕松地將其他操作碼添加到 ALU 的 VHDL 操作中。您還可以修改電路設計以輸出和顯示狀態代碼。在下面的評論中分享您的想法或項目!

審核編輯:湯梓紅

-

FPGA

+關注

關注

1638文章

21867瀏覽量

610484 -

晶體管

+關注

關注

77文章

9887瀏覽量

139926 -

vhdl

+關注

關注

30文章

819瀏覽量

129157 -

開發板

+關注

關注

25文章

5287瀏覽量

100167 -

ALU

+關注

關注

0文章

33瀏覽量

13211

原文標題:從VHDL代碼到實際硬件:設計一個 8 位 ALU

文章出處:【微信號:ZYNQ,微信公眾號:ZYNQ】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于可編程邏輯器件和VHDL語言實現算術邏輯單元的設計

使用Robei利用verilog語言做ALU設計

什么是ALU/Brach Pediction

關于通過FPGA中VHDL語言實現ALU的功能設計詳解

評論