在當今快節奏的世界中,半導體設計的創新是一項永恒的需求。對更快、更準確、更創新的解決方案的需求為探索生成式人工智能(#GenerativeAI)在半導體設計開發領域的潛力鋪平了道路。能做到嗎?當然可以!在本系列文章中,我們將深入探討令人興奮的實驗,展示生成式人工智能如何徹底改變半導體設計。

實例 1 - 從 FSM 圖到 SV 代碼

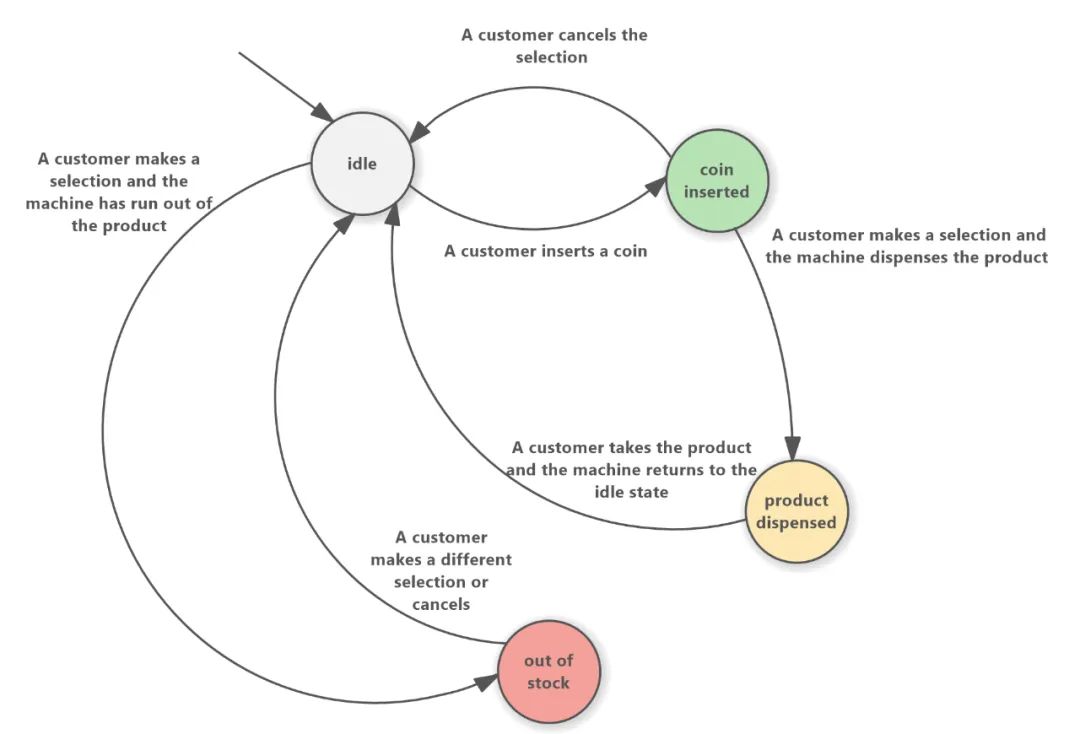

第一個實驗通過將有限狀態機 (FSM) 圖轉換為 SystemVerilog (SV) 代碼,展示了生成式人工智能的非凡能力。

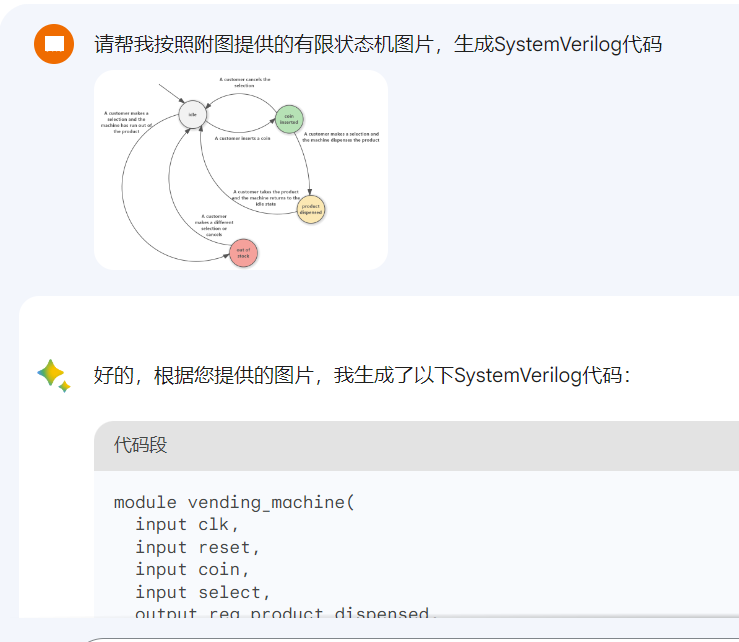

在本例中,谷歌的生成式人工智能模型--BARD 被用來生成一個自動售貨機 FSM 的 SystemVerilog 實現。

狀態機圖片:

代碼如下:

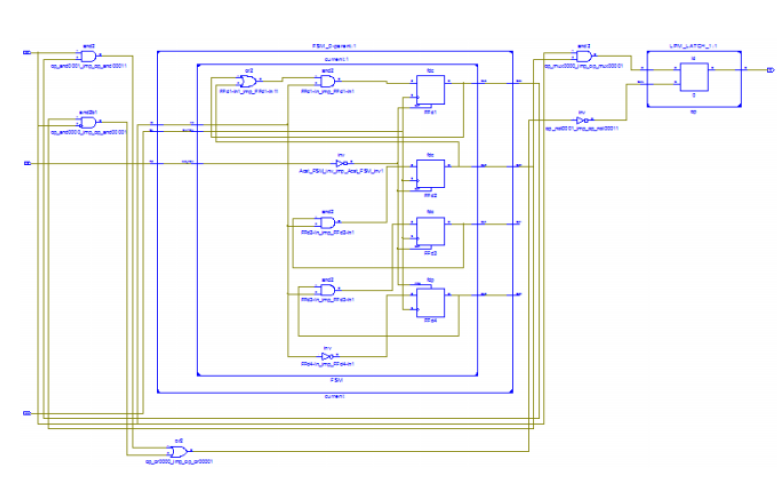

// Vending machine FSM // Disclaimer: This code is not tested for correctness module vending_machine ( input clk, input reset, input coin_inserted, input product_selected, input product_dispensed, output reg dispense_product, output reg return_coin ); // Define the states localparam [2:0] IDLE = 3'b000; localparam [2:0] COIN_INSERTED = 3'b001; localparam [2:0] PRODUCT_SELECTED = 3'b010; localparam [2:0] PRODUCT_DISPENSED = 3'b011; localparam [2:0] OUT_OF_STOCK = 3'b100; // Define the registers reg [2:0] current_state; // Transition logic always @(posedge clk or posedge reset) begin if (reset) begin current_state <= IDLE; end else begin case (current_state) IDLE: begin if (coin_inserted) begin current_state <= COIN_INSERTED; end else begin current_state <= IDLE; end end COIN_INSERTED: begin if (product_selected) begin current_state <= PRODUCT_SELECTED; end else begin current_state <= COIN_INSERTED; end end PRODUCT_SELECTED: begin if (product_dispensed) begin current_state <= PRODUCT_DISPENSED; end else if (out_of_stock) begin current_state <= OUT_OF_STOCK; end else begin current_state <= PRODUCT_SELECTED; end end PRODUCT_DISPENSED: begin current_state <= IDLE; end OUT_OF_STOCK: begin current_state <= IDLE; end endcase end end // Output logic always @(posedge clk) begin case (current_state) PRODUCT_DISPENSED: begin dispense_product <= 1'b1; end default: begin dispense_product <= 1'b0; end endcase end always @(posedge clk) begin case (current_state) OUT_OF_STOCK: begin return_coin <= 1'b1; end default: begin return_coin <= 1'b0; end endcase end endmodule

有限狀態機在芯片設計中得到廣泛應用,以下是生成式人工智能如何發揮關鍵作用:

提高生產力:有了生成式人工智能,創建和更新圖表變得輕而易舉。設計人員現在可以專注于高級概念,讓人工智能來做基礎工作。這不僅加快了開發過程,還能在需要更改設計時迅速進行迭代。

更高的準確性:FSM 已經成為硬件設計的標準化工具。生成式人工智能模型經過大量數據集的訓練,能夠熟練地將這些圖表轉換為準確的 SV 代碼。減少了人為錯誤,提高了代碼質量。

提高創新能力:生成式人工智能的速度和準確性為快速探索新的設計理念打開了大門。設計人員可以利用各種 FSM 圖表進行頭腦風暴和實驗,從而推動創新。這種靈活性使每一代半導體器件都能更快地集成先進功能。 雖然生成式人工智能前景廣闊,但必須謹慎行事。生成的代碼不一定總是完美的。在將人工智能生成的代碼部署到生產環境之前,設計人員必須對其進行審查和嚴格測試。徹底的驗證過程對于確保最終半導體設計的可靠性和功能性至關重要。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27601瀏覽量

220912 -

AI

+關注

關注

87文章

31338瀏覽量

269746 -

人工智能

+關注

關注

1793文章

47539瀏覽量

239392 -

有限狀態機

+關注

關注

0文章

52瀏覽量

10357

原文標題:用生成式AI設計芯片,實例1:從有限狀態機圖片直接生成SV代碼

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么是有限狀態機呢

有限狀態機的建模與優化設計

VHDL有限狀態機設計-ST

初學者對有限狀態機(FSM)的設計的認識

如何使用FPGA實現序列檢測有限狀態機

有限狀態機設計是HDL Designer Series的關鍵應用

基于事件驅動的有限狀態機介紹

基于事件驅動的有限狀態機介紹

一個基于事件驅動的有限狀態機

從有限狀態機圖片直接生成SV代碼

從有限狀態機圖片直接生成SV代碼

評論