生活中加減乘除是多么簡單的事情,小學一年級的小朋友已經能熟練的掌握。本書主要是面向大學本科以上的讀者,卻直到第三章才敢小心翼翼的提出如何讓電路做加法運算,也不得不感嘆,人們設計出計算機是花費了多么大的心血。

首先我們要看看電路如何去做加法。

3.1. 一位加法器設計

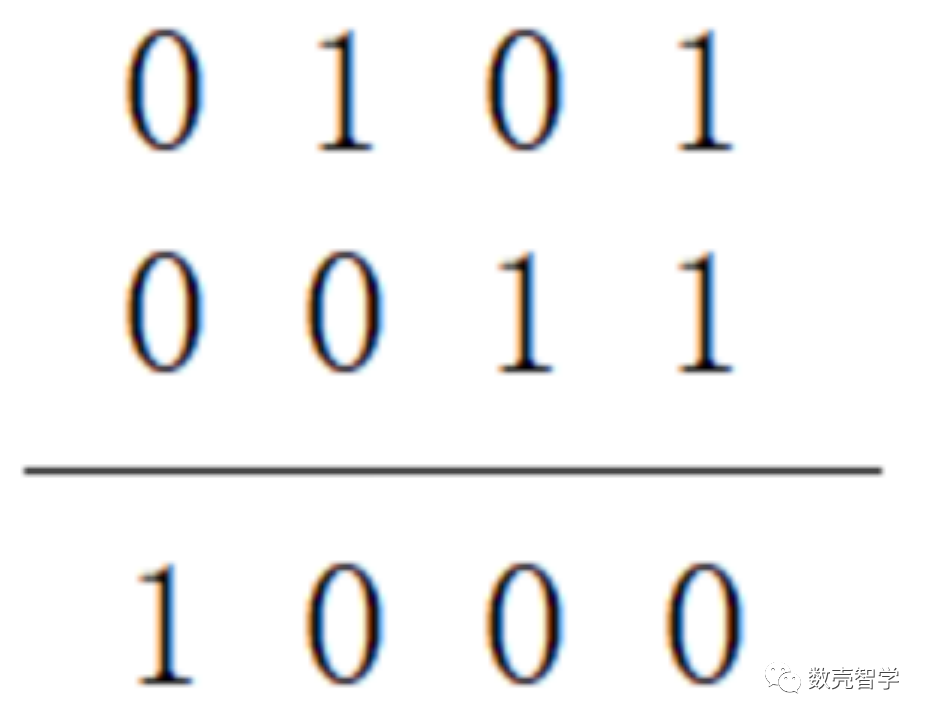

首先我們來看二進制加法的具體步驟(以0101 + 0011為例)(如圖 3-1),數字的最右邊為第0位,往左依次是第1、2、3位。步驟如下:

1.把0101 用A表示,0011用B表示,相加的和用S表示;A的第n位用An表示,B的第n位用Bn表示,S的第n位用Sn表示;用Ci表示當前位來自前一位的進位;

2.第0位二進制相加,A0 + B 0 = 1 + 1 = 10 ,則S0 = 0,C1 =1;

3.第1位二進制相加,A1 + B1 + C1 = 0 + 1 + 1 = 10 ,則S1 = 0, C 2 =1 ;

4.第2位二進制相加,A2 + B2 + C2 = 1 + 0 + 1 = 10 ,則S2 = 0, C 3 =1 ;

5.第3位二進制相加,A3 + B3 + C3 = 0 + 0 + 1 = 01 ,則S3 = 1, C 4 =0 ;

6.所以最終的結果是:C4S3S2S1S0 = 01000

圖 3-1 二進制相加的例子

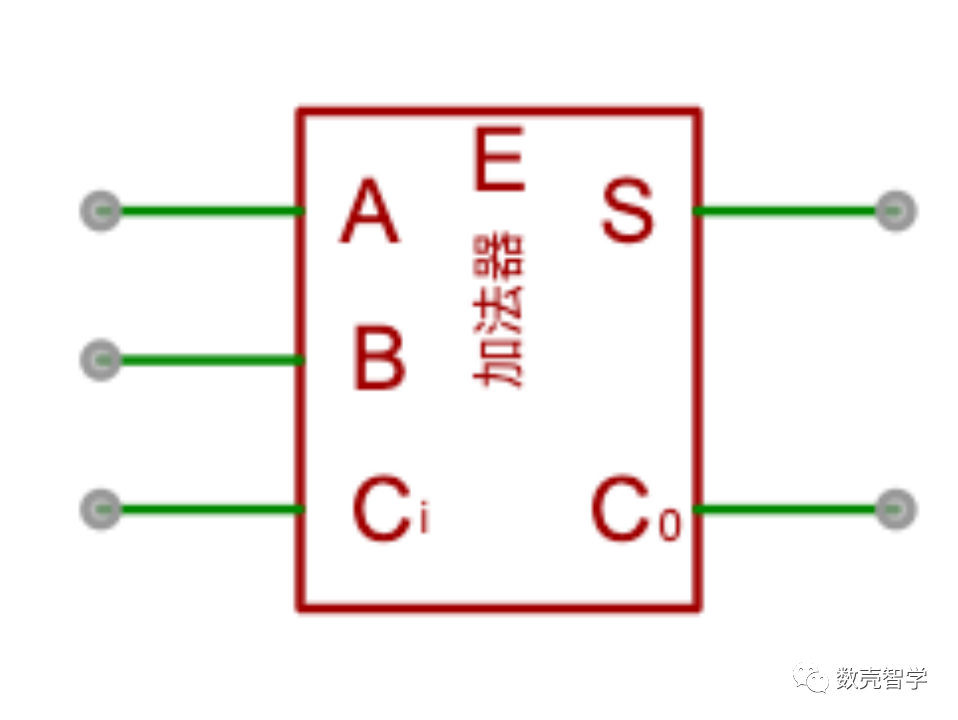

從上面的例子中總結出一位加法器的設計需求。兩個二進制數字的對應位數字相加的需求,需要3個輸入,2個輸出(如圖 3-2)。A和B是來自加數和被加數的兩個比特;Ci是來自前一個比特位的進位;S是前面三項加起來的“和”;C0是當前這一位向下一位的進位。

圖 3-2 一位加法器的符號

我們可以發現一個3個輸入,2個輸出的元器件,可以列出所有的輸入輸出的可能數值,具體如表 3-1 。設計電路的方法就是找到一個電路集合,能夠同時滿足表中的8種輸入輸出情況的邏輯,也就是當輸入的A、B、Ci為某一行的值的時候,S、C0的輸出同時要符合表中列出的數值,比如參照第5行,當輸入A=1、B=0、C ~i~ =1,的時候輸出S=0、C ~0~ =1。

表 3-1 一位加法器真值表

| 序號 | A | B | Ci | S | C0 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 | 0 |

| 3 | 0 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 1 | 0 | 1 |

| 5 | 1 | 0 | 0 | 1 | 0 |

| 6 | 1 | 0 | 1 | 0 | 1 |

| 7 | 1 | 1 | 0 | 0 | 1 |

| 8 | 1 | 1 | 1 | 1 | 1 |

我們可以分成兩部分來考慮,第一部分是輸入A、B、C i, 輸出S的電路設計;第二部分是輸入A、B、C i, 輸出C0的電路設計;這是兩個獨立的電路,為了實現完整的一位加法器功能的模塊,把兩個電路以放在一起就行了。

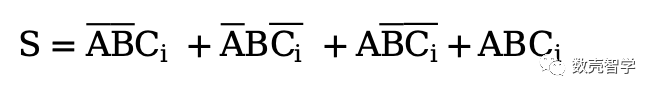

對于第一部分電路,從表 3-1中可以看出,第2、3、5、8行等于1,其他行等于0。S的邏輯表達式只需要滿足2、3、5、8行的其中一種輸入情況(“或”的邏輯關系),另S =1。則S的完整邏輯表達式為:

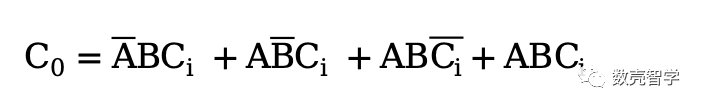

同理,第二部分電路設計中,C0的完整邏輯表達式為:

如果對邏輯表達式的設計還不是非常熟悉的讀者,可以用這兩個邏輯表達式來驗證表 3-1,對于每一行的A、B、Ci的輸入,輸出的S和C0的值都完美的對應。

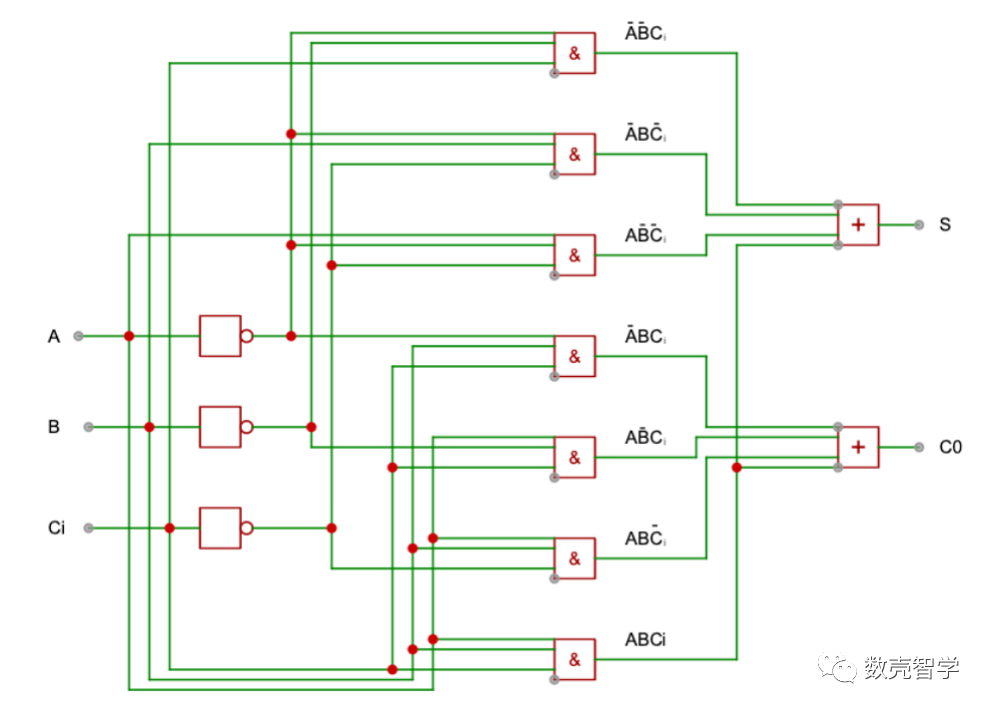

接下來的電路設計,把邏輯表達式中的“與”、“或”、“非“的邏輯關系變成電路中的“與門”、“或門”、“非門”,在加上連線就是我們需要的加法器的電路圖。直接上圖(圖 3-3):

圖 3-3 加法器的邏輯電路圖

3.2. 加法實驗電路

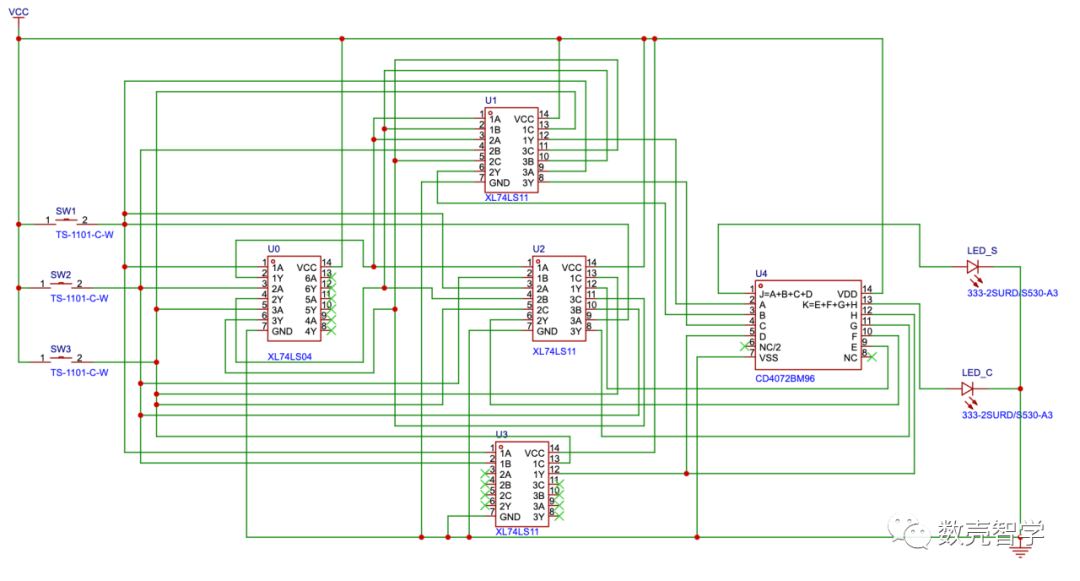

用三個商用的“非門”(圖 2-14)、“與門”(圖 2-15)、“或門”(圖 2-16)芯片組成實際的加法器實現電路圖(圖 3-4)。

圖 3-4根據邏輯門芯片繪制的加法器電路原理圖

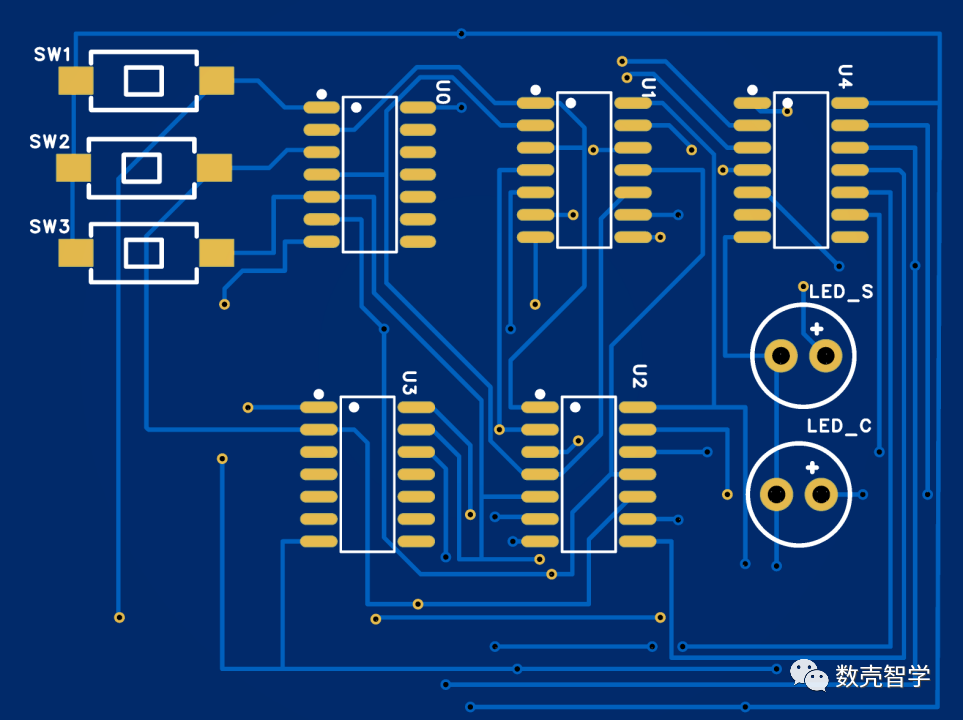

圖 3-5根據門電路芯片設計的加法器PCB板(正面)

3.3. 用加法器實現加法

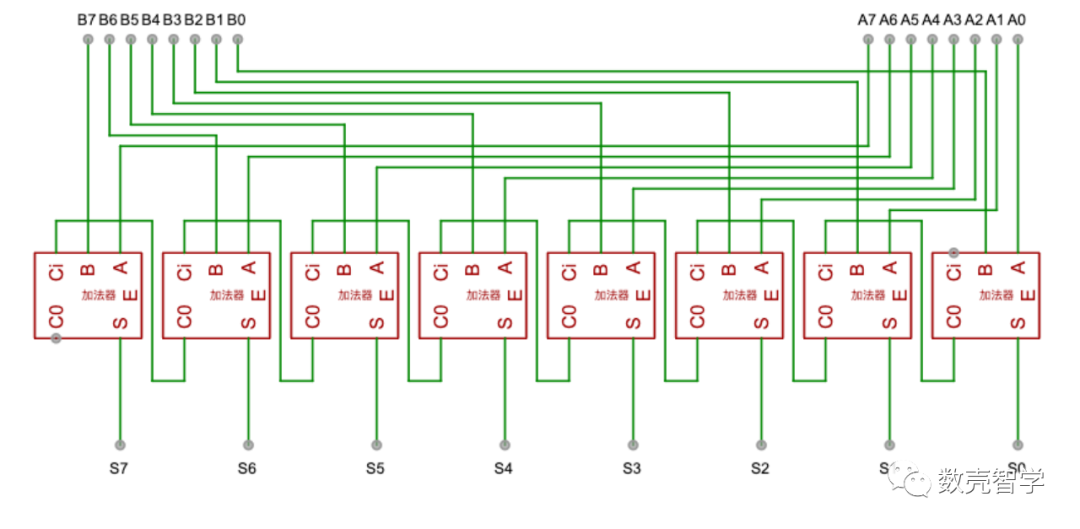

兩個二進制數字相加為例,利用加法器設計電路圖實現二進制加法。

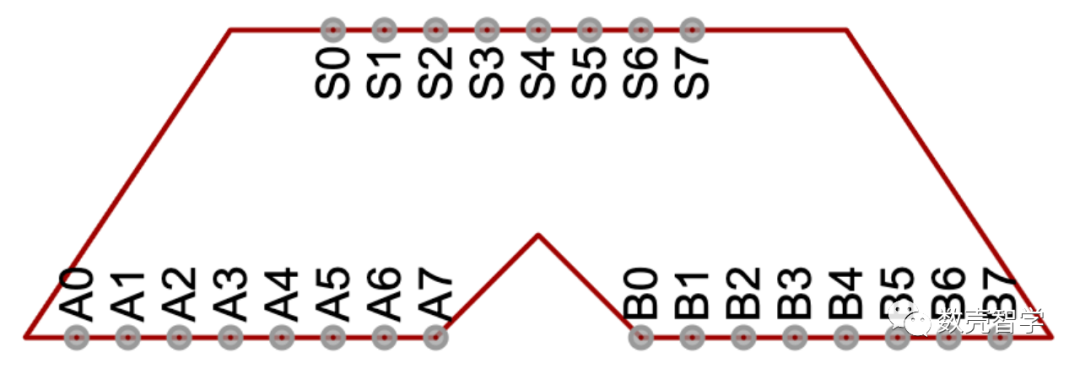

圖 3-6用加法器組成一個八位加法電路

將圖 3-6簡化成8位加法器示意圖:

圖 3-7 八位加法器的示意圖

3.4. 加法實驗

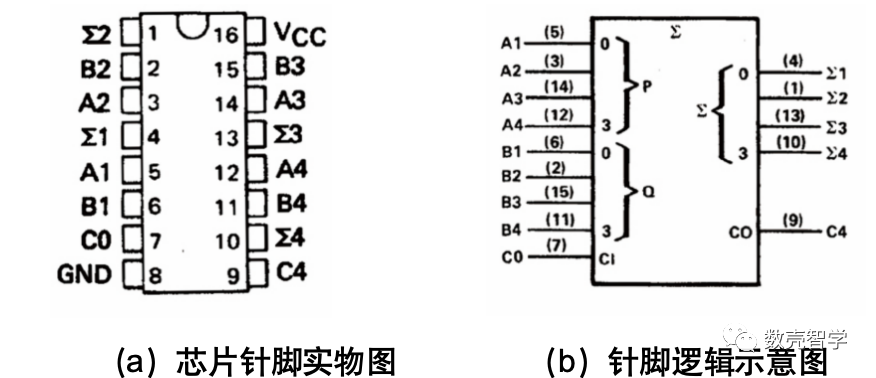

3.4.1. 常用全加芯片XD74LS283

圖 3-8 四位加法器XD74LS283針腳示意圖

3.4.2. 加法實驗

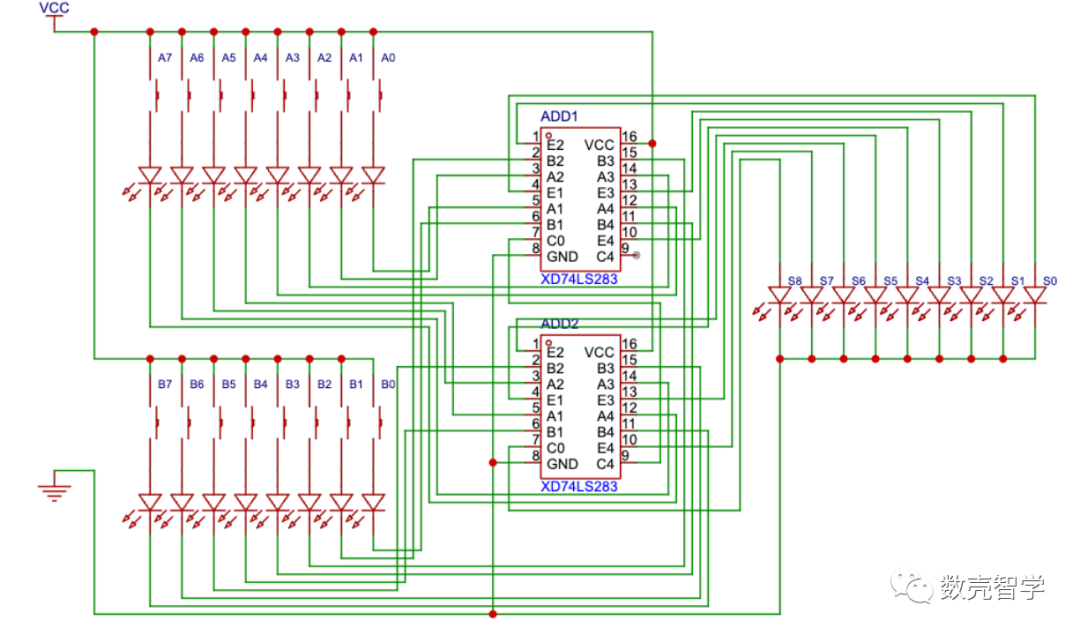

本實驗采用常用的4位加法器芯片(XD74LS283)(如圖 3-8)實現兩個8位二進制相加的實際電路。

圖 3-9八位加法實驗電路圖

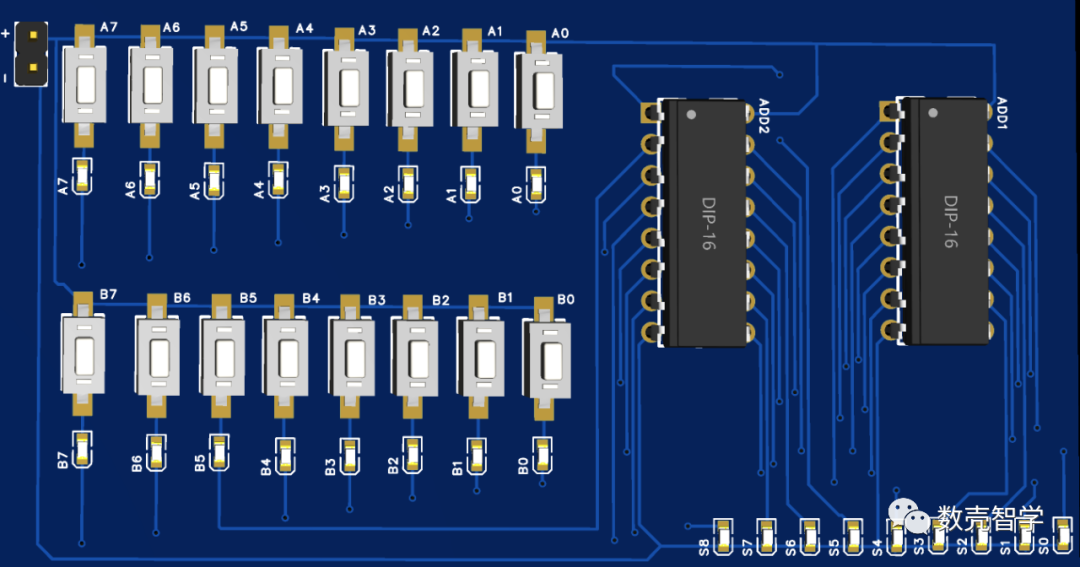

圖 3-10 八位加法實驗板

3.5. 小節

本節通過完整的闡述了加法器這個電子元件的電路設計過程,從元件功能需求分析到邏輯表達式的建立到邏輯電路圖的設計。

-

邏輯電路

+關注

關注

13文章

494瀏覽量

42621 -

電路設計

+關注

關注

6674文章

2453瀏覽量

204361 -

二進制

+關注

關注

2文章

795瀏覽量

41652 -

計算機

+關注

關注

19文章

7494瀏覽量

87954 -

加法器

+關注

關注

6文章

183瀏覽量

30125

發布評論請先 登錄

相關推薦

十進制加法器,十進制加法器工作原理是什么?

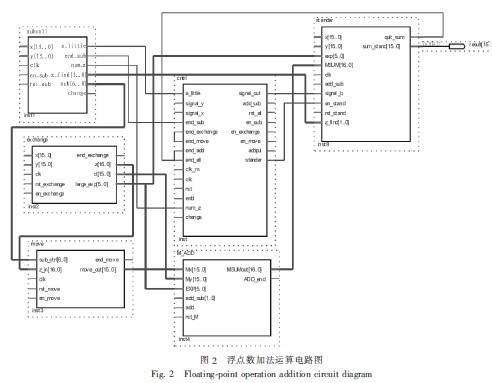

FPU加法器的設計與實現

同相加法器電路原理與同相加法器計算

加法器工作原理_加法器邏輯電路圖

加法器電路設計過程

加法器電路設計過程

評論