鎖相環(huán)性能度量標(biāo)準(zhǔn)包括品質(zhì)因數(shù)、噪聲基底、閃爍噪聲模型。

一個(gè)理想鎖相振蕩器的相位噪聲主要取決于以下因素:

a.VCO的頻率和鑒相器;

b.VCO的靈敏度kvco、VCO和參考振蕩器相位噪聲曲線;

c.電荷泵電流、環(huán)路濾波器和環(huán)路帶寬;

d.工作模式:整數(shù)、小數(shù)調(diào)制樣式。

(1)PLL相位噪聲

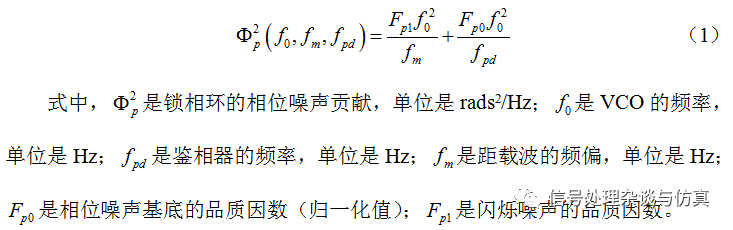

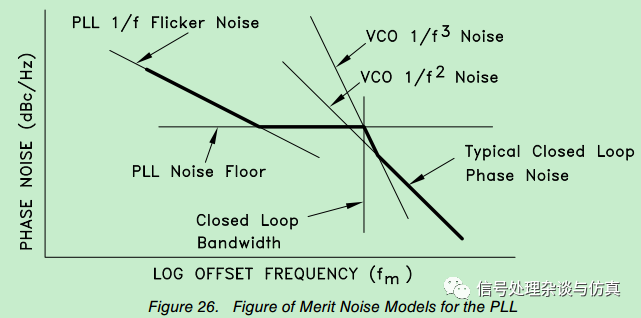

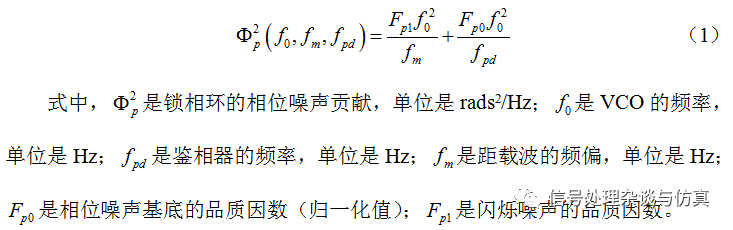

鎖相環(huán)對(duì)輸出相位噪聲的貢獻(xiàn)可以用PLL噪聲基底及PLL閃爍噪聲(又叫1/f噪聲)的品質(zhì)因數(shù)來(lái)表征,見(jiàn)下式(1):

?

?

?

?

?

?

?

?

(3)品質(zhì)因數(shù)的計(jì)算方法

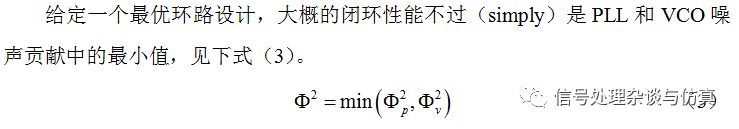

品質(zhì)因數(shù)(FOM)本質(zhì)上是PLL和VCO的歸一化噪聲參數(shù),它有助于快速評(píng)估PLL在所要求的VCO、頻偏及鑒相器頻率下的性能水平。一般來(lái)說(shuō),合成器在閉環(huán)帶寬內(nèi)以PLL IC噪聲為主;在環(huán)路帶寬外(在遠(yuǎn)離載頻的頻偏)以VCO開環(huán)相位噪聲為主。因此,通過(guò)將環(huán)路帶寬設(shè)置為PLL相位噪聲曲線與VCO自由運(yùn)行相位噪聲曲線相交點(diǎn)對(duì)應(yīng)的頻率值【即PLL相位噪聲曲線與VCO開環(huán)相位噪聲曲線相交于一點(diǎn),環(huán)路帶寬等于該點(diǎn)對(duì)應(yīng)的頻率】,來(lái)快速評(píng)估PLL的閉環(huán)性能。

品質(zhì)因數(shù)在估計(jì)噪聲參數(shù)時(shí)也有用,這些噪聲參數(shù)會(huì)輸入到閉環(huán)設(shè)計(jì)工具(比如Hittite PLL Design),Hittite PLL Design工具能夠給出關(guān)于閉環(huán)相位噪聲的更準(zhǔn)確評(píng)估,以及PLL環(huán)路濾波器的元件值。

-

鎖相環(huán)

+關(guān)注

關(guān)注

35文章

584瀏覽量

87767 -

振蕩器

+關(guān)注

關(guān)注

28文章

3832瀏覽量

139088 -

pll

+關(guān)注

關(guān)注

6文章

776瀏覽量

135160 -

VCO

+關(guān)注

關(guān)注

12文章

190瀏覽量

69194

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

什么是鎖相環(huán) 鎖相環(huán)的組成 鎖相環(huán)選型原則有哪些呢?

軟件鎖相環(huán)的設(shè)計(jì)與應(yīng)用

鎖相環(huán)原理

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

模擬鎖相環(huán),模擬鎖相環(huán)原理解析

射頻鎖相環(huán)基礎(chǔ)

鎖相環(huán)

鎖相環(huán)性能度量標(biāo)準(zhǔn)解讀

鎖相環(huán)性能度量標(biāo)準(zhǔn)解讀

評(píng)論