使用Cache的必要性

所謂Cache即高速緩沖存儲器,它位于CPU與主存即DRAM之間,是通常由SRAM構成的規模較小但存取速度很快的存儲器。

目前計算機主要使用的內存為DRAM,它具有價格低、容量大等特點,但由于使用電容存儲信息,存取速度難以提高,而CPU每執行一條指令都要訪問一次或多次主存,DRAM的讀寫速度遠低于CPU速度,因此為了實現速度上的匹配,只能在CPU指令周期中插入wait狀態,高速CPU處于等待狀態將大大降低系統的執行效率。

由于SRAM采用了與CPU相同的制作工藝,因此與DRAM相比,它的存取速度快,但體積大、功耗大、價格高,不可能也不必要將所有的內存都采用SRAM。

因此為了解決速度與成本的矛盾就產生了一種分級處理的方法,即在主存和CPU之間加裝一個容量相對較小的SRAM作為高速緩沖存儲器。

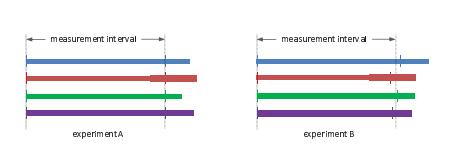

當采用Cache后,在Cache中保存著主存中部分內容的副本(稱為存儲器映像),CPU在讀寫數據時,首先訪問Cache(由于Cache的速度與CPU相當,所以CPU可以在零等待狀態下完成指令的執行),只有當Cache中無CPU所需的數據時(這稱之“未命中”,否則稱為“命中”),CPU才去訪問主存。

而目前大容量Cache能使CPU訪問Cache命中率高達90%~98%,從而大大提高了CPU訪問數據的速度,提高了系統的性能。

使用Cache的可行性

對大量的典型程序的運行情況分析結果表明,在一個較短的時間內,由程序產生的地址往往集中在存儲器邏輯地址空間的很小范圍內。

在多數情況下,指令是順序執行的,因此指令地址的分布就是連續的,再加上循環程序段和子程序段要重復執行多次,因此對這些地址的訪問就自然具有時間上集中分布的趨向。

數據的這種集中傾向不如指令明顯,但對數組的訪問以及工作單元的選擇都可以使存儲器地址相對集中。這種對局部范圍的存儲器地址的頻繁訪問,而對此范圍以外的地址則訪問甚少的現象稱為程序訪問的局部性。

根據程序的局部性原理,在主存和CPU之間設置Cache,把正在執行的指令地址附近的一部分指令或數據從主存裝入Cache中,供CPU在一段時間內使用,是完全可行的。

-

存儲器

+關注

關注

38文章

7492瀏覽量

163843 -

數據

+關注

關注

8文章

7033瀏覽量

89040 -

內存

+關注

關注

8文章

3025瀏覽量

74056 -

Cache

+關注

關注

0文章

129瀏覽量

28346

發布評論請先 登錄

相關推薦

使用Cache的必要性與可行性

使用Cache的必要性與可行性

評論