AXI的控制和數據通道分離,可以帶來很多好處。地址和控制信息相對數據的相位獨立,可以先發地址,然后再是數據,這樣自然而然的支持顯著操作,也就是outstanding 操作。

Master訪問slave的時候,可以不等需要的操作完成,就發出下一個操作。這樣,可以讓slave在控制流的處理上流水起來,達到提速的作 用。

同時對于master,也許需要對不同的地址和slave就行訪問,所以可以對不同的slave 連續操作。而這樣的操作,由于slave返回數據的先后可能不按照master 發出控制的先后進行,導致出現了亂序操作(out of order )。

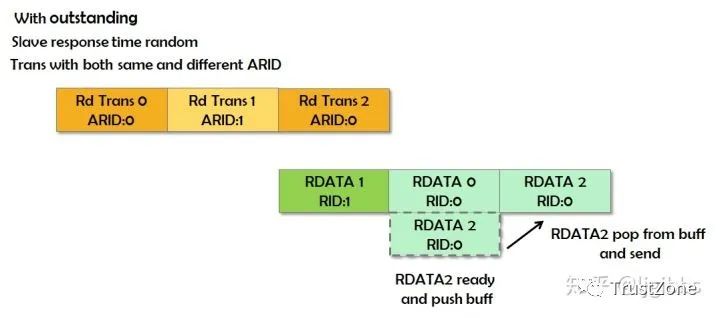

亂序傳輸需要依賴ARID來完成,亂序傳輸是針對transaction而言的,可以認為ARID是transaction的ID。

若支持亂序傳輸,當存在多個transaction時,從機可以不按照transaction的發起順序進行返回數據,主機通過從機返回的BID(寫)或RID(讀)來判斷返回的數據屬于哪個transaction。

另外,擁有相同AWID與ARID的transaction,其返回數據需要按照transaction發起的順序進行返回數據。亂序傳輸的數據傳輸過程如下圖所示:

interleaving 交織

寫交織使用WID來實現,interleaving用來實現不同transaction中的beat的交替傳輸,但同一transaction的beat是需要按照順序進行傳輸的。

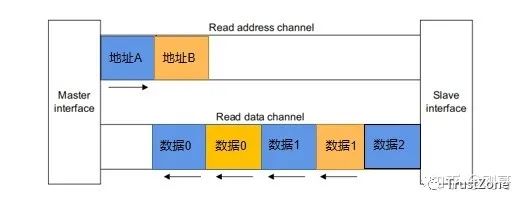

AXI4中已經取消了WID信號的使用,不再支持寫交織。interleaving的輸出傳輸過程如下:

其中數據0與數據1屬于同一transaction的不同beat,地址A與地址B表示兩個transaction。

關于AXI4不支持寫交織是一個非常自然地過程。為了提高效率,AXI總線的寫數據通道并不依賴寫地址通道,這就是說,寫數據可以先于寫地址發送,但是總線不知道寫地址,沒辦法將數據發送出去,只能暫存在buffer中,等待寫地址。比較理想的方案是總線為每個master預留一個寫地址通道buffer和寫數據通道buffer。

在這種方案下,若支持寫交織,地址通道buffer和數據通道buffer的數據可能永遠都對不上(AWID與WID),這會造成該master的所有數據都被堵塞。當然可以采用其他方案來解決這個問題,比如說為每個master分配多個buffer,但實現起來會比較復雜。

合理地設計可以減少寫交織被取消帶來的影響,master應該在某個transaction的數據準備好之后再向總線發起寫請求,否則mater可能長時間占用總線,大大降低總線的效率。因此,設計人員本就應該避免寫交織十分高效時的場景,設計合理的情況下,寫交織的取消并不會給系統帶來明顯的效率影響。

-

數據

+關注

關注

8文章

7102瀏覽量

89274 -

總線

+關注

關注

10文章

2894瀏覽量

88214 -

通道

+關注

關注

0文章

59瀏覽量

20383 -

AXI

+關注

關注

1文章

128瀏覽量

16667

發布評論請先 登錄

相關推薦

解讀AXI總線系統中的多交易操作應用

玩轉Zynq連載3——AXI總線協議介紹1

AXI接口協議詳解

看看Axi4寫通道decoder的設計

AMBA AXI協議指南

AXI 總線和引腳的介紹

AXI的控制和數據通道分離

AXI的控制和數據通道分離

評論