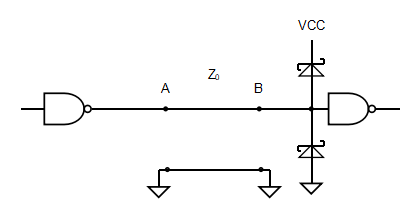

(3)戴維 南 ( 寧 )端接

上拉端接會拉高低電平,下拉端接會降低高電平,這兩種端接方式雖然都可以抑制過沖和振鈴,但同時也會減小信號裕量,如果使用不當還會造成信號電平的誤觸發。戴維南端接方式既可以抑制過沖,又沒有這些缺陷。缺點就是在邏輯高和邏輯低狀態下, 都有直流功耗 ,所以該端接方式 功耗較大 ,同時所用器件 較多,容易造成PCB布線緊張。

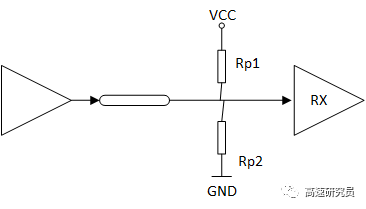

工作原理:

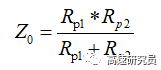

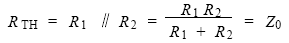

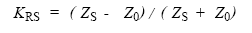

它采用上拉電阻R1和下拉電阻R2構成端接電阻,通過R1和R2吸收反射。R1和R2阻值的選取由下面的條件決定。R1的最大值由可接受的信號的最大上升時間(是RC充放電時間常數的函數)決定,R1的最小值由驅動源的吸電流數值決定。R2的選擇應滿足當傳輸線斷開時電路邏輯高電平的要求。戴維南等效阻抗可表示為:

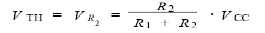

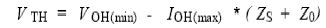

戴維南電壓 為:

為:

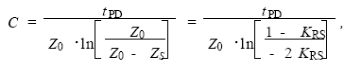

的選擇必須確保驅動器的輸出高電平IOH和低電平的IOL電流在驅動器的性能指標范圍以內,其值可按下式確定

的選擇必須確保驅動器的輸出高電平IOH和低電平的IOL電流在驅動器的性能指標范圍以內,其值可按下式確定

所以,可得到:

R1的作用是幫助驅動器更加容易到達邏輯高狀態,這就需通過從VCC向負載注入電流來實現. R2的作用是幫助驅動器更加容易到達邏輯低狀態,這通過R2 向地釋放電流來實現。

恰當地選取R1和R2的值可以加強驅動器的輸出能力,并且淡化由于信號占空比不一致而導致的功耗的改變。

戴維南終端匹配技術的優點在于,在這種匹配方式下,終端匹配電阻同時還作為上拉電阻和下拉電阻來使用,因而 提高了系統的噪聲容限 ,通過向負載提供額外的電流從而降低了對源端器件驅動能力的要求。適用于分布式負載;可以完全吸收發送波,消除反射。這種方案能夠 很好地抑制過沖 。

戴維南終端匹配的缺點就是無論邏輯狀態是高還是低,在VCC到地之間都會有一個常量的直流電流存在,因而會導致終端匹配電阻中有 靜態的直流功耗 .信號負載為電容時,相對于沒有匹配的信號線而言,戴維南終端匹配技術同樣會改善信號的質量,使得信號的擺動縮小。

另外,戴維寧端接減小了接容性負載時信號的斜率( 電容充放電導致上升/下降沿變緩 ), 容性負載和電阻增加了RC時間常數 ,導致了 驅動器輸出電壓的上升 。簡言之:增加系統電路功耗;使用兩個電阻,布局布線難度大;阻值不易選擇。

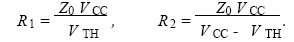

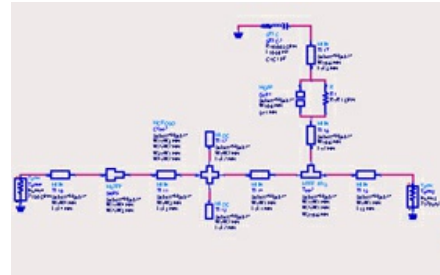

(4)AC端接

有些地方也叫 RC端接 ,其實就是在并聯端接的基礎上增加了一個電容,電容一般采用0.1uF多層陶瓷電容,由于電容通低頻阻高頻的作用,因此電阻不是驅動源的直流負載,故這種端接方式 無任何直流功耗 ,交流功耗也非常小,該端接主要用于時鐘電路。

需注意,此RC電路可能會因此 電路上升沿變緩 ,雖然會降低EMC,但如果過緩,則會引起數據線 時序問題 。在數據線上使用這種電路時,需特別小心。

工作原理:

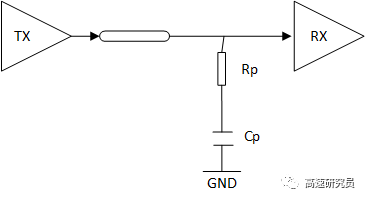

端接電阻 R要小于等于傳輸線阻抗Z0(常見40-50歐姆) ,電容C推薦使用0.1uF的多層陶瓷電容。

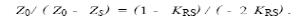

所以有:

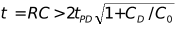

可見電容C的選擇很復雜. 電容值太小會導致RC 時間常數過小,這樣一來該RC 電路就類似于一個尖銳信號沿發生器,從而引入信號的過沖與下沖,一般高速電路電容值10-100pF. 另一方面,較大的電容值會帶來更大的功率消耗. 通常情況下,要確保RC時間常數大于該傳輸線負載延時的兩倍,即

,

,

其中: 為接收器的分布電容,

為接收器的分布電容, 為PCB 傳輸線的內在電容.

為PCB 傳輸線的內在電容.

理想的電容值將隨著傳輸線阻抗,邊沿速率,預期的信號質量的變化而變化。這個值不是最關鍵的,但是測試表明,對于FCT邏輯,100PF的電容值能夠得到很好的折衷,將電容值增加到200PF會改善信號的質量,但是卻以功率損耗為代價。把電容值減小到47PF,降低了功率損耗,但是信號的質量會變差。值低于47PF會對濾波有非常高的頻率響應,對傳輸線的端接是無效的。值高于200PF,會增加功率損耗而不會有附加的信號質量的改善。

RC 終端匹配技術的優勢在于終端匹配電容阻隔了直流通路,因此節省了較大的功率消耗( 直流功耗低 ). 同時恰當地選取匹配電容的值,可以確保負載端的信號波形 接近理想的方波 ,而信號的過沖與下沖又都很小.適用于分布式及總線型負載,完全吸收發送波,消除反射;

RC 終端匹配技術的一個缺點是信號線上的數據可能出現 時間上的抖動(時序問題) . 標準的RS2422 接口協議不建議使用RC 終端匹配技術. 同樣,電流模式的驅動器也不能采用RC 終端匹配技術.另外,RC端接的性能依賴于傳輸線的長度,RC端接不適合于在傳輸線上有多源分布的情況。

另外RC終端匹配易降低信號速率, 增加延時,上升沿變緩; RC時間常數會導致電路中存在反射;高頻、高速慎用;兩個器件,布局布線難度大,成本高。

(5)終端肖特基并聯端接

又叫二極管并聯端接,通常應用在器件內部(電壓箝位,保護器件 )。

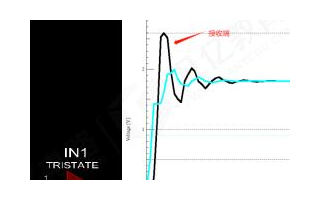

傳輸線末端任何的信號反射,如果導致接收器輸入端上的電壓超過VCC和二極管的正向偏值電壓,該二極管就會正向導通連接到VCC上。該二極管導通從而將信號的過沖箝位到VCC和二極管的閾值電壓的和上。

同樣連接到地上的二極管也可以將信號的下沖限制在二極管的正向偏置電壓上。然而該二極管不會吸收任何的能量,而僅僅只是將能量導向電源或者是地。這種工作方式的結果是,傳輸線上就會出現多次的信號反射。

信號的反射會逐漸衰減,主要是因為能量會通過二極管在電源和地之間實現能量的交換,以及傳輸線上的 電阻性損耗 。能量的損耗限制了信號反射的幅度,確保信號的完整性。

現在很多器件自帶有輸入保護二極管,該端接能有效減小信號過沖和下沖,但并不能消除反射( 只是降幅 );同時 二極管的開關速度會限制響應時間 ,所以較高速系統不合適。

某些情況可以使用肖特基二極管或快速開關硅管進行傳輸線端接,條件是 二極管的開關速度必須至少比信號上升時間快4倍以上(肖特基響應速度約10ns,普通二極管400ns) 。在面包板和底板等線阻抗不好確定的情況下,使用二極管端接即方便又省時。如果在系統調試時發現振鈴問題,可以很容易地加入二極管來消除。

典型的二極管端接如上圖所示。肖特基二極管的低正向電壓降Vf(典型0.3到0.45V)將輸入信號鉗位到GROUND-Vf和VCC+Vf之間。這樣就顯著減小了信號的過沖(正尖峰)和下沖(負尖峰)。在某些應用中也可只用一個二極管。

二極管端接的優點在于:二極管替換了需要電阻和電容元件的戴維寧端接或RC端接,通過二極管鉗位減小過沖與下沖 ,不需要進行線的阻抗匹配 。盡管二極管的價格要高于電阻,但系統整體的布局布線開銷也許會減少,因為不再需要考慮精確控制傳輸線的阻抗匹配。且 功耗小,當傳輸線的特征阻抗Z0不清楚時,比較適合采用這種終端匹配技術 。

二極管端接的缺點在于:二極管的開關速度一般很難做到很快,因此對于較 高速的系統不適用 。因為存在多點反射會影響相應的信號激勵,二極管對轉換頻率的響應會發生變化。肖特基二極管對于3.3V和5V的邏輯族是有效的( 1.8V及以下信號幾乎沒有作用 )。

(6)ODT芯片內部端接匹配;

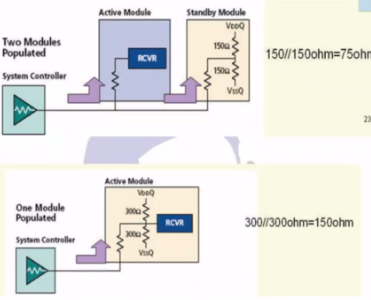

DDR內部有ODT的控制電阻,用來做匹配;芯片內端接是在器件內部實現端接匹配的要求,通常是終端并聯匹配。器件內部可以備用幾種可選的匹配電阻值以根據實際設計需求進行選擇。

(1)優點:不需要外部器件,易于布線。

(2)缺點:匹配電阻是器件已經決定的。增加了器件的功耗。同戴維南端接,電阻值選取需要綜合考慮電平幅度與阻抗的控制。

-

驅動器

+關注

關注

52文章

8237瀏覽量

146369 -

阻抗匹配

+關注

關注

14文章

353瀏覽量

30810 -

傳輸線

+關注

關注

0文章

376瀏覽量

24034 -

時鐘電路

+關注

關注

10文章

236瀏覽量

50727 -

負載電容

+關注

關注

0文章

139瀏覽量

10441

發布評論請先 登錄

相關推薦

傳輸線在阻抗匹配時串聯端接電阻為什么要靠近發送端

淺析阻抗匹配及其應用

傳輸線阻抗匹配

微帶傳輸線阻抗匹配應用經驗

ps脈沖傳輸線的多容性負載阻抗匹配模型和計算

微帶傳輸線阻抗匹配電路設計

淺談阻抗匹配(六)傳輸線端接的工作原理

淺談阻抗匹配(六)傳輸線端接的工作原理

評論