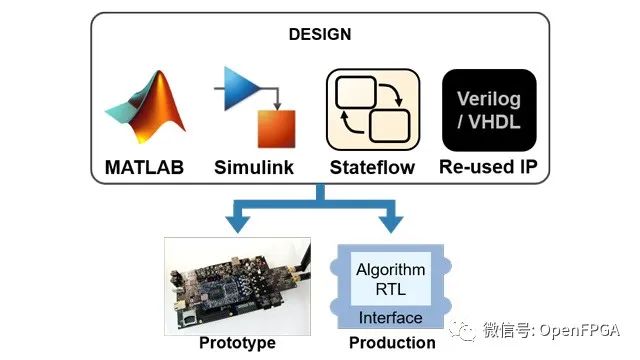

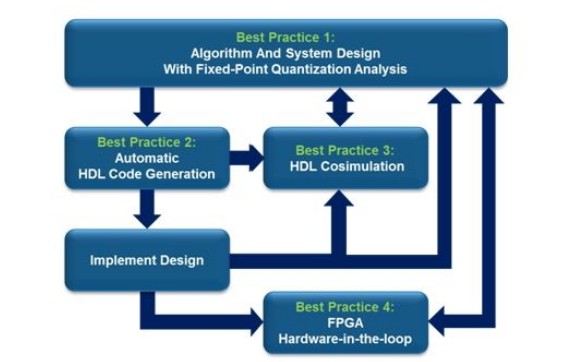

我們將使用實(shí)例講解MATLAB / Simulink HDL 使用入門。

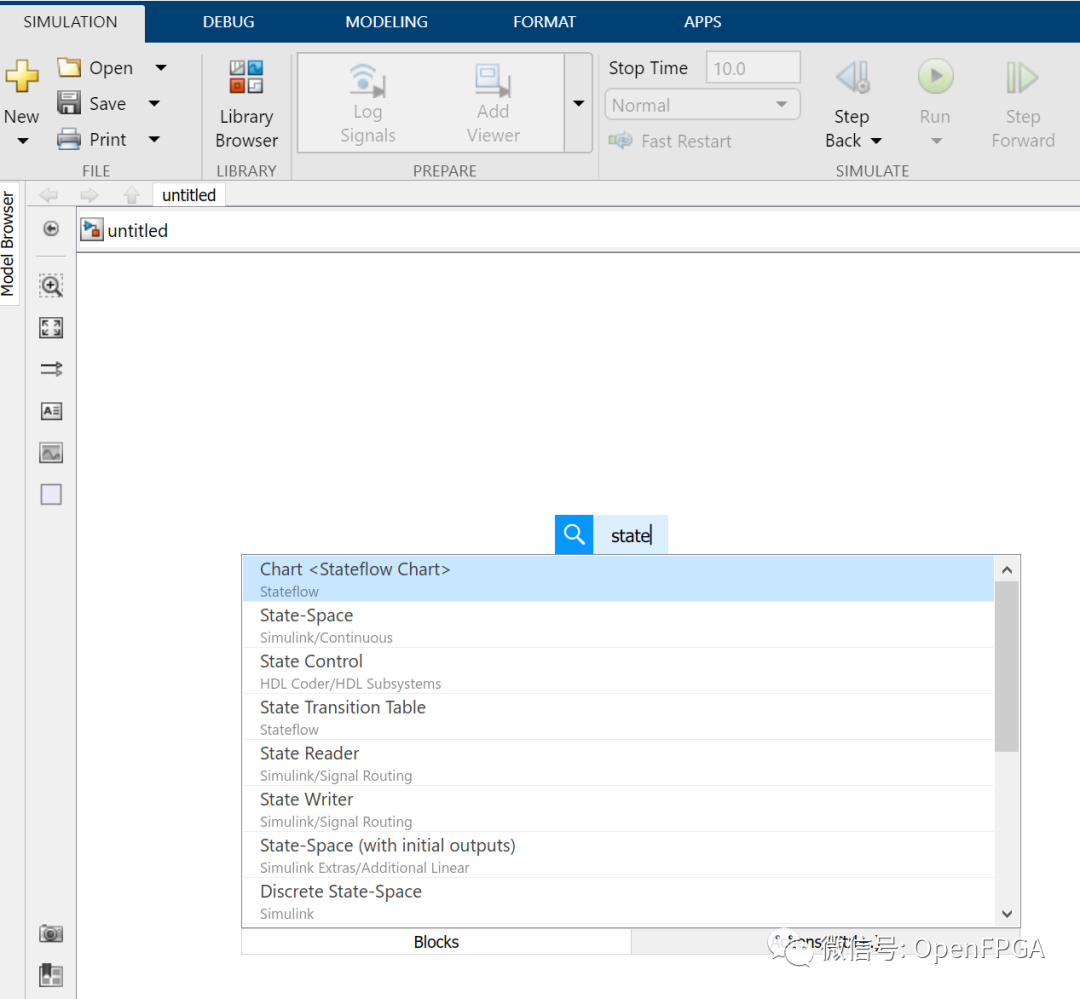

開(kāi)始這個(gè)項(xiàng)目,首先需要?jiǎng)?chuàng)建一個(gè)包含 Stateflow 的新 Simulink 。只需單擊畫(huà)布中的任意位置并開(kāi)始輸入 Stateflow。

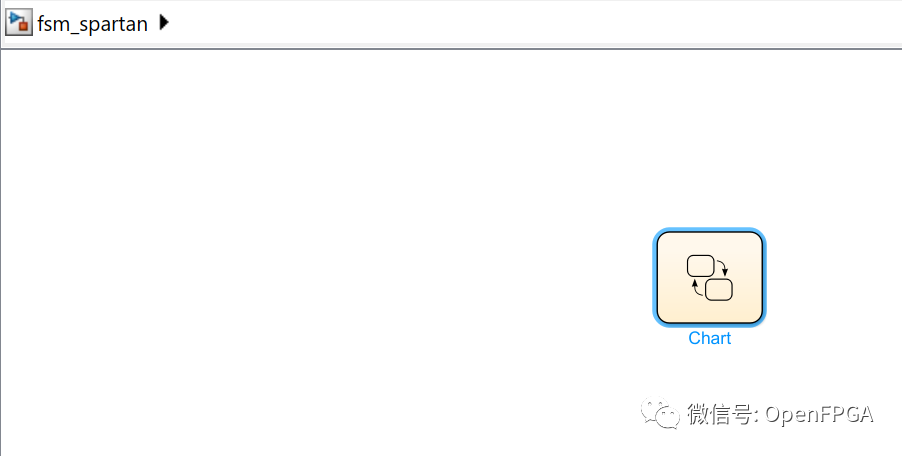

此時(shí)應(yīng)該能在畫(huà)布上看到 Stateflow 圖標(biāo)。雙擊圖標(biāo)進(jìn)行編輯。

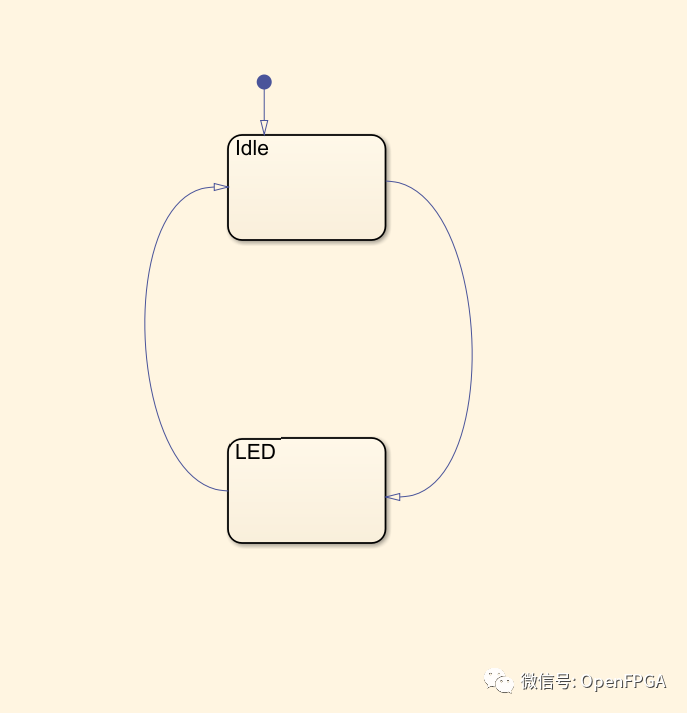

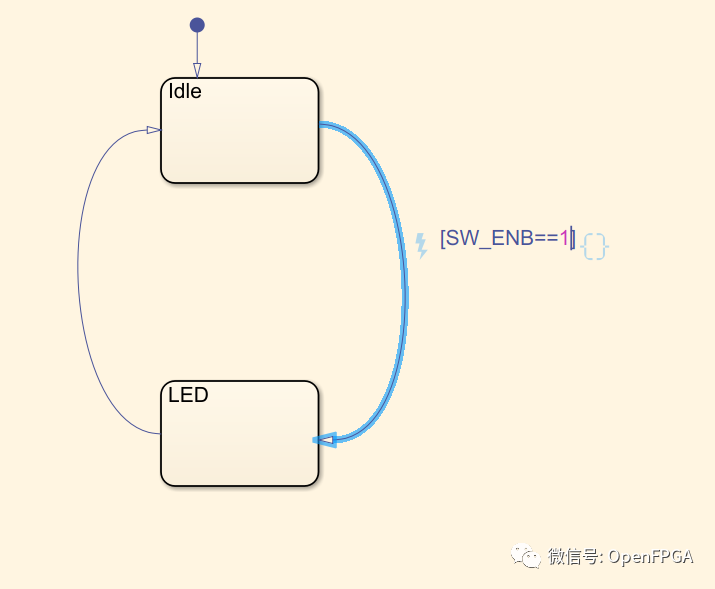

進(jìn)入圖表編輯器后,可以添加狀態(tài)以及狀態(tài)之間的轉(zhuǎn)換。開(kāi)始,我們創(chuàng)建兩種狀態(tài)并將它們命名為“idle”和“LED”。它們之間的轉(zhuǎn)換還沒(méi)有任何條件。

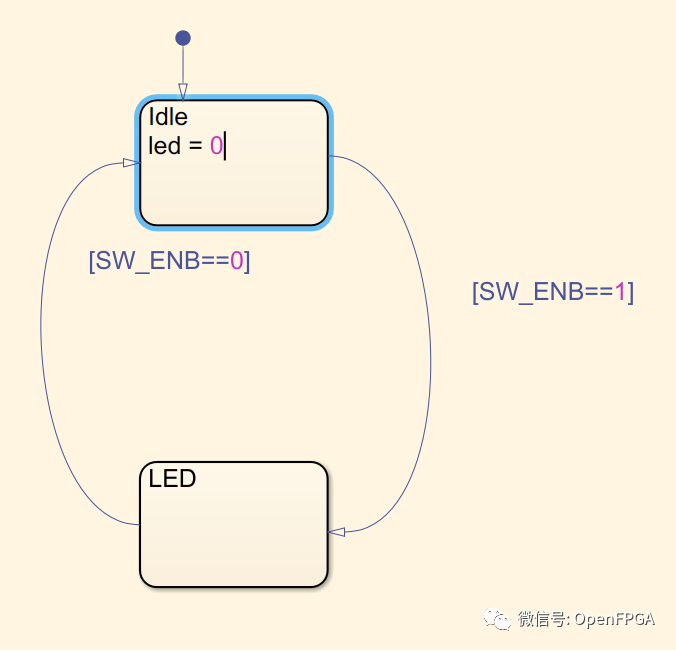

要添加狀態(tài)轉(zhuǎn)換條件,可以雙擊轉(zhuǎn)換并輸入所需的條件。

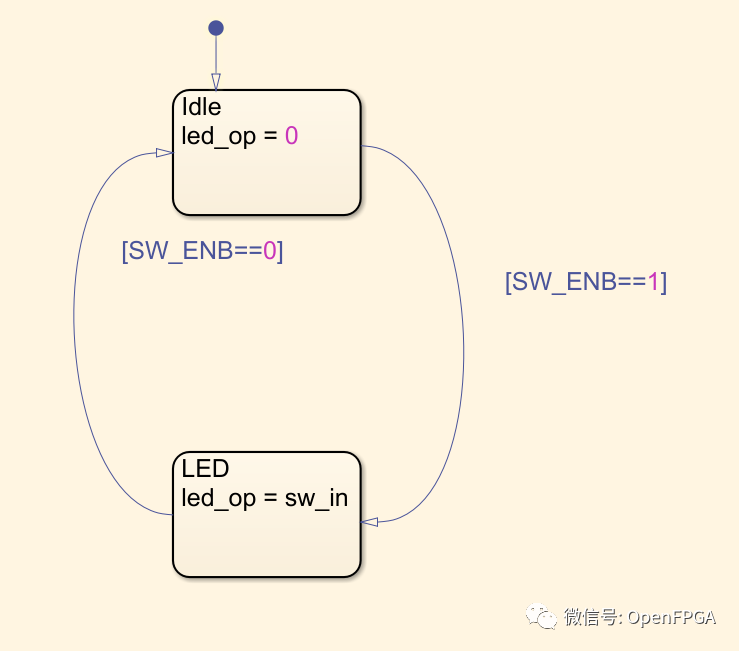

當(dāng)然,狀態(tài)機(jī)可以具有 Mealey 和 Moore 輸出,這些輸出作為當(dāng)前狀態(tài) (Moore) 或當(dāng)前狀態(tài)和輸入 (Mealey) 的函數(shù)出現(xiàn)。在本例中,將 LED 輸出聲明為 Moore 輸出,并在每個(gè)狀態(tài)下聲明。

最終的結(jié)果如下所示。

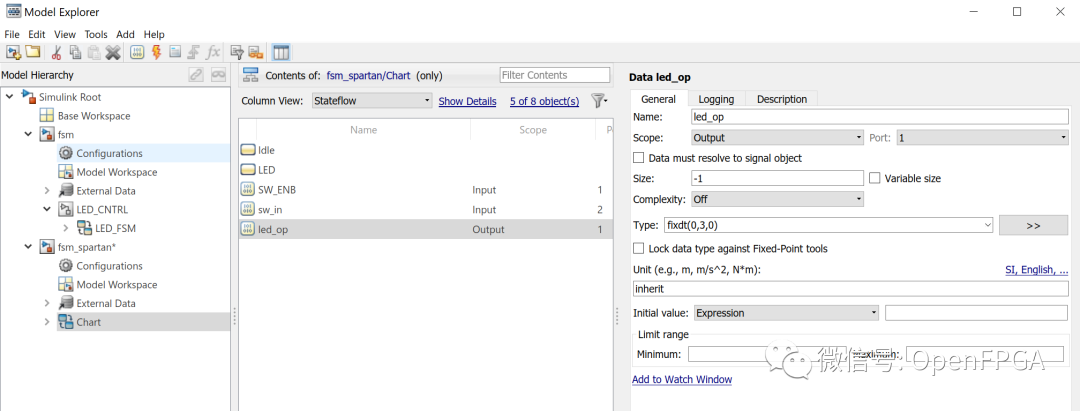

使用模型瀏覽器,我們可以定義狀態(tài)機(jī)的輸入和輸出。對(duì)于輸入,我們將它們保留為與 Simulink 相同的類型,但需要定義輸出。由于 LED 需要三位,因此我們使用類型 fixdt(0,3,0)。這意味著向量是三位寬、無(wú)符號(hào)的,并且沒(méi)有數(shù)字的小數(shù)元素。

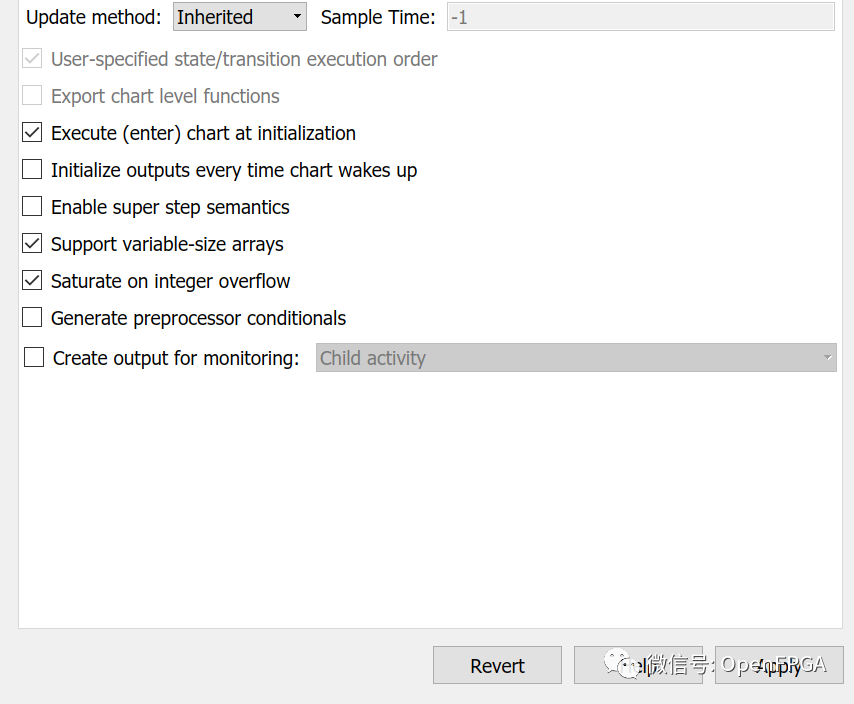

此外,在模型資源管理器中選中“初始化時(shí)執(zhí)行(輸入)圖表”選項(xiàng)。

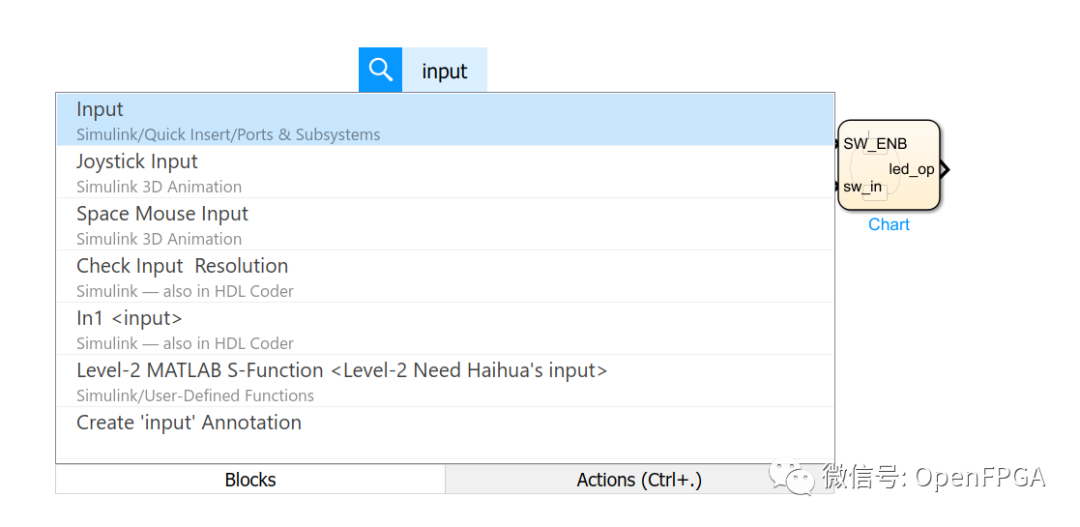

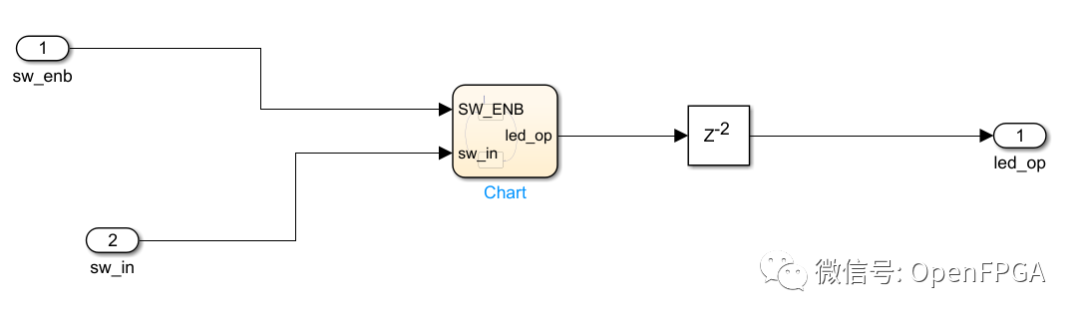

導(dǎo)航到圖表上方的畫(huà)布。這里我們需要添加塊的 IO,我們還將添加延遲。在畫(huà)布中,開(kāi)始輸入輸入或輸出以獲取所需的端口。

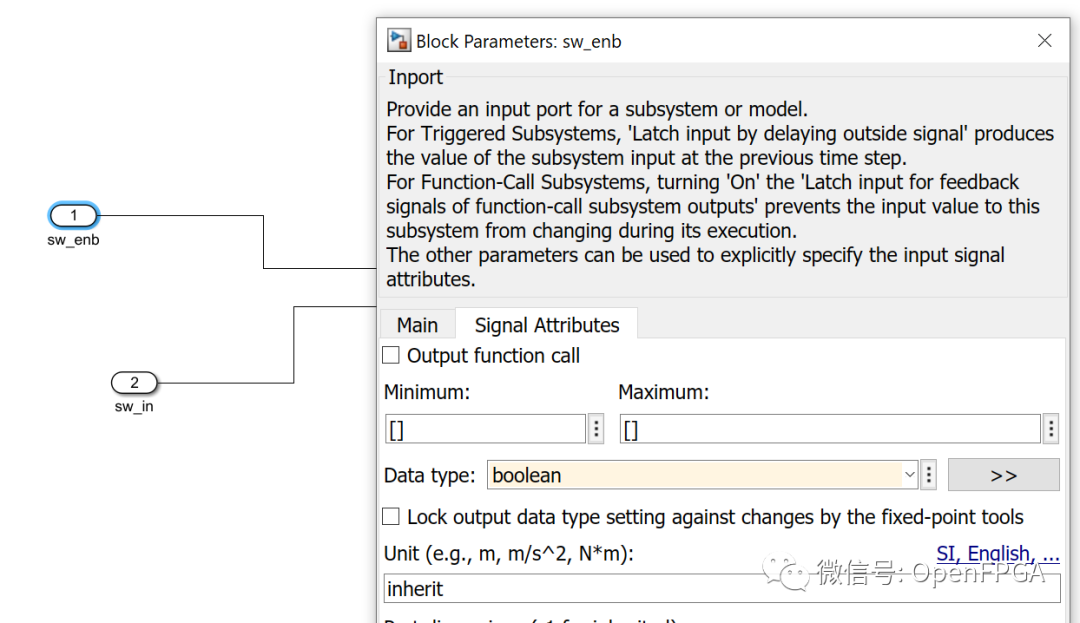

還可以通過(guò)雙擊輸入和輸出來(lái)命名端口,將其設(shè)置為正確的類型。

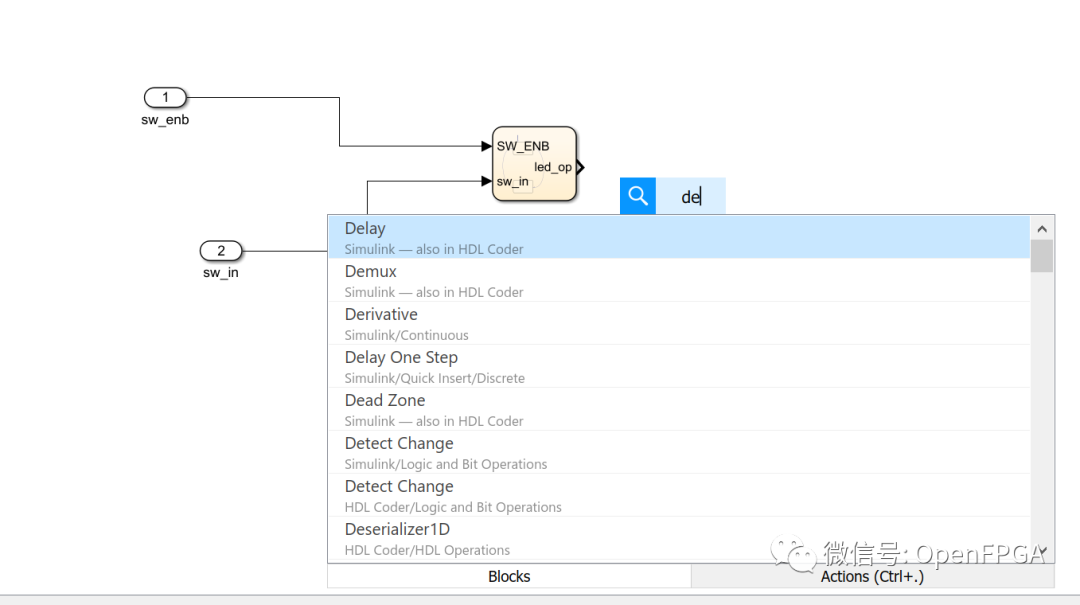

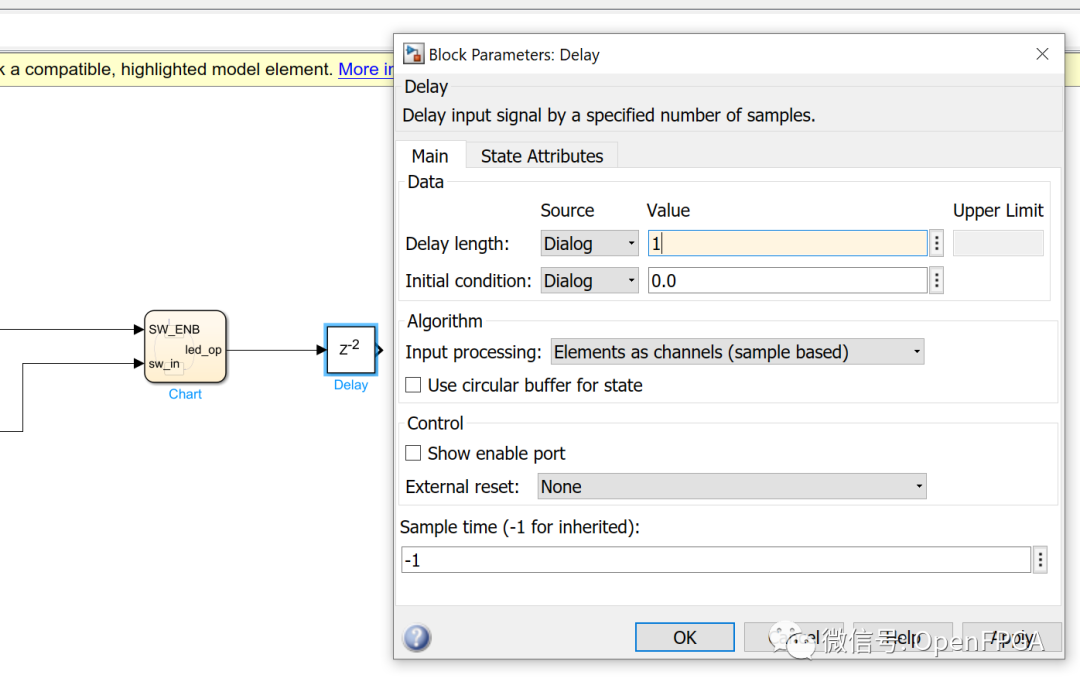

將 sw_in 設(shè)置為與之前聲明的輸出類型相同的 fixdt(0,3,0)。我們使用延遲來(lái)添加寄存器。要添加額外的延遲,只需在畫(huà)布中鍵入即可。

要更改延遲的長(zhǎng)度,雙擊延遲并將其更改為延遲 1。

下圖顯示了完整的圖表。

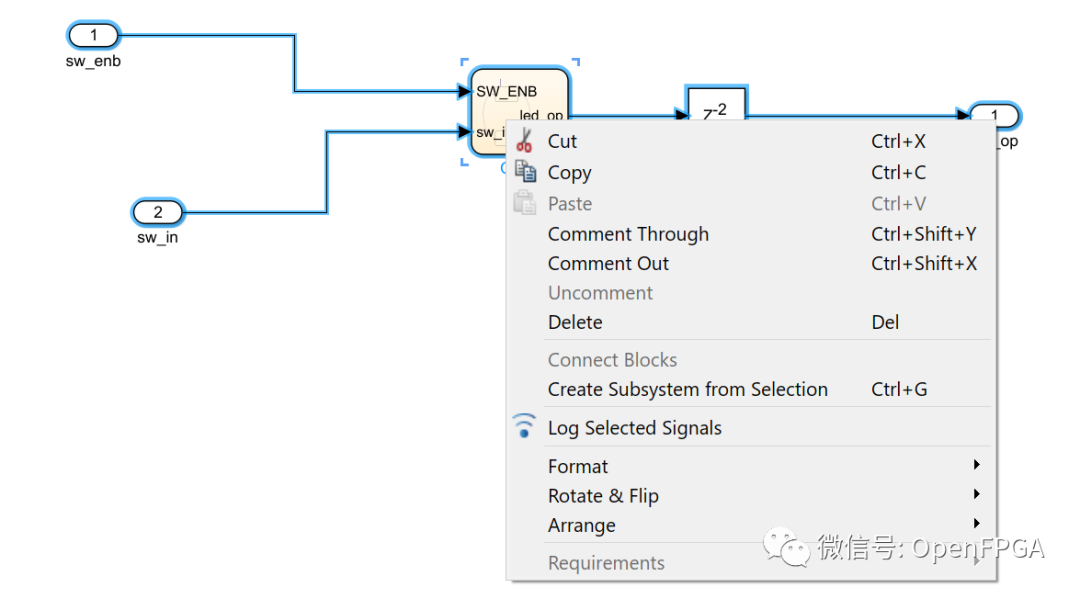

現(xiàn)在我們可以將其生成 RTL,但首先我們將為它創(chuàng)建一個(gè)測(cè)試平臺(tái)。選擇畫(huà)布上的所有元素,右鍵單擊它,然后選擇從選擇創(chuàng)建子系統(tǒng)。

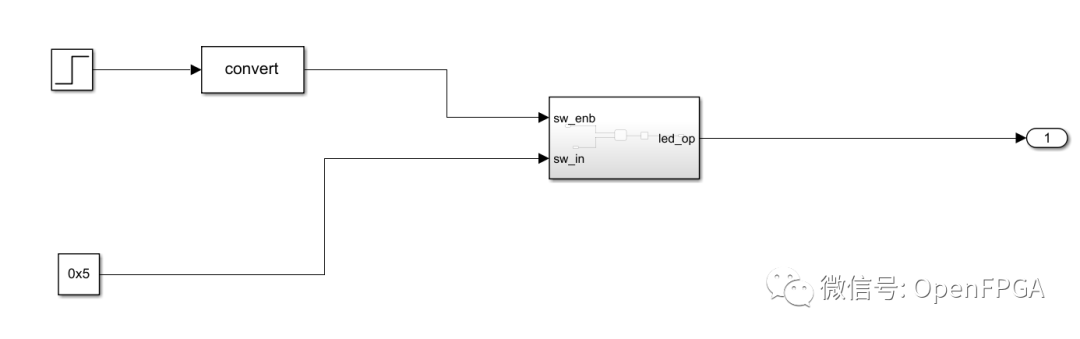

添加階躍函數(shù)和常數(shù),設(shè)置子系統(tǒng)模塊中使用的模塊類型,并確保將離散采樣的采樣時(shí)間設(shè)置為 -1。

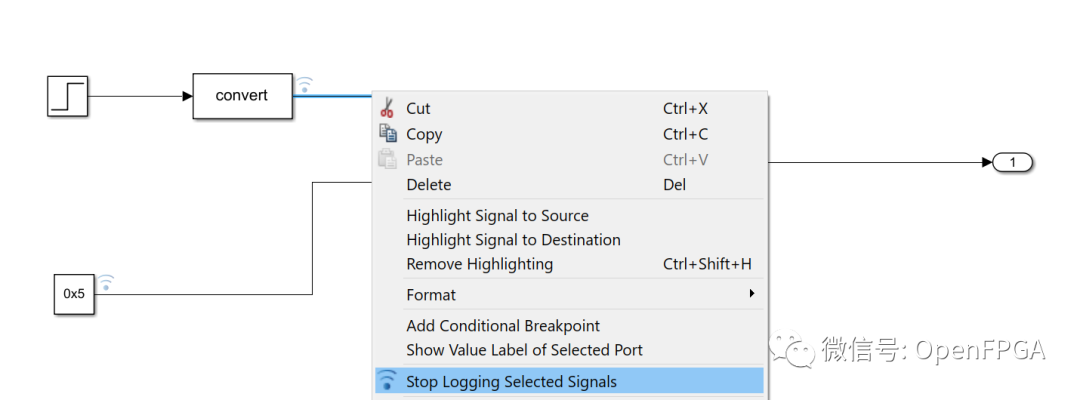

右鍵單擊感興趣的信號(hào)并選擇開(kāi)始記錄所選信號(hào)。

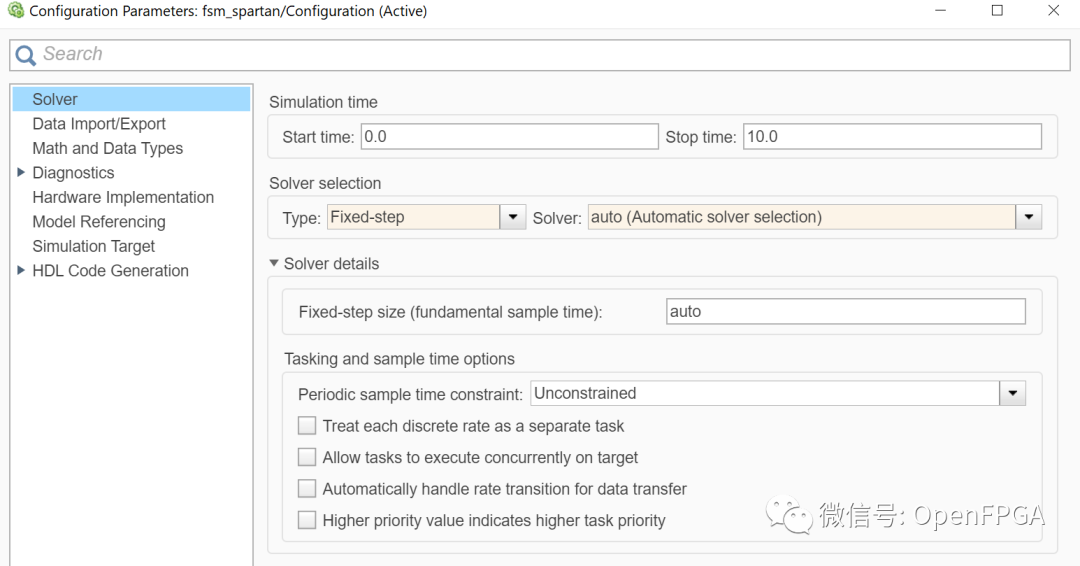

打開(kāi)模型資源管理器并將模型設(shè)置為具有固定步長(zhǎng)的計(jì)時(shí)器的離散時(shí)間。

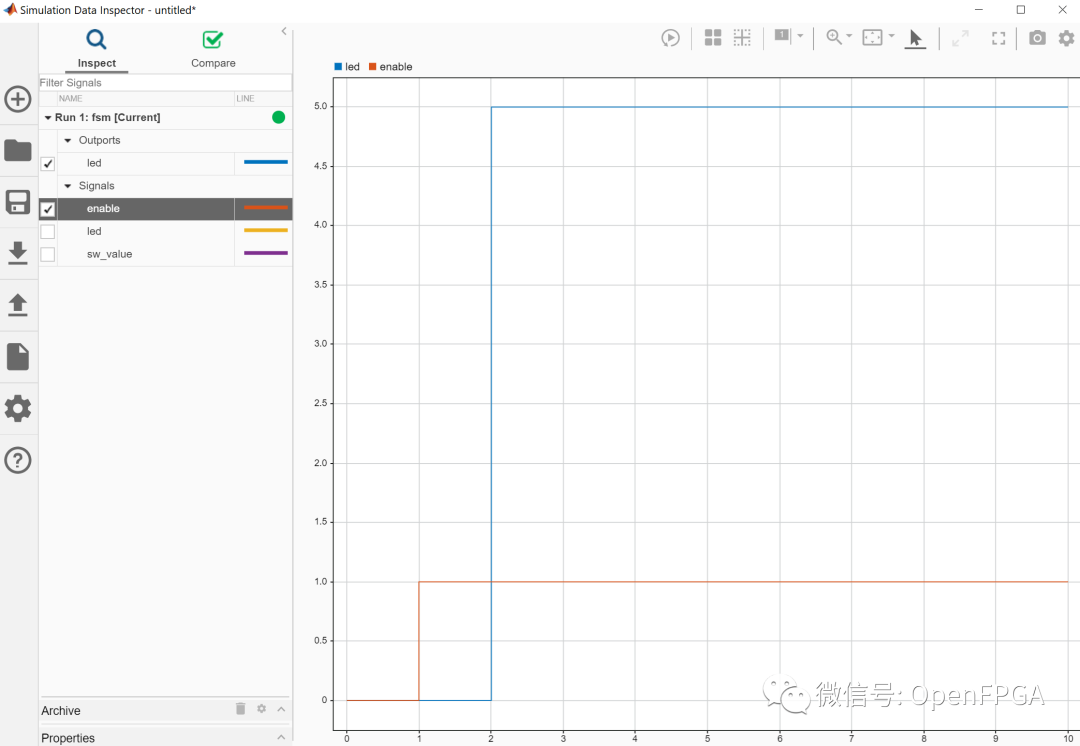

運(yùn)行模擬并打開(kāi)數(shù)據(jù)檢查器。應(yīng)該能夠看到 SW_ENB 被置位,并且 LED 輸出在下一個(gè)時(shí)鐘后變高。

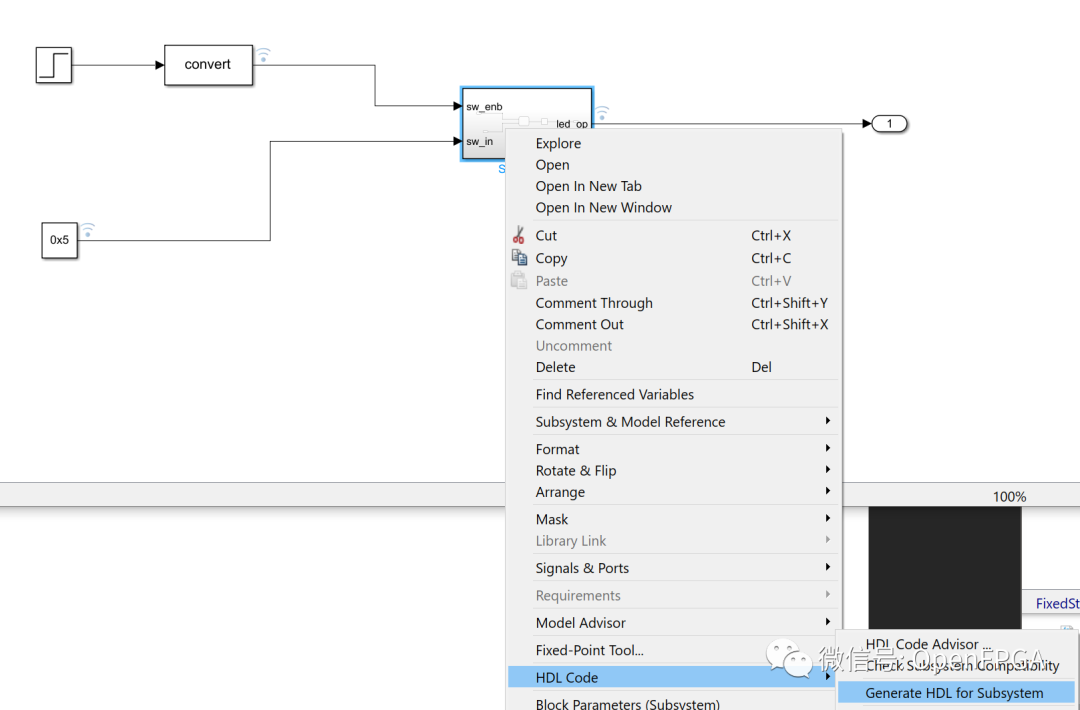

現(xiàn)在我們可以創(chuàng)建 HDL 并將其導(dǎo)出到 Vivado 中使用。我們可以通過(guò)右鍵單擊子系統(tǒng)并選擇為子系統(tǒng)生成 HDL 來(lái)完成此操作。

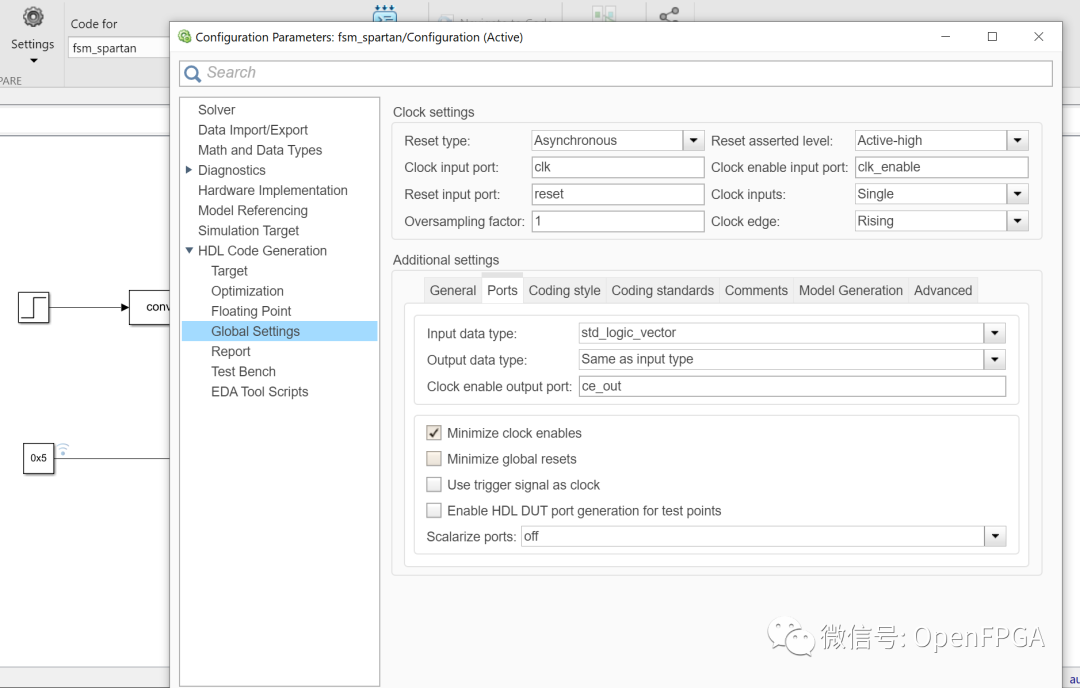

如果要更改任何生成的 HDL 代碼格式(即刪除時(shí)鐘啟用),需要從 HDL 代碼生成選項(xiàng)卡中選擇全局設(shè)置選項(xiàng)。

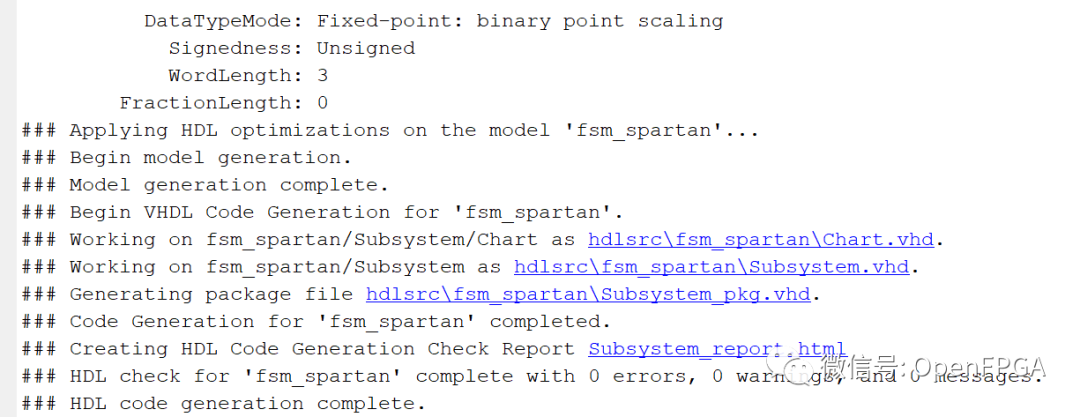

生成代碼后,將在生成代碼的 MATLAB 窗口中看到一條消息。

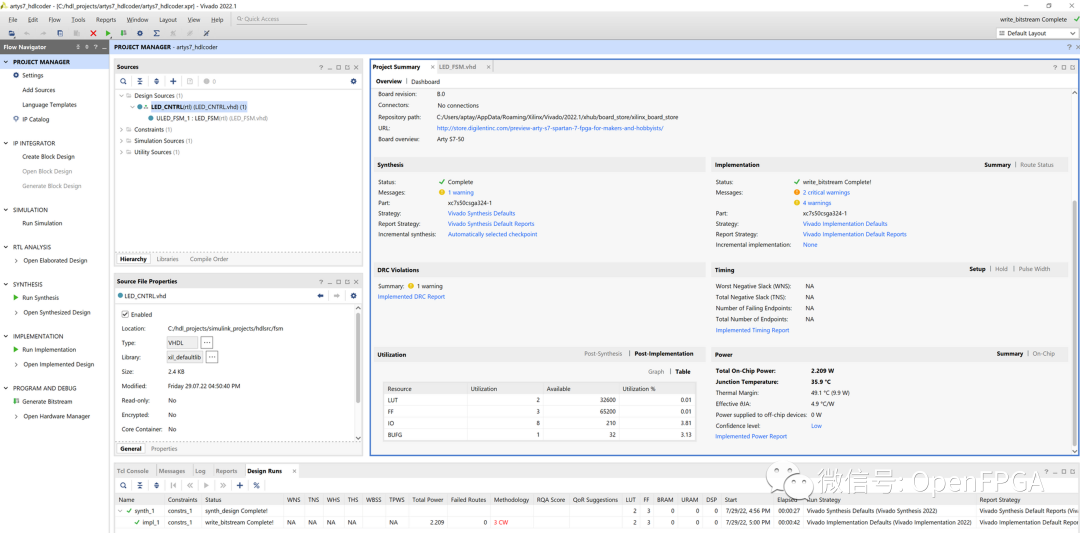

然后可以將該 HDL 導(dǎo)入到 Vivado 項(xiàng)目中。生成的代碼本身實(shí)際上是可讀的,并且取決于我們對(duì) Simulink 圖的注釋程度。例如,我可以命名狀態(tài)圖,這將反映在case語(yǔ)句名稱中。

生成三個(gè) VHDL 文件:包含聲明的包、實(shí)現(xiàn)狀態(tài)機(jī)的實(shí)際源代碼以及頂級(jí)文件。

在 Vivado 中進(jìn)行綜合,最終設(shè)計(jì)需要三個(gè)觸發(fā)器和兩個(gè) LUT。

當(dāng)然,這是一個(gè)簡(jiǎn)單的示例,但能夠?qū)W習(xí)流程,以便可以將它用于更復(fù)雜的應(yīng)用程序。

-

led

+關(guān)注

關(guān)注

242文章

23277瀏覽量

660848 -

matlab

+關(guān)注

關(guān)注

185文章

2976瀏覽量

230466 -

HDL

+關(guān)注

關(guān)注

8文章

327瀏覽量

47382 -

文件

+關(guān)注

關(guān)注

1文章

566瀏覽量

24744 -

Simulink

+關(guān)注

關(guān)注

22文章

535瀏覽量

62398

原文標(biāo)題:MATLAB / Simulink HDL 快速入門

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

專家支招:使用MATLAB和Simulink算法創(chuàng)建FPGA原型

使用MATLAB Simulink和HDL編碼器創(chuàng)建自定義IP--AWB

初學(xué)者的MATLAB_Simulink翻譯

電力系統(tǒng)的matlab的simulink仿真和GUI例子講解

什么是MATLAB SIMULINK?Simulink有哪些應(yīng)用實(shí)例?

Simulink軟件入門

淺析MATLAB和Simulink嵌入式視覺(jué)應(yīng)用

基于MatLab/Simulink的GPS系統(tǒng)仿真

電路實(shí)驗(yàn)與Matlab/Simulink仿真

MathWorks推出基于MATLAB生成HDL代碼的產(chǎn)品

Matlab-Simulink教程集合(文檔)

MATLAB教程之MATLAB語(yǔ)言的基礎(chǔ)知識(shí)及入門

講解MATLAB/Simulink HDL使用入門

講解MATLAB/Simulink HDL使用入門

評(píng)論