今天來看一下中斷及ARM體系中對中斷的處理,直接進入正題。

中斷是指計算機運行過程中,出現某些意外情況需主機干預時,機器能自動停止正在運行的程序并轉入處理新情況的程序,處理完畢后又返回原被暫停的程序繼續運行。

中斷的幾個主要目的。

?第一,通過中斷可以提高CPU效率。假設一種場景,CPU通知其它設備完成某項工作,當設備完成任務后,CPU如何知道呢?一種方式是設備標記狀態寄存器,等待CPU來查詢,這種做法弊端是程序員在編寫程序時不能確切知道設備完成任務所需的時間,也就是說需要定時去查詢設備的狀態。我們知道,現代CPU一般頻率很高,如果去頻繁查詢外部設備,尤其是低速設備,必將浪費很多的CPU資源;如果查詢的時間間隔長,那么外設的利用率就不高。有一種解決辦法,那就是外設處理完任務,主動告訴CPU,從而省去了CPU的查詢開銷。

?中斷的第二個用途是,可以維護系統正常運行。現代的操作系統都是多任務系統,表面看起來多個程序在并行,實際上真正的CPU是分時復用的(假設最簡單的單核單線程),并不是真的并行。如果這時有一個惡意程序,一直霸占CPU資源不釋放,是不是整個系統就會掛死呢?答案是并不會,因為CPU的分配是由操作系統負責完成的,原理就是通過中斷把控制權從程序手中交還給操作系統。另外,CPU訪問內存或其它設備時,也可能發生一些錯誤。對于不同錯誤有不同的處理方式,也可以通過中斷來完成。

對于一些特定的應用場景,設備系統需要滿足實時性。所謂實時性,就是要求系統在規定的或者可預期的時間內作出反應。此類需求也可以通過中斷來滿足。

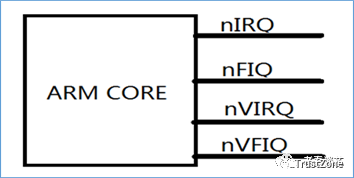

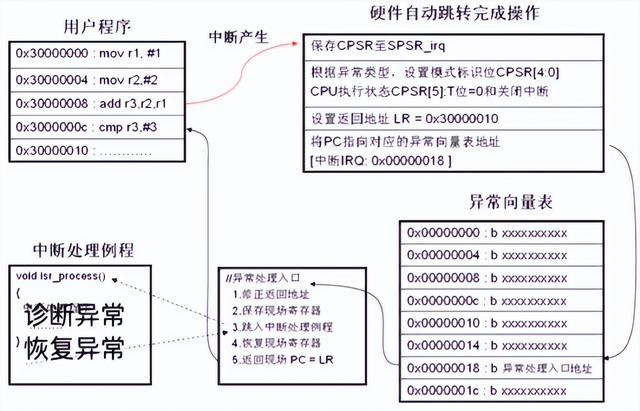

還記得前面講ARM異常時的概念嗎?中斷算一種異步異常,《ARM系列 -- 異常和特權》。A系列處理器提供四個管腳來實現中斷,分別是:

? nIRQ:物理普通中斷

? nFIQ:物理快速中斷

? nVIRQ:虛擬普通中斷

? nVFIQ:虛擬快速中斷 如下圖所示:

其中虛擬中斷是為了實現虛擬化而準備的,這部分留待以后講虛擬化時再說。我們只看物理中斷。

在開始介紹中斷概念時,我們說中斷可能會有很多種,每個設備都可能要發中斷,而ARM處理器只有兩個管腳,那怎么辦?這時,就需要有一個模塊來收集所有的中斷,然后轉發給處理器。在ARM的體系中,這個模塊就是通用中斷處理器(generic interrupt controller,以下簡稱GIC)。

類似ARM的處理器,GIC有架構和實現之分。GIC的架構經歷了GICv1,GICv2,GICv3和GICv4。每個架構下有有對應的設計實現,

在介紹GIC-600之前,有必要先講一下中斷的一些基本概念。

?首先,中斷是分優先級的。很多個設備同時發送中斷,處理器必須遵守一定的規則來給所有中斷排序,從而決定先響應哪個。這個規則就是中斷優先級,操作系統需要維護中斷處理器中的優先級寄存器。

?既然有了優先級,就有了中斷嵌套。當處理器處理某個低優先級的中斷時,來了一個高優先級的中斷,CPU可以保留低優先級的中斷處理現場,轉而處理高優先級中斷,待高優先級處理完再繼續處理低優先級中斷。如果CPU在某段時間內,選擇不響應某設備,其中斷也可以被屏蔽。

在ARM體系中,對于每個中斷,有四個狀態:

? pending:中斷處于有效狀態,但是CPU沒有響應該中斷

? active:中斷處于有效狀態,CPU在響應該中斷

? active and pending:CPU在響應該中斷,但是該中斷源又發送中斷過來

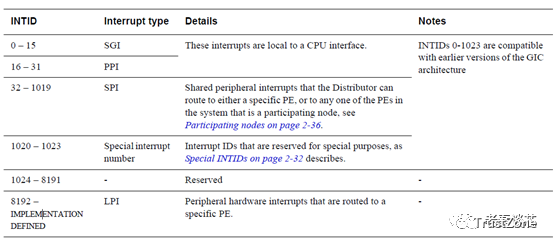

在ARM體系中,中斷分為以下幾個類型(不討論虛擬中斷):

? PPI:(Private Peripheral Interrupt,私有外設中斷),該中斷來源于core,但是該中斷只對指定的core有效,所謂的私有即指對core私有;

? SPI:(Shared Peripheral Interrupt,共享外設中斷),該中斷來源于外部設備,該中斷可以對所有的core有效;

? SGI:(Software Generated Interrupt,軟件中斷),用于給其它的core發送中斷信號;

? LPI:(Locality-specific Peripheral Interrupt,特定局部外設中斷),是一種基于消息的邊沿中斷。

ARM又為每種中斷分配了中斷號,用以區分,其中1020-1023是特殊的中斷號。

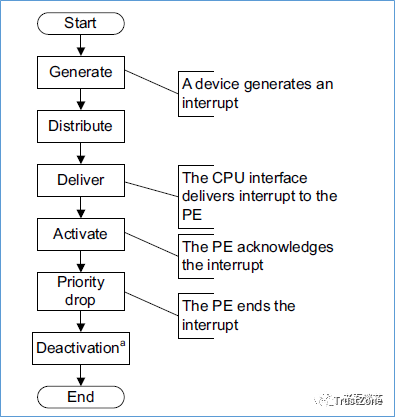

圖1 GICv3中斷號分配對于每個中斷,從產生到處理再到結束,是有一個完整的生命周期的。

圖2 物理中斷生命周期

? generate:外設或軟件發起一個中斷

? distribute:中斷經過分組,優先級仲裁等,發送給對應的CPU interface

? deliver:CPU interface將中斷發送給core

? activate:當CPU core開始響應中斷,GIC將最高激活優先級的中斷設置為激活

? priority drop: core發信號給GIC,通知最高優先級中斷,GIC可以重置優先級

? deactivation:清除中斷

這里要解釋一下CPU interface。前面也提到了,core提供給中斷的物理管腳只有兩個,中斷會有成百上千個,GIC怎么把這些中斷發送給core是一個問題。這時就需要CPU interface了。CPU interface將GIC發送的中斷信息,通過IRQ,FIQ管腳,發送給連接到core。CPU

interface提供了以下的功能:

? 將中斷請求發送給core

? 中斷進行認可

? 中斷完成識別

? 設置中斷優先級屏蔽

? 定義中斷搶占策略

? 決定當前處于pending狀態最高優先級中斷

在GICv3架構中,CPU interface被抽離出來,實現在core內部的。也就是說,在GIC-600中,是不包含CPU interface的。這樣做的好處是,可以減少中斷響應的時間,并且減少系統總線的占用。對于眾核SoC設計來說,其物理設計非常大,CPU interface實現在core內部,也就意味著某些中斷寄存器可以放在其內部,這樣core就可以很快的訪問到這些寄存器了。對于那些常用的寄存器,core不用跋山涉水的通過系統總線或片上網絡去頻繁訪問GIC了。CPU interface與GIC之間,是通過專用的AXI-stream總線來傳輸信息的。

-

ARM

+關注

關注

134文章

9097瀏覽量

367560 -

cpu

+關注

關注

68文章

10863瀏覽量

211767 -

中斷

+關注

關注

5文章

898瀏覽量

41497

發布評論請先 登錄

相關推薦

ARM7嵌入式系統的中斷設計與中斷處理優化

中斷及ARM體系中對中斷的處理

中斷及ARM體系中對中斷的處理

評論