前言

本次總結為中斷和定時器的相關內容。除了基本的寄存器配置,初始化,中斷主要是掌握三級中斷制,定時器主要關注定時器的工作原理和中斷時間的設置。

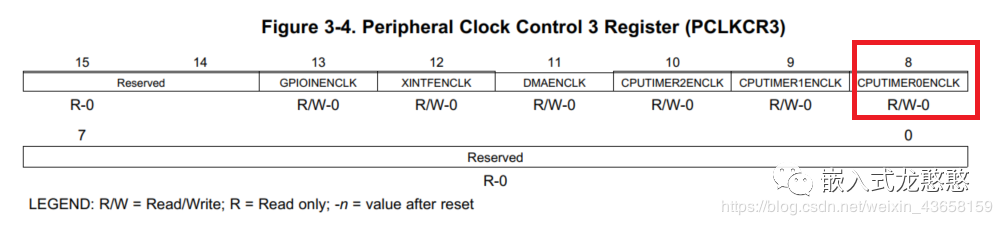

時鐘

定時器時鐘使能為外設時鐘控制寄存器PCLKCR3的第8位。

SysCtrlRegs.PCLKCR3.bit.CPUTIMER0ENCLK = 1; // CPU Timer 0

1 中斷

F28335內部有16個中斷線,分別是:

1、2個不可屏蔽中斷:RESET、NMI;

2、14個可屏蔽中斷:INT1-INT12,外部中斷和內部單元使用;INT13和INT14 預留給實時操作系統。

當前主要學習INT1-INT12這12 個中斷。

CPU級中斷有12個中斷線(INT1-12),通過PIE控制器進行復用管理,將外設中斷分成12組,每一組有8個外設級中斷組成,共有96個外設級中斷,分別對應相應外設接口的中斷引腳,實際有效外設中斷為58個,其余為保留。

1.1 三級中斷制:

三級中斷制:

外設級中斷 ——> PIE級中斷 ——> CPU級中斷

使用中斷時主要需要注意各級中斷的標志、使能、應答寄存器,具體如下圖的標號所示:

外設級: IF、IE;

PIE級: PIEIFRx、PIEIERx.y、PIEACK;

CPU級: IER、IFR、INTM。

見Figure6-6。

一般當有中斷請求時,IF和IFR等寄存器是硬件自動置位,IE和IER等寄存器是軟件使能。

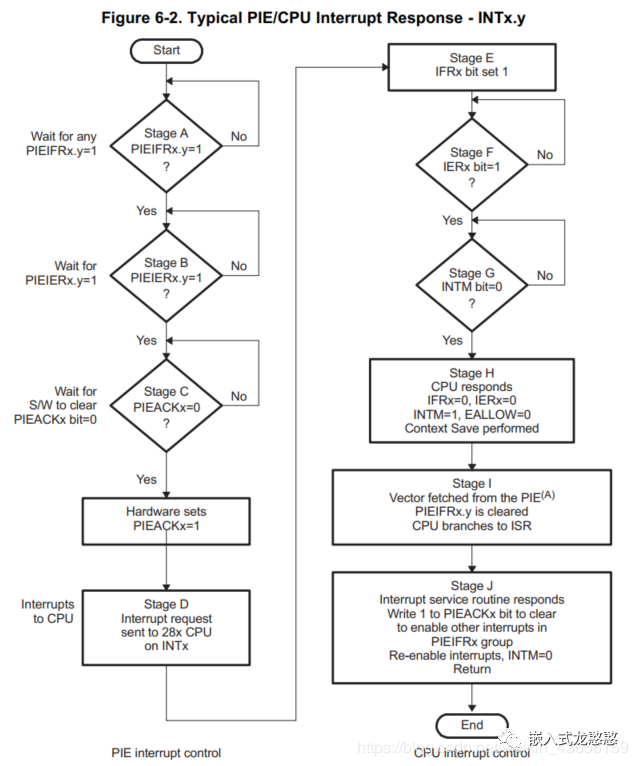

中斷的過程:

如下圖,可以依據Figure6-1和Figure6-2進行理解。

外設級: 當有外設級中斷產生,外設中斷標志寄存器IF硬件自動置位,同時外設中斷使能寄存器IE軟件使能(置1)后,向PIE控制器發出中斷申請;

PIE級: 有PIE中斷時,PIE級中斷標志位PIEIFRx硬件自動置位,使能位PIEIERx.y軟件使能(置1),PIEACK為0,此時PIE可從終端組向CPU發送中斷,PIEACK硬件置1,中斷組的中斷向量已向CPU發送了中斷請求,中斷到CPU。

CPU級: 有中斷請求時,CPU級中斷標志寄存器IFR硬件置1,CPU級中斷使能寄存器IER軟件使能(置1),全局中斷屏蔽位INTM使能(0-使能,CPU可響應;1-失能,CPU不響應),此時CPU響應中斷,清除IER,IFR=0(軟件清除/自動清零),CPU從PIE獲取向量(ISR地址),清除PIEIFRx(中斷響應后自動清零、寫0也可清零),CPU調到ISR執行中斷程序,ISR程序,通過向相應中斷位寫1到PIEACKx讓該位清零,清除PIEIFRx中使能的中斷,重新使能中斷,INTM=0。

2 定時器

定時器主要總結TIMER0的使用,包括定時器工作原理以及定時時間的設置。

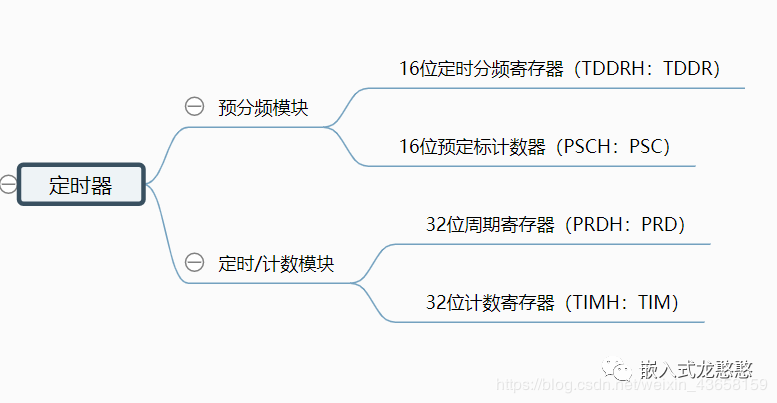

2.1 定時器工作原理

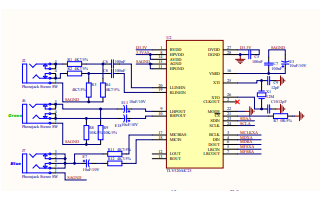

定時器組成如下圖所示:

定時器工作原理如下圖Figure3-19定時器功能框圖以及流程圖所示:

由定時器流程圖可知,定時器周期寄存器(PRDH:PRD)的值為軟件設置的定時器頻率* 定時器周期(Freq*Period)的值,定時器周期值在每一個定時器周期開始之前會裝載到計數寄存器(TIMH:TIM)中。而計數寄存器的值遞減又和預分頻模塊有關,即和定時器分頻寄存器(TDDRH:TDDR)和預定標計數器(PSCH:PSC)有關。

定時器分頻寄存器(TDDRH:TDDR)和預定標計數器(PSCH:PSC)主要決定定時器源時鐘周期,PSCH:PSC和TDDRH:TDDR等于0時,系統時鐘即為定時器源時鐘,見外設時鐘框圖和Figure3-19,可知即每一個定時器源時鐘周期(1/150M),TIMH:TIM減1。

每隔(TDDRH:TDDR+1)個定時器源時鐘周期,定時器計數寄存器減1。若PSCH:PSC和TDDRH:TDDR等于0時,一個定時器源時鐘周期后,重新將TDDRH:TDDR的值裝載到PSCH:PSC,TIMH:TIM減1。

2.2 定時時間計算

中斷時間T:0.5s,即500ms

T = Freq * Period / 150 000000 (s)

其中Freq 為定時器頻率150(MHz);Period 為定時器周期值,計算得來

Period = 150 000000 * 0.5 / 150 = 50 0000

小結

本次總結主要講述了中斷的三級中斷制,包括其中斷過程中相關定時器的設置;定時器講述了定時器工作原理和中斷時間的設置。這是在學習過程中需要主要了解的內容,掌握這些內容后基本可以完成定時器0的中斷實驗。

-

寄存器

+關注

關注

31文章

5345瀏覽量

120477 -

預分頻器

+關注

關注

0文章

18瀏覽量

8147 -

中斷定時器

+關注

關注

0文章

4瀏覽量

5595 -

時鐘控制

+關注

關注

0文章

17瀏覽量

6828

發布評論請先 登錄

相關推薦

關于tms320f28335功率保護中斷引腳的問題

tms320f28335原理圖庫

TMS320F28335,TMS320F28334,TMS320F28332 Digital Signal Controllers (DSCs)

tms320f28335的數據手冊

TMS320f28335控制AD7656的硬件電路設計

TMS320F28069和TMS320F28335的DSP處理器到底有什么區別

TMS320F28335學習之中斷和定時器的相關內容

TMS320F28335學習之中斷和定時器的相關內容

評論