不斷發展的電子世界需要更強大、更高效和更可靠的設備,集成電路 (IC) 設計公司因此面臨著持續上漲壓力,既要提供創新的產品,又要縮短產品上市時間。過去的傳統方法是通過投入更多資源來解決問題,但這種方法在巨大的壓力已然難以為繼,“左移”(shift left) 策略和工具的出現為IC設計業者提供了新的發展之路。

“左移” —— 將流程前置解決后期問題

在傳統 IC 設計流程中,簽核驗證 (sign-off),包括DRC、LVS、以及ERC 往往排在設計周期的末尾。這一整套流程可以確保設計符合晶圓代工廠的要求。然而,在將系統級芯片的所有元件編譯到單個芯片中時,通常會產生一些意外錯誤。糾正這些錯誤需要經過多輪耗時的調試和驗證迭代,耗時耗力耗成本。

“左移”的策略是將在設計流程末尾執行的任務整合到早期階段,其主要目的是及早發現關鍵缺陷和錯誤,以更輕松、更快速地予以解決。“左移”策略不僅能節省時間和資源,還能保證產品質量,甚至提升產品質量。

在考慮實施“左移”策略的時候,我們可以先考慮這樣一個問答清單,來幫助自己了解“左移”可能會如何影響我們的設計流程:

1.為什么要使用 “左移”策略?

“左移”策略具有幾項顯著優勢,包括:

節省時間和資源:通過及早識別和解決問題,減少所需的迭代次數,從而節省寶貴的時間和資源。

提升產品質量:在早期階段解決缺陷有助于提高設計質量,并降低最終產品出現嚴重錯誤的可能性。

效率增益:將流程前置可以簡化整個設計流程,使設計團隊之間的協作更加順暢,并縮短驗證周期。

降低風險:更容易發現早期問題,降低后期設計變更的風險,節省成本。

2.“左移” 策略的關鍵組成部分有哪些?

“左移”通常涉及以下幾部分:

早期檢測工具:實施能夠及早發現設計問題的工具和方法,例如 DRC 和 LVS 驗證。

自動化:利用自動化、集成和用戶友好的界面來簡化驗證流程并減少人工干預。

協作:促進不同設計團隊(例如 IP 設計人員、模塊設計人員、P&R 工程師)協作,共同解決問題。

3.“左移” 對不同的 IC 設計人員有何影響?

IP設計人員可以在多個方面從 “左移”策略中獲益:

硬IP:“左移”有利于在設計階段發現變更并修復錯誤,確保硬 IP 組件順利簽核。

軟IP:“左移”有助于及早檢測和糾正 SRAM 等軟 IP 中的問題,從而提高整體設計質量。

定制IP:借助在線檢查工具,定制封裝設計變得更加高效,減少了手動迭代所需的時間和工作量。

對于模塊設計人員和 P&R 工程師來說,“左移”可提供以下優勢:

及早識別問題:在設計流程的早期發現貼裝、抽象和布局中的問題,從而減少運行時間和錯誤數。

高效的工程變更單(ECO)處理:“左移”可精確定位變更并支持有針對性的檢查,從而簡化工程變更單 的處理。

定制 IP 集成:定制 IP 封裝可以更順利地集成,同時減少運行時間和錯誤帶來的挑戰。

全芯片設計人員可在多項任務中體驗“左移”帶來的好處:

精準的天線檢查:“左移”可將焦點范圍縮小到芯片級連線,從而簡化天線檢查并減少運行時間。

高效實施工程變更單:在最后階段引入的設計變更變得更易于管理,降低了引入新錯誤的風險。

優化調試:識別設計修訂版之間的變化和解決錯誤變得更加簡單,簡化了調試過程。

市場的變化既帶來挑戰也伴隨機遇。西門子EDA的CalibrenmPlatform提供創新的“左移”解決方案,具備早期分析能力和人工智能技術,滿足時下設計人員和工程師的需求,有效提升生產力、效率并降低成本,助力IC設計企業直面市場挑戰。

-

芯片

+關注

關注

455文章

50812瀏覽量

423581 -

西門子

+關注

關注

94文章

3039瀏覽量

115869 -

eda

+關注

關注

71文章

2759瀏覽量

173263

原文標題:談談“左移”策略

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

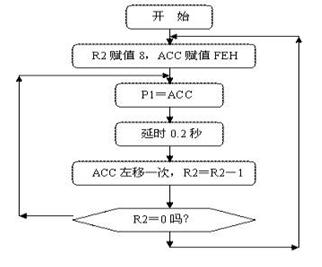

ICC AVR 左移問題

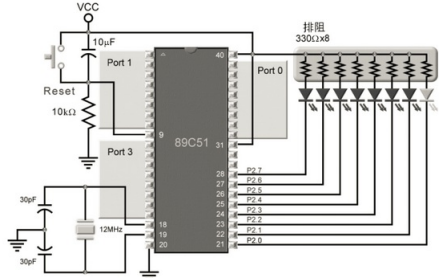

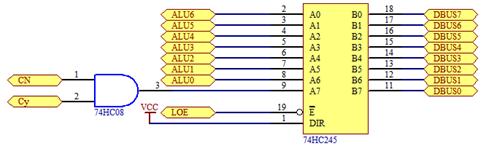

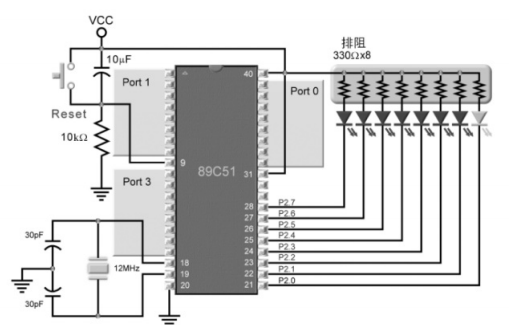

廣告燈的左移右移實驗

使用51單片機實現單燈左移雙燈左移以及霹靂燈的實驗演練資料合集

談談優良的PCB分層策略(EMC設計)資料下載

淺談SCL 之 ROL( 循環左移)

C語言中無符號數和有符號數的左移和右移

談談“左移”策略

談談“左移”策略

評論