本文要點

MOSFET非理想特性對模擬集成電路設(shè)計有重要影響

空載電導率、溝道長度調(diào)制和亞閾值導通是需要考慮的非理想特性

工藝、電壓和溫度變化對晶體管性能有影響

本文摘要

MOSFET的非理想特性對模擬集成電路設(shè)計具有重要影響。文章介紹了非理想特性的多個方面,包括電容、體效應(yīng)、溝道長度調(diào)制、亞閾值導通、遷移率下降以及飽和速度和壓敏降閾。同時,工藝、電壓和溫度變化也對晶體管性能產(chǎn)生影響。因此,在模擬IC設(shè)計過程中,需要考慮并解決這些非理想特性和外部條件的影響。

MOS 晶體管表現(xiàn)出理想模型未涵蓋的各種二階效應(yīng)。為了設(shè)計能夠在現(xiàn)實世界中工作的模擬集成電路,我們需要了解這些非理想情況。

在上一篇文章中,我們介紹了MOSFET的基本結(jié)構(gòu)和工作區(qū)域。我們討論的模型描繪了理想的 MOSFET,并且由于其溝道尺寸較長,對于早期 MOS 晶體管來說相當準確。然而,隨后的研究和晶體管的持續(xù)小型化都揭示了晶體管行為的一系列非理想性。本文將介紹這些非理想的基礎(chǔ)知識以及它們?nèi)绾斡绊懩M集成電路中的晶體管性能。

寄生電容

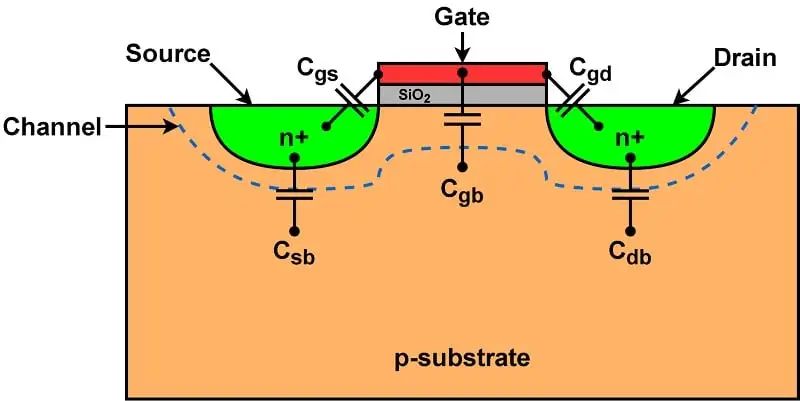

由于 MOSFET 的物理實現(xiàn),端子結(jié)之間會形成以下寄生電容:

CGS:柵源電容。

CGD:柵漏電容。

CGB:柵體電容。

CSB:源極至主體電容。

CDB:漏極至體電容。

在設(shè)計包含 MOSFET 的模擬 IC 時,這些電容在電路帶寬中發(fā)揮著重要作用。圖 1 說明了它們的位置。

圖 1.具有寄生電容的 MOSFET 結(jié)構(gòu)。

電容值隨工作區(qū)域而變化,我們將在接下來的部分中討論。

柵源電容和柵漏電容

雖然圖 1 中未顯示,但在晶體管制造過程中,源極和漏極略微延伸至柵極下方。在柵極與源極或漏極重疊的區(qū)域中,形成電容器,其中柵極氧化物 (SiO2) 作為它們之間的電介質(zhì)。這種重疊的長度稱為Ldiff。

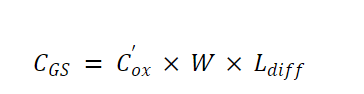

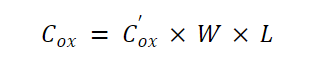

由氧化物電容 ( Cox)形成的柵極到源極(或漏極)電容器的值可以計算為:

等式 1。

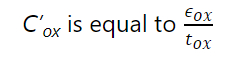

在這里::

εox 是二氧化硅的介電常數(shù)

tox 是柵極氧化物的厚度(如圖 1 所示的高度)。

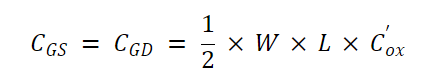

這個柵源(或漏極)電容的簡單方程僅在源極和漏極彼此分離時才有效,當晶體管處于截止或飽和狀態(tài)(因為溝道夾斷)時,情況也是如此。在線性區(qū)域中,源極和漏極溝道實際上被電阻溝道“短路”,因此我們只需要關(guān)心柵極和溝道之間的氧化物電容。

由于器件是對稱的,因此在線性區(qū)域中,我們可以假設(shè)源極和漏極各占氧化物電容值的一半。柵極到源極和柵極到漏極的值可以計算為:

等式2。

柵體電容

CGD的值實際上由兩個獨立電容器的并聯(lián)組合組成:

氧化物電容器,位于柵極和襯底之間。

耗盡層電容器,形成于耗盡層(溝道和襯底之間的區(qū)域)和襯底之間。

氧化物電容值可以使用以下公式計算:

等式 3。

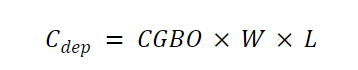

和耗盡電容,使用這個:

等式 4。

其中CGBO是取決于晶體管物理特性的柵極體重疊電容項。

氧化物電容器和耗盡電容器彼此并聯(lián)——當兩者都存在時,它們就加在一起。在截止區(qū)域中,因為柵極和主體之間沒有通道,所以CGB的值是等式 3 和 4 之和。一旦存在通道,Cox就會與主體斷開,正如我們之前與柵極討論的那樣到源極/漏極電容。因此, CGD的值等于Cdep,可以使用公式 4 求出。

源極至體電容和漏極至體電容

導出CSB和CDB的值涉及大量的器件物理知識。這些值由結(jié)電容(CJ)決定。CJ的值由耗盡區(qū)寬度決定,而耗盡區(qū)寬度又取決于 MOSFET 內(nèi)的摻雜濃度。

我們需要了解的是,CSB和CDB在源極或漏極與主體之間的連接處將保持恒定,因為端子的尺寸在工作區(qū)域之間不會改變。

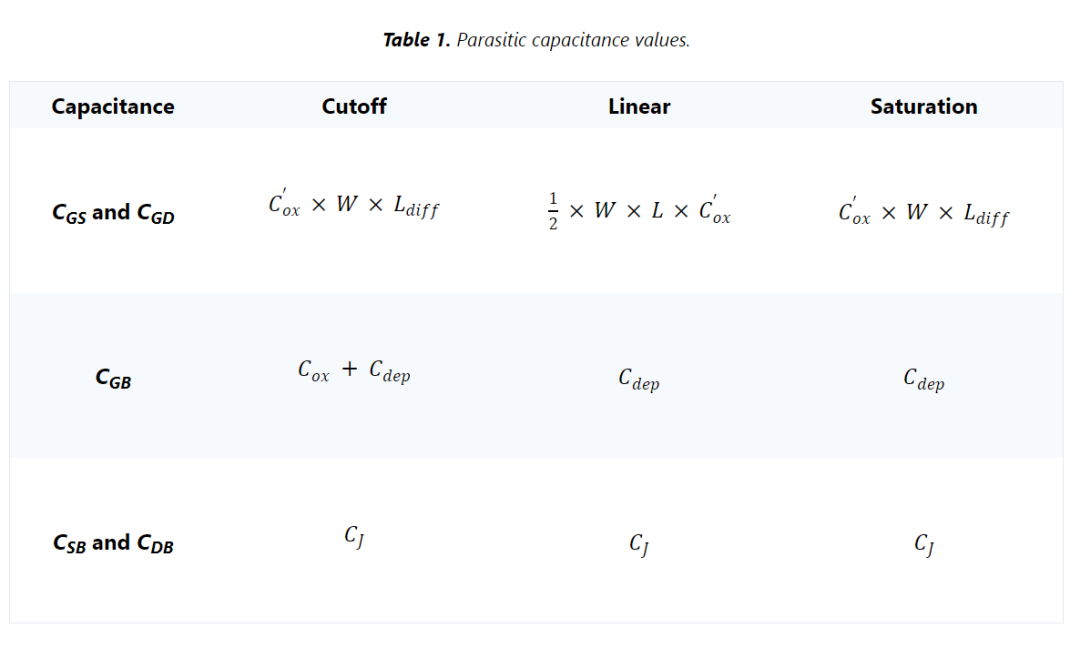

電容值匯總

表 1 按工作區(qū)域總結(jié)了 MOSFET 的寄生電容值。

表 1.寄生電容值。

身體效應(yīng)

我們之前討論了晶體管的體極端和源極端通常如何連接到相同的電位,但沒有詳細說明原因。為了理解其中的原因,讓我們更深入地了解一下物理晶體管, VGS的值從 0 增加到大于閾值電壓 (Vth)。

隨著VGS從零緩慢增加,硅內(nèi)的正空穴被推離柵極,留下帶負電的離子。這會產(chǎn)生耗盡層——其中不存在電荷載流子的區(qū)域。隨著VGS繼續(xù)增加,柵極電荷開始緩慢增長到大于耗盡層的電荷,從而在源極和漏極之間形成電子溝道。

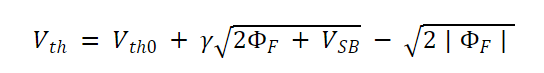

我們假設(shè)體電壓變得比源電壓更負(VSB> 0)。現(xiàn)在更多的空穴被吸引到體終端,導致通道附近形成更大的耗盡區(qū)。這意味著閾值電壓的增加,因為現(xiàn)在需要更大的柵極電壓來克服耗盡區(qū)的電荷并形成溝道。當VSB< 0時,情況相反:溝道附近形成較小的耗盡區(qū),并且V?th相應(yīng)降低。

體效果如圖2所示。

圖 2.ID與VGS隨VSB變化的關(guān)系(淺藍色:VSB= 0 V;綠色:VSB= –0.5 V;紅色:VSB= 0.5 V)。

相對于體效應(yīng)的閾值電壓可以計算為:

等式 5。

在這里::

Vth0是標稱閾值電壓

ΦF是硅的費米勢。

體效應(yīng)對模擬設(shè)計有很大影響——將晶體管堆疊在一起非常流行,這會導致體效應(yīng)以一種不平凡的方式改變閾值電壓。

通道長度調(diào)制

理論上,處于飽和狀態(tài)的晶體管應(yīng)該充當具有無限輸出電阻的完美電流源。實際上,當溝道夾斷時,VDS仍然對漏極電流有影響,因此晶體管的輸出電阻很大但有限。這是由于一種稱為溝道長度調(diào)制的現(xiàn)象,其中隨著飽和區(qū)漏極電壓的增加,溝道長度開始逐漸減小。

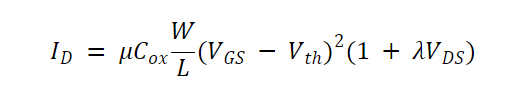

為了適應(yīng)溝道長度調(diào)制,我們將飽和狀態(tài)下的漏極電流方程調(diào)整為:

等式 6。

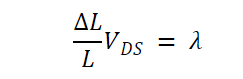

通道長度調(diào)制系數(shù) λ 的計算公式為:

等式 7。

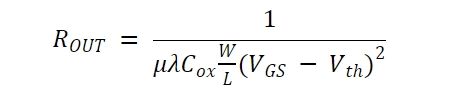

由此,我們可以計算出飽和狀態(tài)下的輸出電阻(ROUT)為:

方程 8.

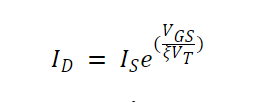

亞閾值傳導

之前,我們定義了三個晶體管工作區(qū)域:截止區(qū)域、線性區(qū)域和飽和區(qū)域。事實上,還有第四個區(qū)域:亞閾值區(qū)域,它在超低功耗模擬 IC 設(shè)計中非常流行。

該區(qū)域的形成是因為晶體管不會在VGS低于Vth時完全關(guān)閉。相反,擴散電流在源極和漏極之間構(gòu)成了一個小溝道。當VGS

方程 9.

在這里:

流動性下降和速度飽和

晶體管內(nèi)的漂移電流由內(nèi)部電場決定,隨著晶體管尺寸的縮小,其電場迅速增加。事實證明,對于短溝道晶體管,晶體管內(nèi)可以實現(xiàn)少數(shù)載流子的最大速度。這稱為飽和速度。

這限制了某些器件相對于VGS和VDS的電流增加,因為它們的驅(qū)動電流最終會達到頂峰。此外,隨著電場繼續(xù)增加,這些載流子的遷移率降低,導致在這些非常高的電壓下驅(qū)動電流減少。這種短溝道效應(yīng)是現(xiàn)代晶體管行為的許多方面之一,無法通過我們在上一篇文章中看到的平方律方程來預(yù)測。

漏極誘導勢壘降低 (DIBL)

當VDS變得足夠大時,漏極開始將負電荷吸引到柵極下方的表面,幫助柵極創(chuàng)建溝道。結(jié)果,有效閾值電壓降低,形成Vth與VDS成反比的關(guān)系。這稱為漏極誘導勢壘降低,簡稱 DIBL。

PVT 變化

工藝、電壓和溫度的變化(統(tǒng)稱為 PVT)共同構(gòu)成了我們將討論的最后一個非理想情況。

當制造晶體管時,制造工藝的變化是不可避免的。工藝變化可能會改變重要的晶體管特性,從而導致不同的閾值電壓、載流子遷移率和寄生電容等影響。這些過程變化通常包含在四個“角落”內(nèi):快-快、快-慢、慢-快和慢-慢。角點描述了基于最壞情況制造統(tǒng)計數(shù)據(jù)的 PMOS 和 NMOS 晶體管的相對速度。

除此之外,通過蒙特卡羅分析測試一個晶體管到另一個晶體管的變化,該分析使用包含制造的晶體管參數(shù)變化的統(tǒng)計數(shù)據(jù)的模型。模擬設(shè)計人員必須同時使用蒙特卡羅方法和角點方法,因為失配會對電路性能產(chǎn)生毀滅性影響。

最后,工作電壓和環(huán)境溫度也會影響晶體管性能。在 IC 設(shè)計過程中必須檢查這些環(huán)境條件,以確保最終產(chǎn)品按照規(guī)格運行。

-

集成電路

+關(guān)注

關(guān)注

5409文章

11789瀏覽量

365459 -

電容器

+關(guān)注

關(guān)注

64文章

6400瀏覽量

101032 -

模擬電路

+關(guān)注

關(guān)注

125文章

1586瀏覽量

103327 -

MOSFET

+關(guān)注

關(guān)注

148文章

7711瀏覽量

216333 -

晶體管

+關(guān)注

關(guān)注

77文章

9881瀏覽量

139816

原文標題:模擬IC設(shè)計中的MOSFET非理想性

文章出處:【微信號:moorexuetang,微信公眾號:摩爾學堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

評論