從線上購物時的“猜你喜歡”、到高等級自動駕駛汽車上的實時交通信息接收,再到在線視頻游戲,所有的這些都離不開人工智能(AI)加速器。AI加速器是一種高性能的并行計算設備,旨在高效處理神經網絡等AI工作負載并提供近乎實時的處理方案,從而實現一系列應用。

為了讓AI加速器有效地完成自己的工作,數據必須要以極快的速度在AI加速器(作為設備)與CPU和GPU(主機)之間進行快速且低延時的移動,而實現這一切的關鍵就在于PCI Express(PCIe)高速接口。

PCIe大約每三年更新換代一次,帶寬也會隨之翻倍,而這正是我們數據驅動的數字世界所需要的。作為PCIe規范的最新版本,PCIe 6.0可提供:

每個引腳64 GT/s的數據傳輸速率

一種新的低功耗狀態,從而實現更低的功耗

經濟高效的性能

高性能的完整性和數據加密(IDE)

向后兼容前幾代

盡管PCIe過去可能通過PC上的插槽,連接顯卡和掃描儀等外圍設備,但得益于帶寬的不斷增加,PCIe的作用現在已遠不止于此。本文將詳細介紹PCIe如何滿足AI加速器的日益增長的要求。

AI無處不在,PCIe也是如此

GlobalData的數據表明,AI正在芯片組領域中迅速普及,預計到2030年,超過40%的芯片組中都將包含AI硬件。人工智能(AI)和機器學習(ML)工作負載的復雜性仍在不斷增加。事實上,AI和ML訓練模型的規模大約每隔幾個月就會翻一番。為了確保有效性,AI系統必須能在不犧牲性能或增加延遲的情況下,通過AI開發管道移動大型數據集。不妨看一看下面這些帶寬密集型工作負載示例:

4K和8K高清視頻 — 需要更多計算能力和內存

高分辨率和高動態范圍 — 實現機器視覺和實時感知

多攝像頭陣列和4D傳感 — 實現深度和運動推理

所有這些趨勢都表明,AI加速器的關鍵在于提供強大的并行計算能力,讓語音激活和高等級自動駕駛汽車等應用能夠做出近乎實時的響應。這些高性能機器既可以采用超大芯片的形式,例如用于深度學習系統的Cerebras晶圓級引擎(WSE);也可以是GPU、大規模多核標量處理器或空間加速器,通過將數十到數百個芯片組合到一起,打造出具有數百petaFLOPS處理能力的大型系統,用以處理大型神經網絡。

PCIe發揮著高效的橋梁作用

由于能夠處理AI和ML工作負載,AI加速器可以增強數據中心服務器中CPU的處理能力,而PCIe則充當兩者之間的橋梁。就其作用而言,PCIe具有以下優勢:

最大限度提高芯片到芯片接口的帶寬,無論是用于大規模計算陣列中的AI加速器,還是邊緣的AI加速器

提供擴展容量,以便在多個主機和多臺設備之間移動數據,因為PCIe插槽可以支持各種類型的擴展卡,包括AI加速器

支持通過多線程技術跨多個芯片并行處理工作負載

實現主機和設備之間的通用互操作性,使得能夠在系統運行時無縫添加或移除AI加速器卡

提供低功耗PCIe 6.0 L0p模式,能夠以更少的通道支持所需的數據流量,從而可以降低功耗,幫助最大限度地減少碳足跡

提供數據保密性、完整性和重發保護功能,確保傳輸中的數據免受嗅探、篡改、刪除、插入或重發數據包攻擊

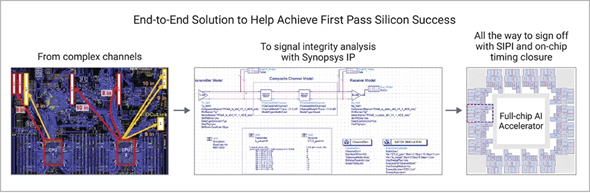

要充分利用這種安全的高速接口,經驗證的PCIe物理層(PHY)和具有IDE安全性的控制器IP是關鍵,而相關的專業知識也對幫助開展相應設計至關重要。功耗和信號完整性方面的考量則突顯了專家支持的重要作用。AI加速通常需要許多高速通道。PCIe的多個通道同時切換會產生大量功耗,這使得電源完整性成為一個問題。如果在同時切換過程中出現IR壓降等問題,則不利于充分發揮全部性能。信號完整性也很重要,因為系統中在AI加速器和CPU之間傳輸的信號必須完好無損。新思科技內部擁有功耗和信號完整性方面的專家,他們能夠模擬多通道環境,指導開發者在設計芯片時將支持PCIe的PHY放置在合適位置,從而實現最佳性能。

新思科技是PCIe IP和PCIe協議驗證解決方案(包括驗證IP)的行業領導者,新思科技的PCIe專家也是PCI-SIG聯盟(負責編寫PCIe總線規范)的主要貢獻者。新思科技的PCIe產品組合,以及各種具有向后兼容性的組件,包括:

新思科技PHY IP,通過自適應數字信號處理(DSP)算法來優化數字均衡,以跨底板、網絡接口卡(NIC)及芯片到芯片通道實現高能效

新思科技控制器IP,具有與新思科技IDE安全IP模塊緊密集成的架構,其中包含多個接口,旨在盡可能降低延遲并提高吞吐量

新思科技驗證IP,可加速測試平臺開發,并且具有內置驗證計劃、驗證序列和功能覆蓋范圍

用于新思科技ZeBu硬件加速系統和新思科技HAPS原型系統的新思科技協議接口卡、在線和虛擬解決方案,可實現軟件驅動的系統驗證、性能分析、認證和流片前合規性測試

除了端到端PCIe IP解決方案,新思科技的IP核組合還包括內存、處理器及其他用于AI加速器的接口IP。全棧式AI驅動型電子設計自動化(EDA)套件Synopsys.ai現已搭載能夠顯著加快專用AI加速器設計的功能。在驗證方面,AI SoC需要更快的流片前硬件輔助驗證解決方案。新思科技的ZeBu Server 5和HAPS系統提供了超快且容量超大的硬件輔助驗證(HAV)系統,有助于完成各種復雜SoC設計的所有系統級驗證用例。

PCIe接下來的發展方向如何?

下一代PCIe有望達到速度驚人的2.048TB。隨著越來越多的設備和系統融入AI,任何能夠滿足AI速度需求的創新都是利好消息。對于現今和未來的AI加速器來說,不斷發展的PCIe高速接口有望與之攜手共進,讓日常生活變得更加智能。

審核編輯:湯梓紅

-

AI

+關注

關注

87文章

31287瀏覽量

269643 -

高速接口

+關注

關注

1文章

44瀏覽量

14786 -

PCIe

+關注

關注

15文章

1245瀏覽量

82877 -

新思科技

+關注

關注

5文章

802瀏覽量

50376

原文標題:AI低延遲應用,怎么缺少PCIe高速接口?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

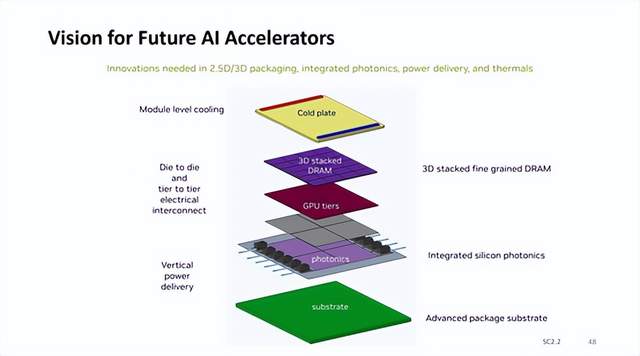

英偉達AI加速器新藍圖:集成硅光子I/O,3D垂直堆疊 DRAM 內存

IBM將在云平臺部署AMD加速器

磁調制式電流傳感器在粒子加速器中的應用

SiFive發布MX系列高性能AI加速器IP

下一代高功能新一代AI加速器(DRP-AI3):10x在高級AI系統高級AI中更快的嵌入處理

西門子推出Catapult AI NN軟件,賦能神經網絡加速器設計

美國限制向中東AI加速器出口,審查國家安全

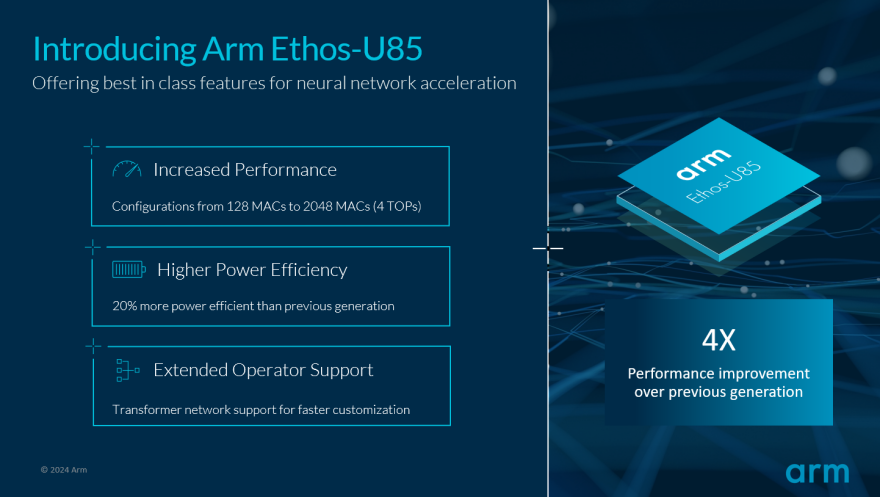

Arm推動生成式AI落地邊緣!全新Ethos-U85 AI加速器支持Transformer 架構,性能提升四倍

Hitek Systems開發基于PCIe的高性能加速器以滿足行業需求

PCIe在AI加速器中的作用

PCIe在AI加速器中的作用

評論