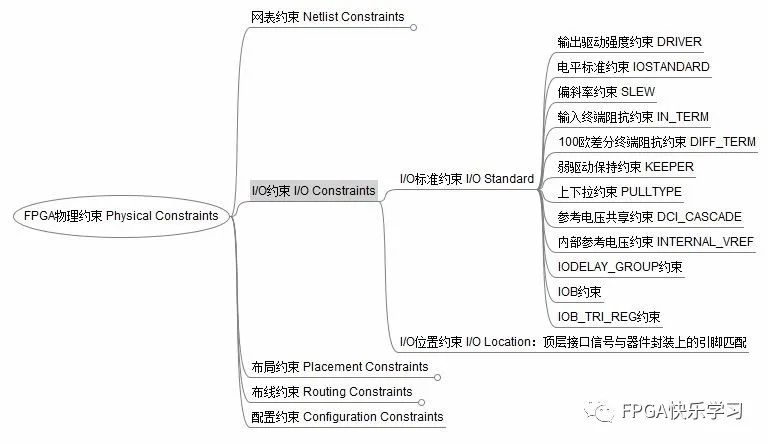

I/O約束(I/O Constraints)包括I/O標準(I/OStandard)約束和I/O位置(I/O location)約束。

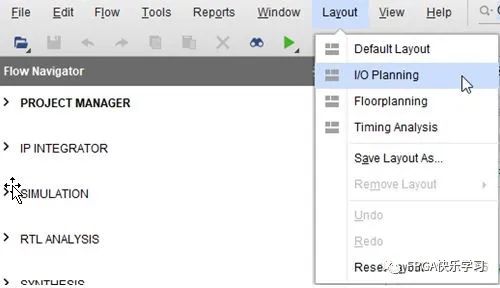

以Xilinx Vivado開發工具為例,點擊OpenImplemented Design,打開實現設計(Implemented Design)頁面。接著如圖1所示,在菜單上點擊Layout-> I/O Planning,打開I/O約束頁面。

圖1I/OPlanning菜單

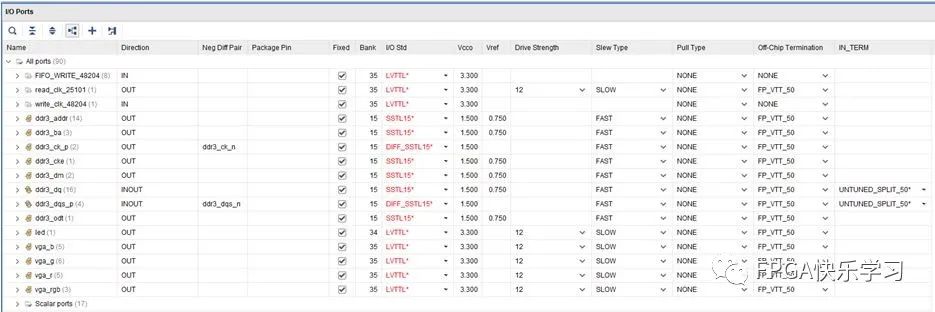

I/O約束頁面如圖2所示,在該頁面中,Allports一列中按照總線的方式進行分類,可以進一步展開看到每一個具體的I/O引腳的約束信息。這里的I/O標準約束包括了電平標準(I/O Std)、輸出驅動強度(Drive Strength)、上下拉類型(Pull Type)、偏斜率類型(Slow Type)、輸入終端阻抗(IN_TERM)等。由于I/O標準和FPGA外部所連接的外設芯片息息相關,每個外設芯片所對應的I/O標準不同,在FPGA中的約束設置也有所不同。

圖2I/O約束頁面

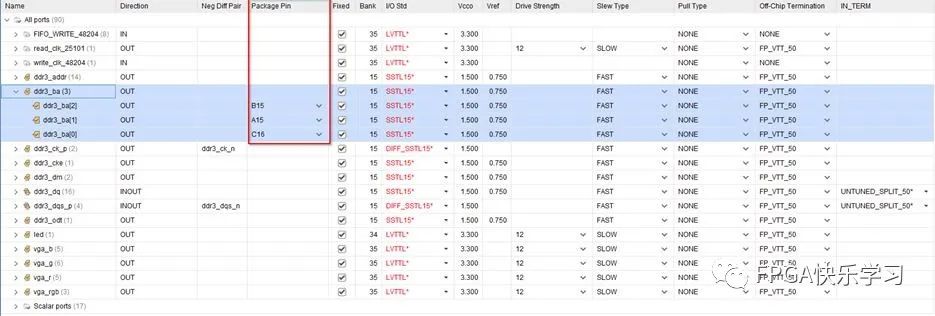

如圖3所示,展開一組名為ddr3_ba的總線,其下的3個I/O引腳詳細的約束信息都一目了然。Package Pin一列即I/O的位置約束信息,通常對應著一些字母和數字組合的位置代號,如圖示的B15、A15、C16,即FPGA器件封裝上對應著的具體的物理引腳的代號。通過這樣的位置約束,就將FPGA頂層模塊代碼中的I/O信號和器件封裝上的引腳映射在一起了。

圖3I/O位置約束

審核編輯:湯梓紅

-

FPGA

+關注

關注

1641文章

21912瀏覽量

611722 -

Xilinx

+關注

關注

73文章

2179瀏覽量

123873 -

引腳

+關注

關注

16文章

1470瀏覽量

51894 -

約束

+關注

關注

0文章

82瀏覽量

12875 -

Vivado

+關注

關注

19文章

823瀏覽量

67885

原文標題:物理約束實踐:I/O約束

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

物理約束之IO約束

物理約束之布局約束

如何約束內部生成的i2s o時鐘?

Adam Taylor玩轉MicroZed系列74:物理約束

FPGA設計約束技巧之XDC約束之I/O篇(下)

評論