來源 :智能軟件研究中心,作者:羅宇哲,直接來源:華為開發者社區

STM32作為ARM核芯片廣為人知,分享本文來了解下與之相關的ARM。

01 ARM匯編指令

操作系統中硬件相關的部分集中體現在匯編指令和對寄存器的操作中,因此我們對ARM體系結構的介紹也圍繞ARMv8-A的匯編指令和寄存器來展開。

處理器架構是處理器廠商為同一個系列的處理器規定的一個規范。ARM架構是一種精簡指令集(RISC)架構,具有以下RISC架構特點:

較大的通用寄存器堆。

load/store體系結構,其中數據處理操作僅對寄存器內容進行操作,而不是直接對內存內容。

簡單尋址模式,所有load/store地址由寄存器內容和指令確定。該體系結構定義了處理單元與內存(包括緩存)的交互,并包括內存地址翻譯系統。它還描述了多個處理單元如何相互作用。面積小、性能強和非常低的功耗是ARM體系結構的關鍵特性。本小節主要以ARMv8-A架構為例來介紹ARM體系結構的基本特性。ARMv8-A體系結構的一個重要特性是向后兼容,可以支持諸多標準和應用場景下的最優設計。ARMv8-A架構支持64bit的執行模式(AArch64)和32bit的執行模式(AArch32),這一模式兼容之前的ARM架構。兩種執行狀態都支持SIMD和浮點指令。

一、AMRv8架構概要

ARM體系結構自推出以來已經有了顯著的發展,并且ARM還在繼續開發它。到目前為止,已經有八個主要版本,由版本號1到8表示。其中前三個版本現在已經過時了。

通用名稱AArch64和AArch32描述了64位和32位執行狀態。AArch64是64位執行狀態,意味著地址保存在64位寄存器中,并且基本指令集可以使用64位寄存器進行處理。AArch64支持A64指令集。AArch32是32位執行狀態,這意味著地址保存在32位寄存器中,并且基本指令集使用32位寄存器進行處理。AArch32支持T32和A32指令集。

ARM支持三種架構配置:

A系列,面向應用場景的架構(Application Profile)。該系列支持基于內存管理單元(MMU)的虛擬內存系統體系結構(VMSA)。它支持A64、A32和T32指令集。

R系列,面向實時場景的架構配置。該系列支持基于內存保護單元(MPU)的受保護內存系統體系結構(PMSA)。它支持A32和T32指令集。

M系列,面向微處理器的架構。該系列實現了一個為低延遲中斷處理而設計的程序員模型(programmers’ model),該模型具有寄存器硬件堆棧和對中斷處理程序的高級語言支持。它支持T32指令集的變種。

(注:內存保護單元(MPU)是ARM中配備的有效保護系統資源的一種硬件,提供了內存區域保護功能。)

二、ARMv8-A指令集

在ARMv8-A中,可能的指令集取決于執行狀態:

AArch64:AArch64 state只支持A64指令集。這是一個固定長度的指令集,使用32位指令編碼。

Arch32:AArch32 state支持以下指令集:

A32:這是一個固定長度的指令集,使用32位指令編碼。它是與ARMv7 ARM指令集兼容。

T32:這是一個可變長度指令集,它同時使用16位和32位指令編碼。它與ARMv7 Thumb指令集兼容。

ARM指令的基本格式如下[2]:

其中各個部分的含義為:

Opcode:操作碼,也就是助記符,說明指令需要執行的操作類型;

Cond:指令執行條件碼;

S:條件碼設置項,決定本次指令執行是否影響PSTATE寄存器相應狀態位值;

Rd/Xt:目標寄存器,A32指令可以選擇R0-R14,T32指令大部分只能選擇RO-R7,A64指令可以選擇X0-X30;

Rn/Xn:第一個操作數的寄存器,和Rd一樣,不同指令有不同要求;

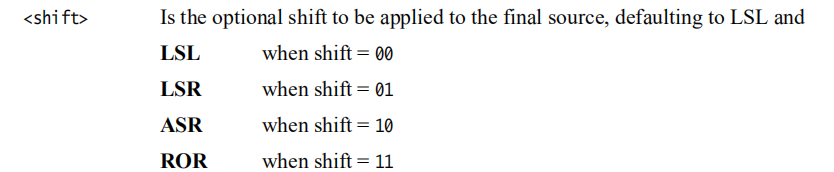

Opcode2:第二個操作數,可以是立即數,寄存器Rm和寄存器移位方式(Rm,#shit);

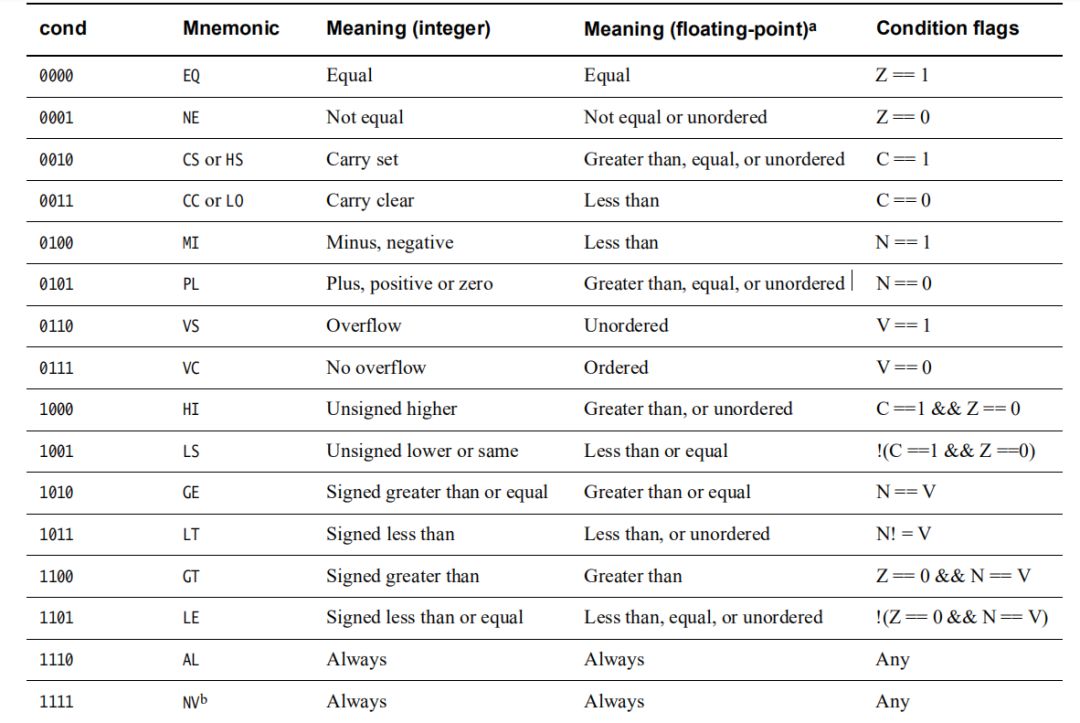

ARMv8-A指令集的條件碼如下圖所示:

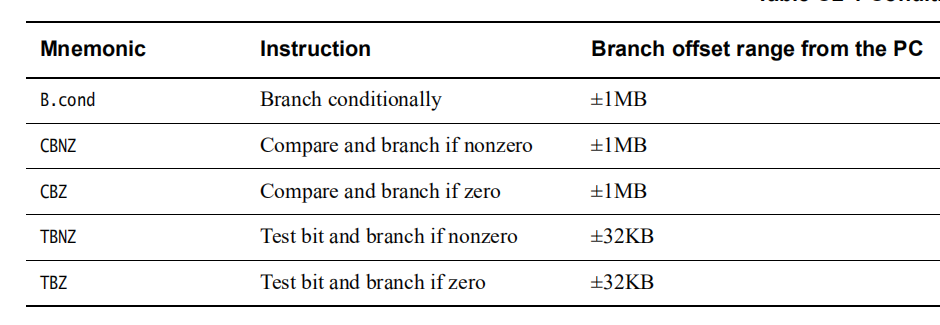

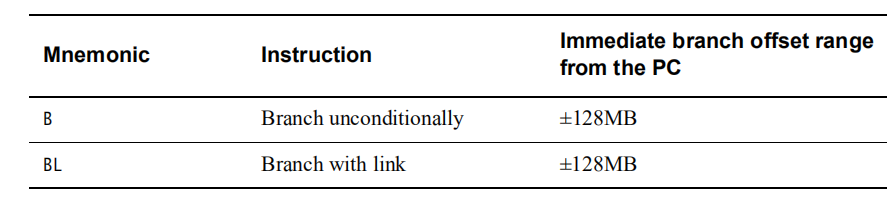

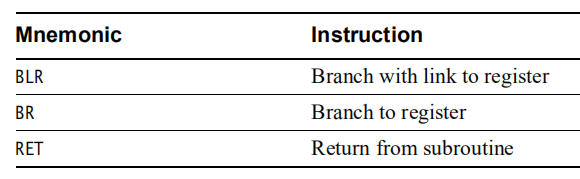

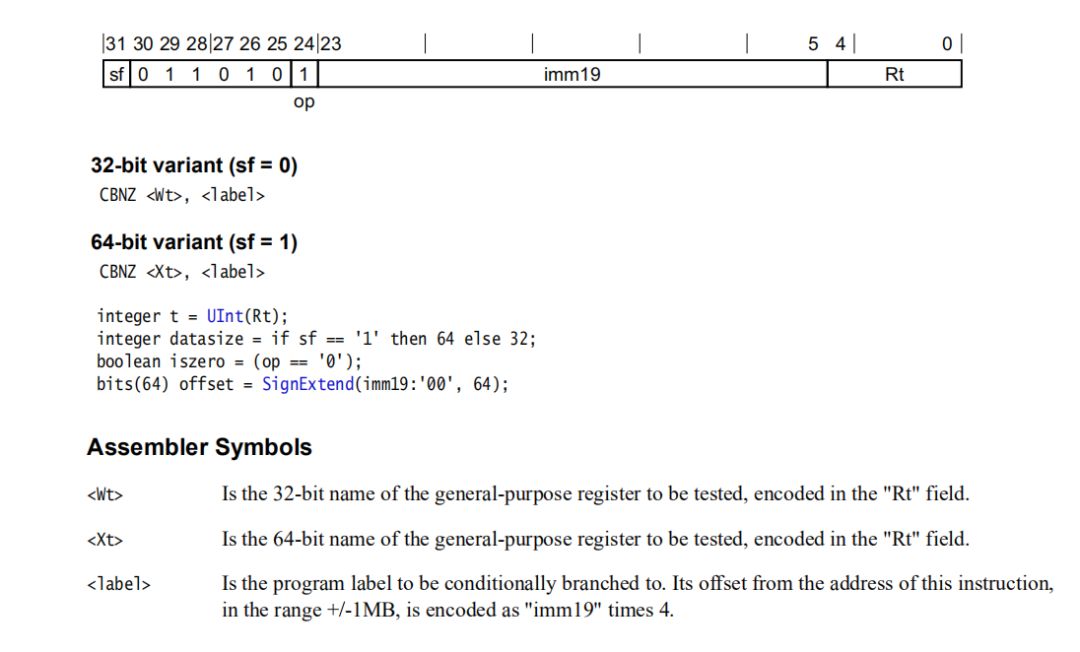

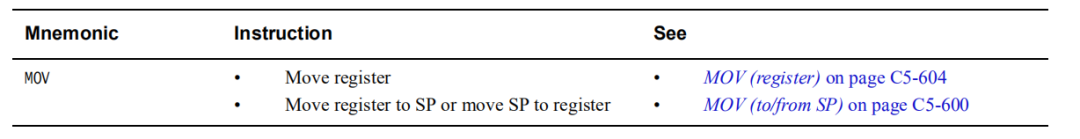

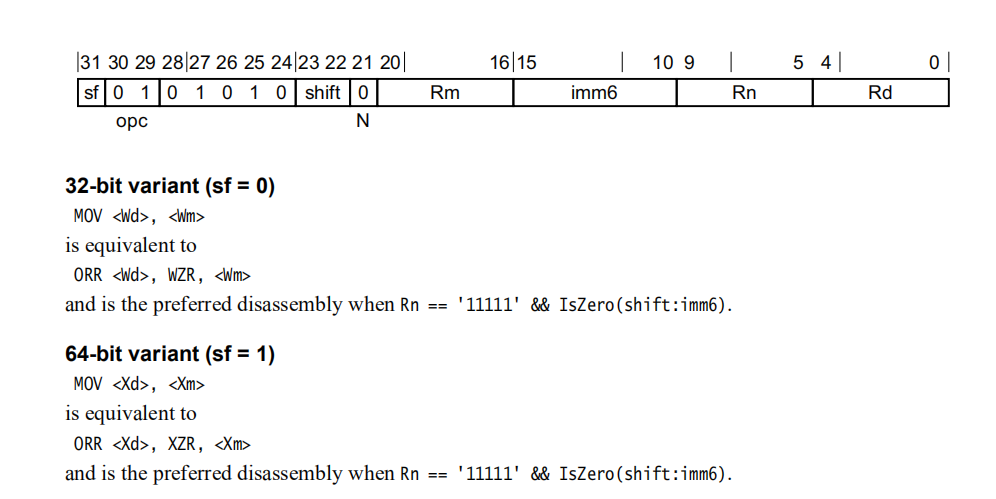

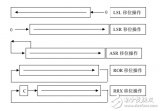

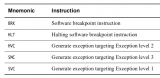

下面以A64指令集為例簡要介紹ARMv8-A的指令體系。A64指令集中的指令主要分為控制指令、訪存指令和計算指令。控制指令主要包括有條件分支指令、無條件分支指令、異常產生和返回指令、系統寄存器指令、系統指令、提示指令、同步指令和清除獨占訪問標志指令。訪存指令主要有Load指令和Store指令,這兩種指令有許多變種。計算指令包含算數指令、邏輯指令、MOVE指令、移位指令、位擴展指令和SIMD指令等等。以下列出了一些常用的控制指令的名稱與用途。

1. 控制指令:

條件分支指令:

無條件分支指令:

使用寄存器的無條件分支指令:

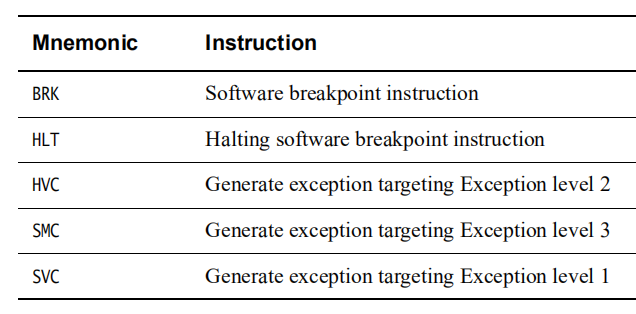

異常產生指令:

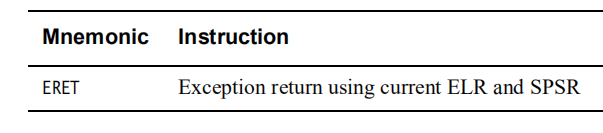

異常返回指令:

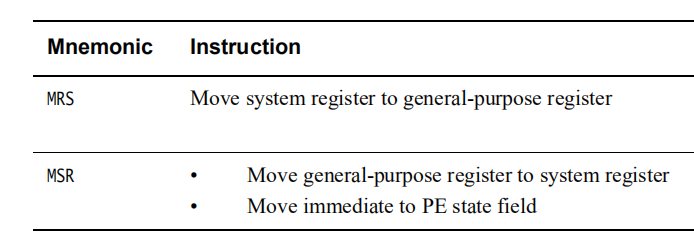

系統寄存器指令:

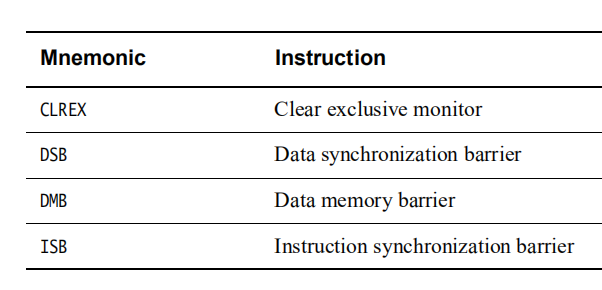

同步指令和獨占狀態清除指令:

例如:

2. 訪存指令:

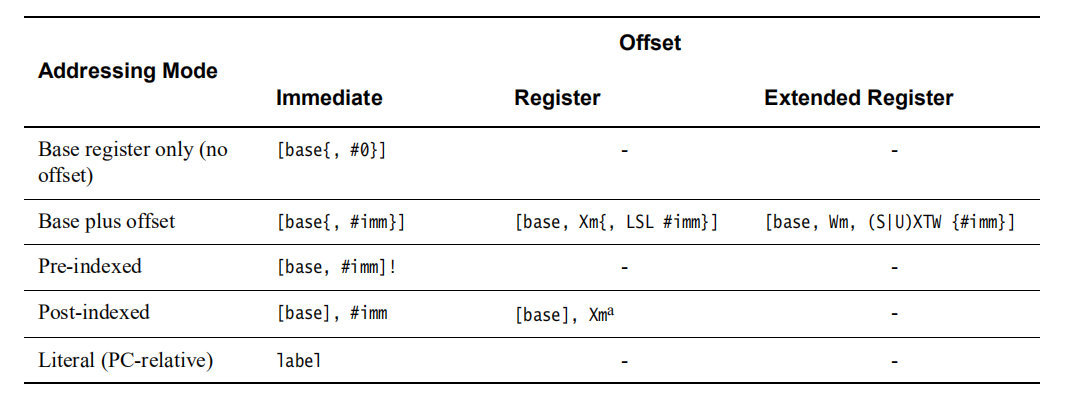

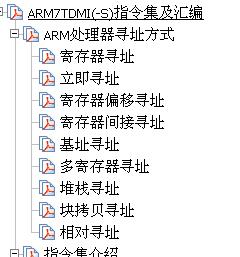

ARMv8訪存指令支持以下尋址模式:

基址加上無符號立即數的尋址和基址加上有符號立即數的尋址;

基址加上寄存器偏移值;

基址加上擴展的寄存器偏移;

pre-index模式;

post-index模式;

PC相對尋址模式。

具體情形見下表:

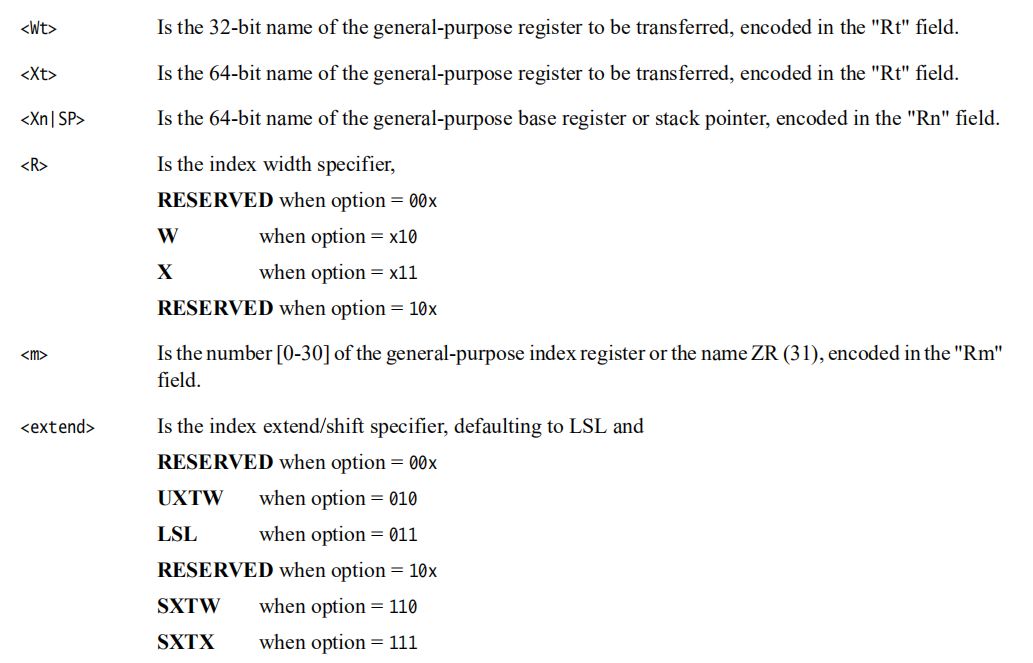

其中對于A64指令集來說,64bit的基址來自通用寄存器X0-X30或來自棧指針SP,立即數或寄存器偏移值則是可選的,對尋址方式的解釋如下:

寄存器偏移尋址是指來自64bit基址寄存器的地址加上一個偏移值;

Pre-indexed模式是指尋址地址是64bit基址加上一個偏移值,這個計算和將會寫入基址寄存器;

Post-indexed模式是指尋址地址是64bit的基址,但之后基址和偏移值的和將會寫入基址寄存器;由此可見pre-indexed和post-indexed的區別在于使用的地址是先加上偏移值再使用還是先使用再加上偏移值;

PC相對尋址是指尋址地址是這條指令64bit的PC值加上一個19bit的有符號字偏移,這個地址在當前指令的PC值的 ±1MB范圍內并且是4byte對齊的。使用PC相對尋址所load的數據大小至少為32bit并且只能用來預取指令,且PC值不能被其他尋址方式使用。

一個立即數偏移可以為有符號的,也可以為無符號的,可以為scaled也可以為unscaled。當一個立即數偏移是scaled的時候,它被編碼為傳輸數據大小的整數倍。雖然匯編程序總是使用byte對齊的偏移,但匯編器或反匯編器會做必要的轉換工作,因此可用的byte偏移值取決于load/store指令類型和數據傳輸的大小。

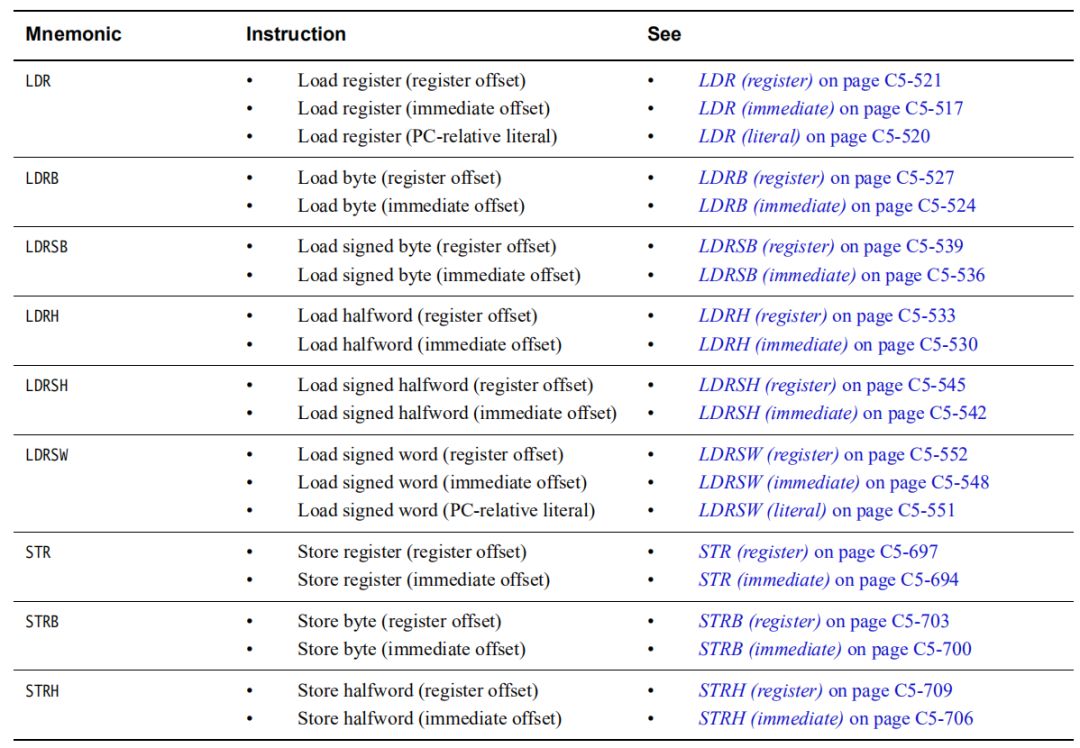

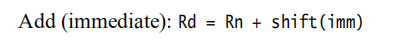

下面列出了一些load/store指令:

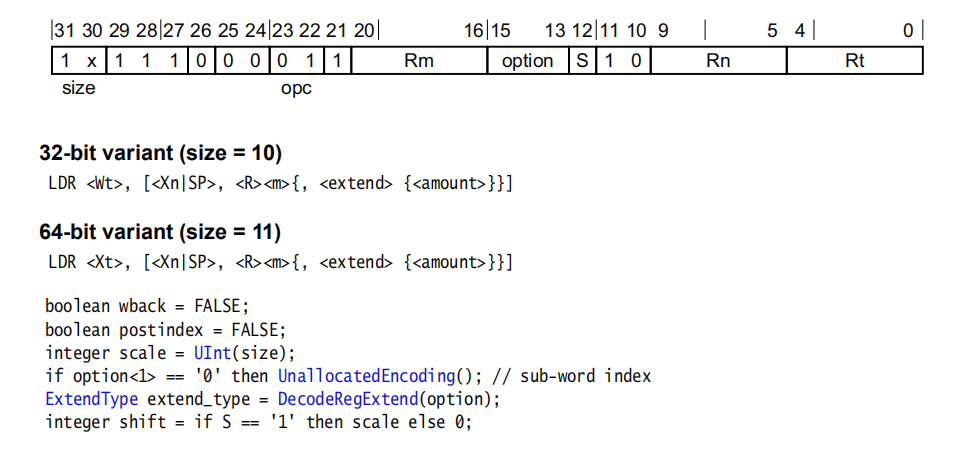

例如Load寄存器指令:

上表中指令的尋址方式有:

基址加上12bit無符號scaled立即數偏移尋址;

基址加上9bit有符號unscaled立即數偏移尋址;

基址加上64bit寄存器偏移,可選為scaled;

基址加上32bit可拓展寄存器偏移,可選為scaled;

有unscaled9bit有符號立即數偏移的pre-indexed模式;

有unscaled9bit有符號立即數偏移的post-indexed模式;

Load至少32bit數據的PC相對尋址模式。

如果被load或store的指令的尋址模式會修改基址寄存器的內容,且被load/store寄存器恰好的是基址所在的寄存器,那么硬件的行為可能不確定。

3.計算指令:

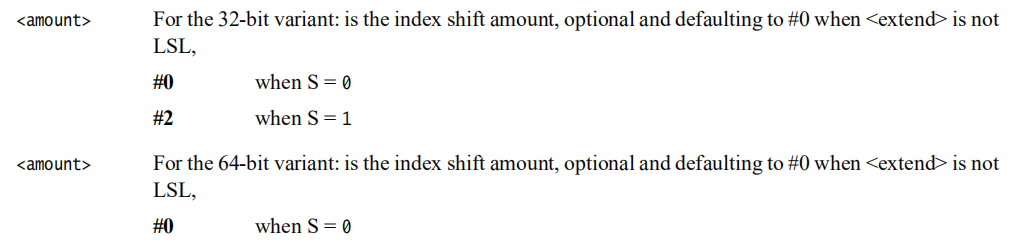

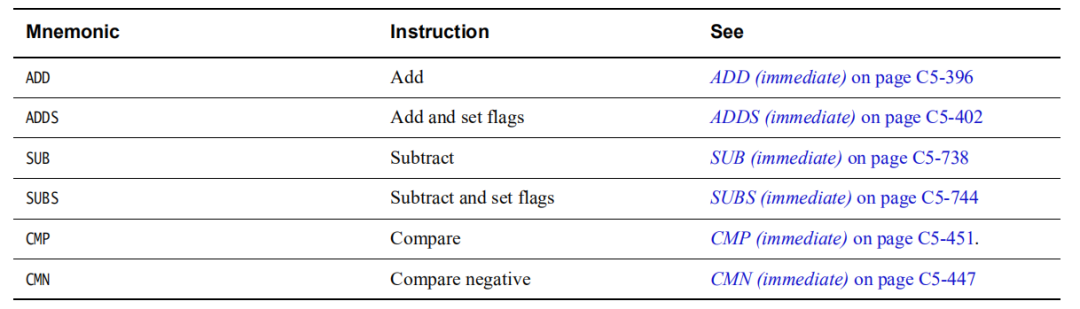

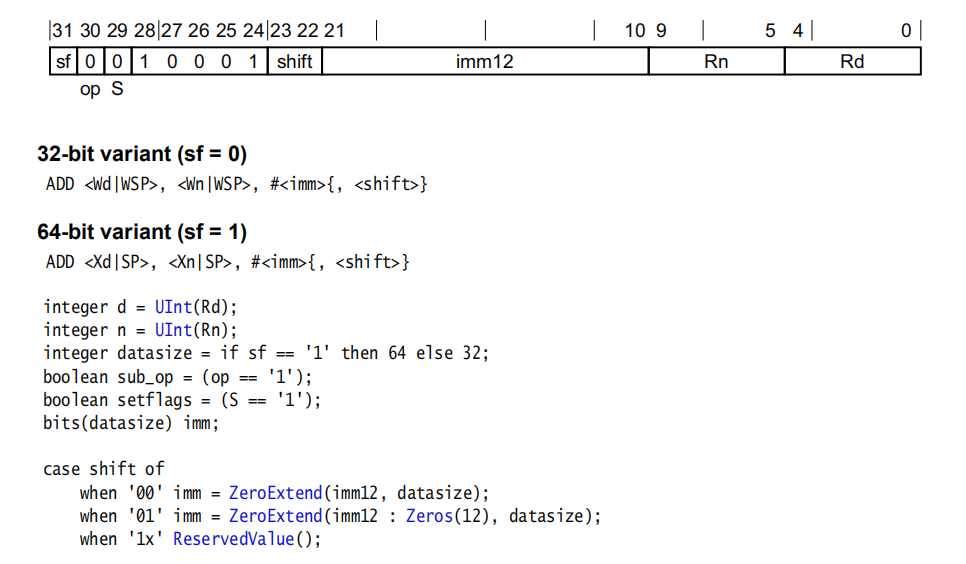

在操作系統匯編語言中使用的計算指令主要是一些簡單的算數計算指令,用于對寄存器的move操作和對地址的計算操作,一般計算指令既可以使用立即數作為操作數,也可以使用寄存器中的數作為操作數。下面簡單列舉了一些算數指令:

使用立即數的簡單算數指令:

例如:

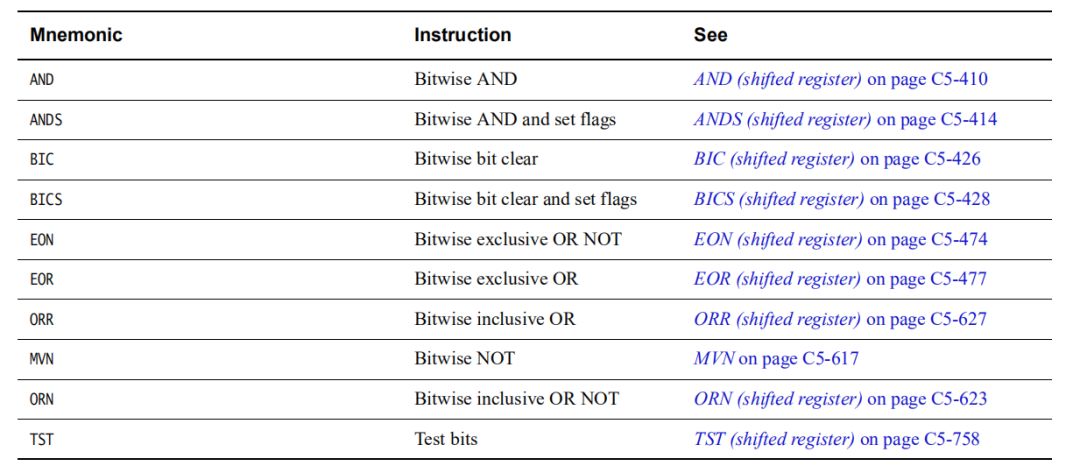

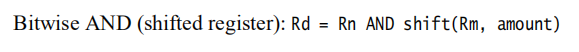

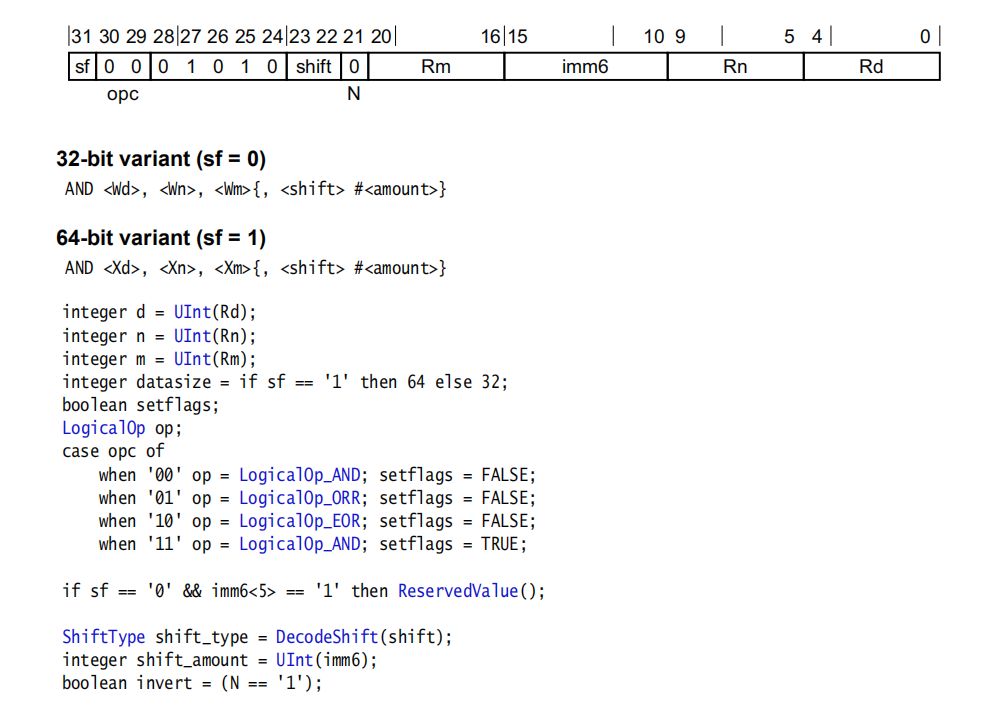

使用寄存器的邏輯操作指令:

例如:

其中:

寄存器移位指令:

例如:

02ARM架構寄存器

在處理器中,寄存器用于保存需要被快速訪問的數據,在操作系統中需要特別注意的寄存器主要有棧指針寄存器(SP)、連接寄存器(LR)、程序計數器(PC)以及當前程序狀態寄存器(CPSR)和保存程序狀態寄存器(SPSR)。本小節主要以ARMv8-A為例介紹ARM架構的寄存器的基本情況。詳情可參見文獻[3],D1.6小節。

在這一小節中,我們主要介紹ARMv8架構中AArch64執行狀態下的寄存器使用情況。ARM架構中的寄存器主要有兩類,一類用于提供系統控制與狀態報告;另一類用于指令運行和異常處理。我們主要討論第二類。

通用寄存器主要用于基本指令集中的指令運行,通用寄存器共有31個,編號為R0-R31。這些通用寄存器可以被當成31個64bit的寄存器,編號為X0-X30;或者被作為31個32bit的寄存器,編號為W0-W30。

在AArch64執行狀態下,除了通用寄存器外,每一個異常級別都會有一個棧指針寄存器(StackPointer Register, SP),棧指針寄存器為SPEL0和SPEL1。異常級別用于區分指令的執行權限,我們將在本章的第四期介紹。如果處理器實現中包含EL2,那么還有SPEL2。如果處理器實現中包含EL3,那么還有SPEL3。詳情可參考鏈接[5]。

SIMD和浮點寄存器共用一系列寄存器,這些寄存器會用于浮點操作、向量操作和其它SIMD有關的標量操作。SIMD指令是能夠復制多個操作數、并把它們打包在大型寄存器的一組指令集[3]。以加法指令為例,單指令單數據(SISD)的CPU對加法指令譯碼后,執行部件先訪問內存,取得第一個操作數;之后再一次訪問內存,取得第二個操作數;隨后才能進行求和運算。而在SIMD型的CPU中,指令譯碼后幾個執行部件同時訪問內存,一次性獲得所有操作數進行運算。浮點寄存器和SIMD寄存器共包含32個128bit位寬的寄存器,V0-V31。這些寄存器可以作為:

32個雙字(64bit)寄存器,D0-D31。

32個單字(32bit)寄存器,S0-S31。

32個半字(16bit)寄存器,H0-H31。

32個單字(8bit)寄存器,B0-B31。

程序狀態寄存器(Current Program Status Register,CPSR) 在用戶級編程時用于存儲條件碼。CPSR包含條件碼標志,中斷禁止位,當前處理器模式以及其他狀態和控制信息。

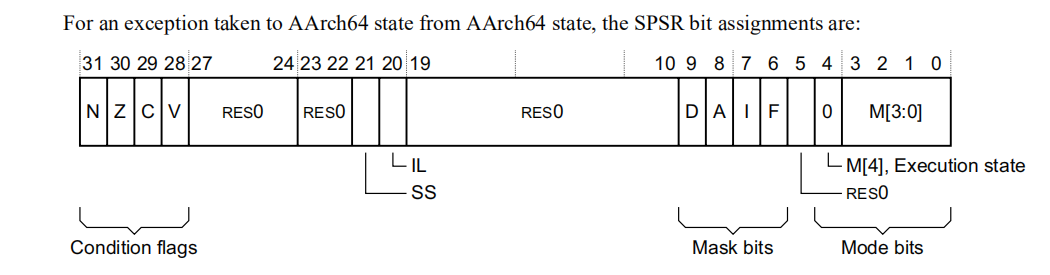

保存程序狀態寄存器(SPSR,Saved Program StatusRegister)用于保存CPSR的狀態,以便異常返回后恢復異常發生時的工作狀態。在A64中,不再使用單一的CPSR寄存器,來保存當前處理器狀態,而是用PSTATE來保存處理器狀態,而在A32中依然使用CPSR。有關PSTATE和CPSR的詳細信息可參考鏈接[4]。A64中SPSR 格式的示意圖如下圖所示:

其中N、Z、C、V均為條件碼標志位。它們的內容可被算術或邏輯運算的結果所改變,并且可以用于決定某條指令是否被執行,其含義如下表所示[8]:

| 標志位 | 含義 |

| N | 當兩個有符號整數運算時:N=1表示運算的結果為負數;N=0表示運算的結果為正數或零。 |

| Z | Z=1表示運算的結果為零,Z=0表示運算的結果非零。 |

| C |

可以有4種方法設置C的值: 在加法指令中(包括比較指令CMP),當結果產生了進位,則C=1,表示無符號運算發生上溢出;其他情況C=0。 在減法指令中(包括減法指令CMP),當運算中發生借位,則C=0,表示無符號運算數發生下溢出;其他情況下C=1。 對于包含移位操作的非加減運算指令,C中包含最后一次溢出的位的數值。 對于其他非加減運算指令,C位的值通常不受影響。 |

| V | 對于加減運算指令,當操作數和運算結果為二進制的補碼表示的帶符號數時,V=1表示符號為溢出,通常其他指令不影響V位。 |

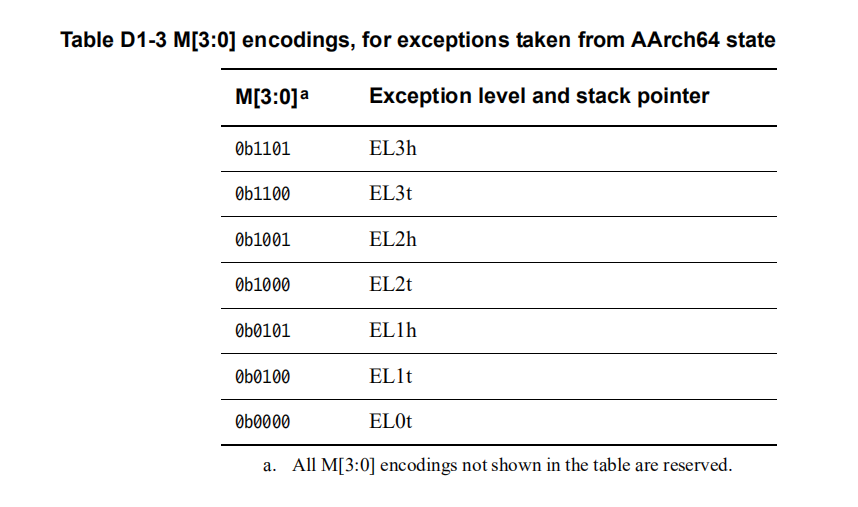

M[3:0]則用來確定異常級別和SP:

有關SPSR中各個位的詳細信息可以參考文獻[1] 1.6.4小節。

連接寄存器LR(R14)的主要作用有兩個:

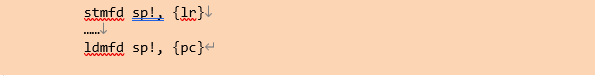

1. 保存子程序返回地址,用MOVE指令或BX指令可以用于實現返回,如MOV PC、LR或BXLR。若子程序中還需要調用子程序,則可以寫為:

第一條指令將LR中的內容入棧,最后一條將棧中保存的LR寄存器的內容存入PC中用于返回。

2. 當異常發生時,異常模式的LR用于保存異常返回地址,將LR內容入棧可以處理嵌套中斷。

PC是程序計數器,其中保存的是正在被加載的指令,而不是正在被執行的指令。例如,若指令長度為4byte,則PC指向當前正在被執行的指令的地址+8byte的地址。關于LR和PC的詳細內容可參考文獻[6]和[7]。

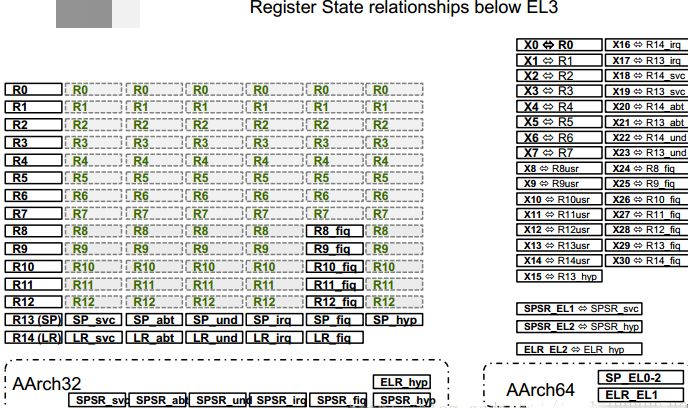

以下是異常級別EL3中使用的寄存器的例圖:

ARM架構中處理器有不同的運行模式,因此同一個功能的寄存器在不同的運行模式下可能對應不同的物理寄存器,這些寄存器被稱為備份寄存器。如SPSR_svc表示svc模式下使用的SPSR寄存器。ARM架構中常用的運行模式如下表所示[9]:

| 處理器模式 | 描述 |

| 用戶模式(User, usr) | 正常程序執行的模式 |

| 快速中斷模式(FIQ, fiq) | 用于高速數據傳輸和通道處理 |

| 外部中斷模式(IRQ, irq) | 用于通常的中斷處理 |

| 特權模式(Supervisor, svc) | 供操作系統使用的一種保護模式 |

| 數據訪問中止模式(Abort, abt) | 當數據或指令預取中止時進入該模式,用于虛擬存儲及存儲保護 |

| 未定義指令中止模式(Undefined, und) | 當執行未定義指令時進入該模式,用于支持通過軟件仿真硬件的協處理器 |

| 系統模式(System, sys) | 用于運行特權級的操作系統任務 |

ARMv8-A架構還有Monitor(mon)工作模式,用于處理器安全狀態與非安全狀態的切換,Hypervisor(hyp)模式則用于對虛擬化有關功能的支持。有關安全狀態的詳細內容在后續的文章中會介紹。

03ARM架構中的執行狀態

ARMv8-A有兩種執行模式,一種是AArch64執行模式,另一種是AArch32執行模式。執行狀態定義處理單元(Processing Element, PE)的執行環境,包括以下內容:

支持的寄存器寬度

支持的指令集

異常模型

虛擬存儲系統(Virtual Memory System Architecture, VMSA)架構

程序員模型

AArch64為64位執行狀態。對應上述內容,此執行狀態:

提供31個64位通用寄存器,其中X30用作過程鏈接寄存器(ProcedureLink Register)。

提供64位程序計數器(PC)、堆棧指針(SP)和異常鏈接寄存器(ELRs)。

提供32個128位寄存器以支持SIMD矢量和標量浮點運算。

提供單一指令集A64。

定義ARMv8異常模型,該模型最多有四個異常級別EL0-EL3,它們提供執行權限層次結構。

支持64位虛擬尋址。

定義一系列與PSTATE相關的寄存器。A64指令集包括能直接操作各種PSTATE寄存器的指令。

使用后綴命名每個系統寄存器,該后綴指示可以訪問寄存器的最低異常級別。

AArch32為32位執行狀態。對應上述內容,此執行狀態:

提供13個32位通用寄存器和一個32位PC、一個32位SP寄存器和一個32位鏈接寄存器(Link Register,LR)。鏈接寄存器用作異常鏈接寄存器和過程鏈接寄存器。其中一些寄存器有多個備份寄存器,用于不同的處理器工作模式。我們在上一期提到過,同一個功能的寄存器在不同的處理器運行模式下可能對應不同的物理寄存器,這些寄存器被稱為備份寄存器。

為從Hyp(hypervisor)模式返回的異常提供一個異常鏈接寄存器。

提供32個64位寄存器,用于對高級SIMD矢量和標量浮點計算的支持。

提供兩個指令集,A32和T32。

支持基于處理器工作模式的ARMv7-A異常模型,并將其映射到基于異常級別的ARMv8異常模型。

使用32位虛擬地址。

使用單個當前程序狀態寄存器(CPSR)保存處理器狀態。

在AArch64和AArch32執行狀態之間進行轉換稱為內部處理(interprocessing)。

04 ARMv8-A架構的異常級別和安全狀態

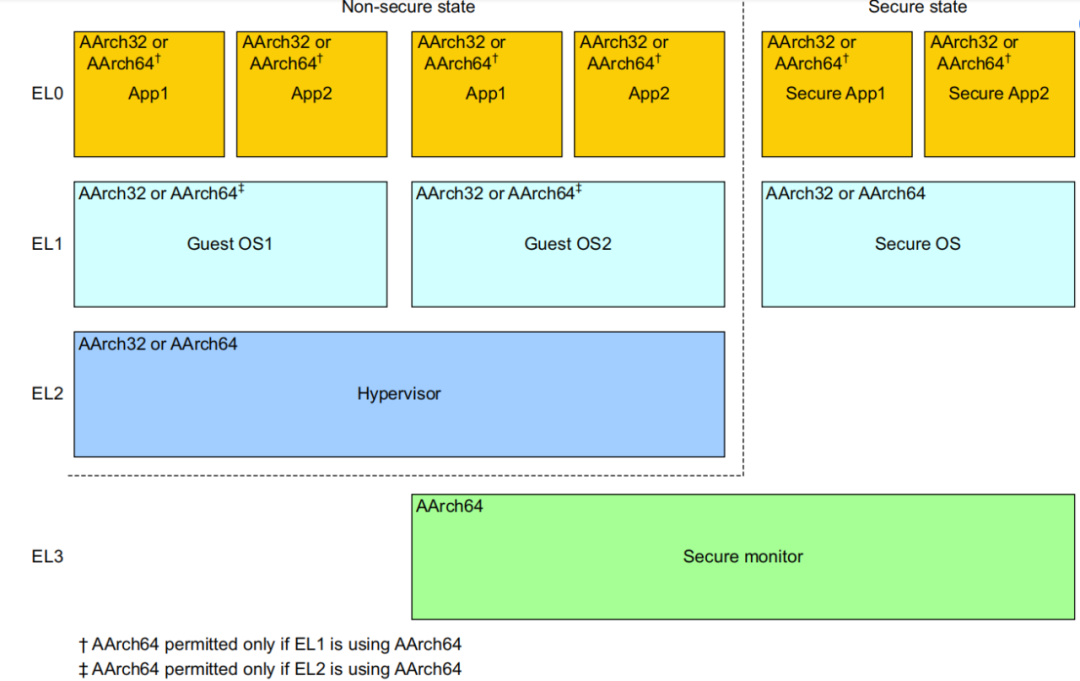

ARMv8-A有四個異常級別,從EL0到EL3。對于異常級別ELn,整數n增加表示軟件執行的特權權限變大了。EL0級別下的執行叫非特權執行(unprivileged execution)。EL1主要用于運行操作系統內核。EL2可以支持非安全操作的虛擬化。EL3則支持安全狀態和非安全狀態之間的轉換。安全狀態與ARM TrustZone技術有關[2]。安全狀態可以運行可信執行環境(TEE, Trusted Execution Environment)及安全應用,用于保障隱私數據和程序運行環境的安全性。

ARMv8-A架構并未直接指定哪些軟件應該運行在哪些異常級別,但是在通常情況下,有如異常級別的使用模型:

1.應用程序運行在EL0;

2.操作系統內核和相關功能運行在EL1;

3.Hypervisor[3]運行在EL2;

4.安全世界狀態和正常世界狀態的切換在EL3完成。

下圖反映了ARM-v8A架構中的執行狀態、安全狀態和異常級別之間關系[1]:

從圖中我們可以看出,Hypervisor相關的支持特性主要是在EL2的非安全狀態實現的。Hypervisor可以支持虛擬機之間的切換,而虛擬機主要被包含在EL1的非安全狀態和EL0的非安全狀態中。一些Guest OS可以運行在EL1狀態里,每一個Guest OS可以運行在一個虛擬機上。而應用則運行在EL0的非安全狀態中,同時也運行在Guest OS上。

審核編輯:湯梓紅。

-

處理器

+關注

關注

68文章

19384瀏覽量

230493 -

ARM

+關注

關注

134文章

9121瀏覽量

368249 -

寄存器

+關注

關注

31文章

5359瀏覽量

120806 -

STM32

+關注

關注

2270文章

10915瀏覽量

356764 -

匯編指令

+關注

關注

0文章

38瀏覽量

11501

原文標題:認識ARM:匯編、架構、異常級別和安全狀態

文章出處:【微信號:ARM與嵌入式,微信公眾號:ARM與嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

講講ARM指令集格式以及常用的ARM匯編指令

一文認識ARM匯編指令和體系架構

一文認識ARM匯編指令和體系架構

評論