幾年后,服務器可能看起來與現在有所不同,那時,存儲和處理器會被放在彼此獨立的機箱內。一種名為 CXL(Compute Express Link)的互連技術正在使這成為可能。

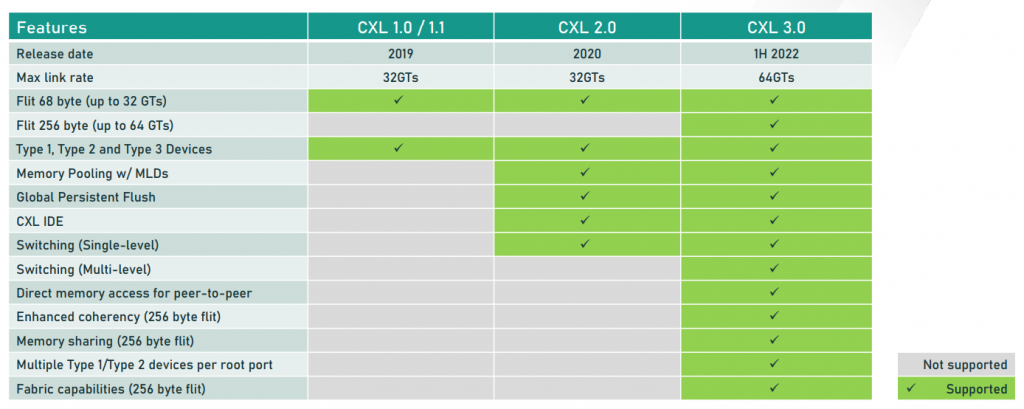

CXL是由電腦科技的行業巨頭組成的聯盟— Compute Express Link Consortium(CXL Consortium)所開發和定義的,主要成員包括英特爾(Intel)、AMD、三星(Samsung) 、SK海力士(SKHynix)、美光(Micron)、戴爾(Dell)、惠普企業(Hewlett Packard Enterprise)、Microchip Technolog等。CXL 協定發展經歷過1.0、1.1、2.0、以及最新的3.0版本,如今市場上已經陸續出現支援CXL 1.1 和2.0 的產品,3.0 協定還在開發中;協定本身更是吸引了一群大型科技公司積極參與其中。

該技術的升級規范,3.1版,于本周發布。更新提供了更快、更安全的計算環境和更強大的技術基礎,可將數據中心轉變為巨型服務器。

新規范將支持 DDR6 內存,該內存仍在開發中。DDR 標準制定組織 JEDEC 尚未廣泛討論 DDR6。

目前,英特爾和AMD的服務器芯片支持DDR5,但尚未指導芯片組對DDR6的支持。大多數硬件和云提供商都支持 CXL。

CXL 3.1 是一年多前推出的 CXL 3.0 的增量改進。CXL 協議是系統中芯片、內存和存儲之間的通信鏈路。

CXL 3.0 規范基于 PCIe 6.0,數據傳輸速度高達每秒 64 千兆。它比其前身 CXL 2.0 快兩倍,CXL 2.0 基于 PCIe 5.0,并且正在進入服務器系統。

隨著 AI 等技術的普及,CXL 已成為芯片組的重要組成部分,機器學習應用程序需要大量內存和帶寬,CXL 允許跨服務器池化存儲和內存。

CXL 3.1 協議可以打開更多的點對點通信,將內存和存儲分解到單獨的機箱中,通過傳統網絡和互連技術進行分解的討論已經討論了10年,CXL 提供了提供各種計算資源所需的可擴展性。

首先,CXL 3.1 規范提供了一個支持新型內存的開放標準,可以更有效地將數據重新路由到內存和加速器。

一項重要的改進是將結構上的內存資源匯集到一個全局地址下,該功能稱為全局集成內存,對于在內存和其它資源之間建立更快的連接非常重要。

加速器還將能夠直接與內存資源通信,基于端口的路由的新功能有助于更快地訪問內存資源。

CXL 3.1 還提供了在受保護環境中執行數據的指令,引入這項技術是為了支持機密計算,英特爾的 Sapphire Rapids 中已經引入了 TDX 指令,AMD的芯片中引入了 SNP-SEV 功能。

新規范定義了一種安全協議,該協議可保證數據在內存、處理器和存儲之間移動時擴展安全環境。

該協議將檢測需要對連接進行身份驗證以打開硬件保險庫,以訪問代碼或信息的環境。這些信息可能位于處理器、內存或存儲上。英特爾、Microsoft 和其它公司有不同類型的證明方法來驗證在安全環境中訪問數據的連接。

CXL的功能與特性詳解

CXL是一種用于加速CPU 和設備之間資料傳輸的協定,主要應用于人工智能和機器學習等領域,以解決在這些應用中需要高效率的資料交互的需求。隨著PCIe協定的發展,到了5.0版本后,像需要大量IO 資料交互的人工智能應用,開始遇到性能瓶頸的問題。為了突破這個瓶頸,引入了CXL協定的概念。

首先,CXL 協定解決了共享RAM的問題,在支援PCIe 協定的設備中,每個設備都擁有自己的RAM,但這些RAM無法被CPU 統一編址,因此無法直接進行調用,這導致了延遲的問題;CXL協定引入了共享RAM 的概念,允許CPU 對所有設備上的RAM 進行統一編址,從而實現了彼此之間的互相調用。

其次,CXL 協定解決了高延遲的問題,例如:CPU 和GPU之間的資料交互,需要經過多個節點,包括CPU 緩沖(Cache)、CPU RAM、PCIe 鏈路、GPU RAM和GPU Cache 等,這些節點和IO 頻寬限制導致了延遲的增加;為了降低延遲,我們希望CPU 能夠直接存取GPU 的RAM,從而避免了繁復的資料傳輸過程。CXL的功能特性中,CXL 2.0 版本引入了FLIT(可變長度介面傳輸,Flexible-Length Interface Transport) based transfers 功能,使用544 位元的FLIT 模式進行資料傳輸,這種模式可以降低資料傳輸的延遲,類似于NVMe 協定中的隊列概念。

CXL的三個子協定及其對應的三種設備

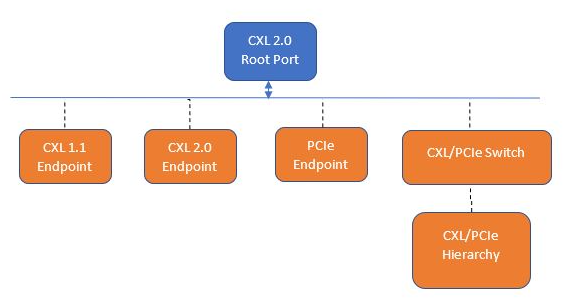

CXL有三個子協定:CXL.io、CXL.cache、CXL.memory。

CXL.io 和CXL.cache 是CXL 協定中的兩個子協定,它們的功能和用途有所不同,主要是為了引入非對稱的概念;CXL.io 類似于PCIe 的事件(event),主要用于初始化、鏈接、設備發現、列舉以及寄存器(register) 的存取,從某種程度上說,它可以看作是PCIe事件的一個變種。

CXL.cache 則是用于設備去使用主機的主要RAM,這表示設備可以直接存取主機的RAM,并且需要與CPU 的Cache 保持資料一致性;如果沒有有效的通訊和同步,可能會出現RAM 使用沖突或不存在的問題。

另一方面,CXL.memory則是CPU 使用設備上的RAM;在這種情況下,CPU可以直接存取設備上的RAM,而不需要與設備的Cache 進行交互;這是因為CPU 的Cache 直接使用設備上的RAM,因此可以直接進行通訊,而無需額外的同步操作。

總結來說,CXL.io 和CXL.cache 的使用方向和目的不同,因此被拆分為兩個子協定;CXL.io 類似于PCIe 事件,用于設備和主機之間的通訊和初始化過程;而CXL.cache 則用于設備存取主機的RAM 并保持資料一致性;另一方面,CXL.memory 則是CPU 直接使用設備上的RAM,無需與設備的Cache 進行交互,這樣的設計使得CXL 協定在不同的使用情境中更具靈活性和效能。

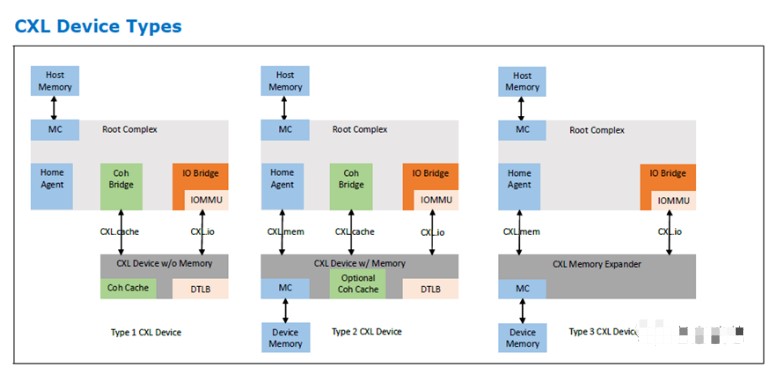

基于這三個子協定,衍生出三種不同的設備類型;其中,CXL.io 是所有設備都需要的協定,因為它包含了設備的列舉過程,使其能夠被識別和通信;另外兩個協定則是進行組合以產生更具特定功能的設備。

第一種設備類型是智慧網卡,它有Cache,但沒有獨立的RAM;相反,它直接使用CPU 的內存,這使得在CPU 處理資料時非常迅速;由于記憶體就在設備內部,它可以直接讀取和處理資料,這是它的優勢。

第三種設備類型則只擁有RAM,而沒有Cache;換句話說,它實際上是CPU 的一種無限擴展的內存;傳統CPU 主機板上的內存插槽有限,且主機板的空間有限,即使提高單條內存的容量也有限制。

審核編輯:黃飛

-

cpu

+關注

關注

68文章

10863瀏覽量

211786 -

內存

+關注

關注

8文章

3025瀏覽量

74056 -

服務器芯片

+關注

關注

2文章

122瀏覽量

19256 -

機器學習

+關注

關注

66文章

8418瀏覽量

132646 -

ddr6

+關注

關注

0文章

6瀏覽量

7484

原文標題:最新CXL規范支持DDR6

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一窺CXL協議

一文解析CXL系統架構

CXL事務層的結構是由哪些部分組成的

CXL內存協議介紹

一文詳解CXL鏈路層格式的定義

CXL事務層詳解

CXL協議和標準介紹, CXL2.0和3.0有什么新功能?

CXL 2.0設備發現的迷人路徑

MIFARE DESFire EV3特性和功能與其他MIFARE的比較

關于CXL的功能與特性詳解

關于CXL的功能與特性詳解

評論