作者:Paul McLellan,來源:Cadence楷登PCB及封裝資源中心

莎士比亞在《羅歐與朱麗葉》中寫道:“名字有何重要?玫瑰不叫玫瑰,依舊芳香如故。”

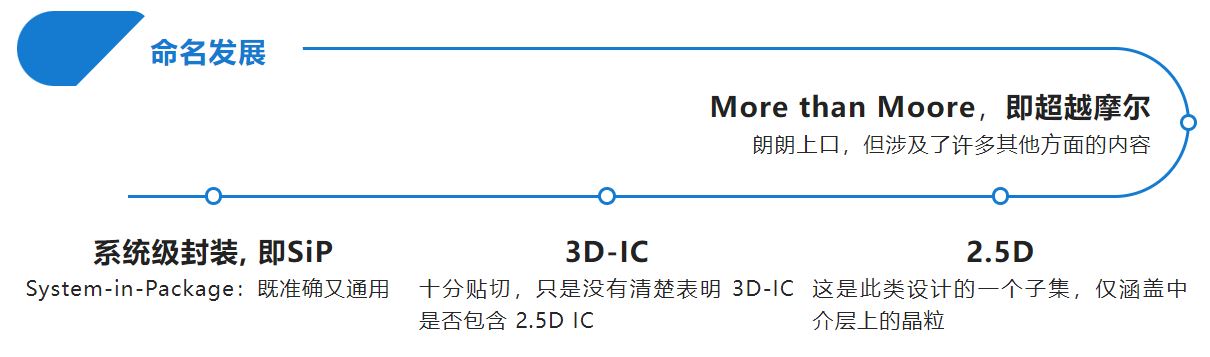

然而在過去 10 年中,尤其是過去 5 年左右,每當我們將不止一個晶粒置于一個封裝內時,我們就想為其增加一個新的命名:

……此外還有很多不同的專用名詞,顯然不適合用作整個行業的通用名稱。

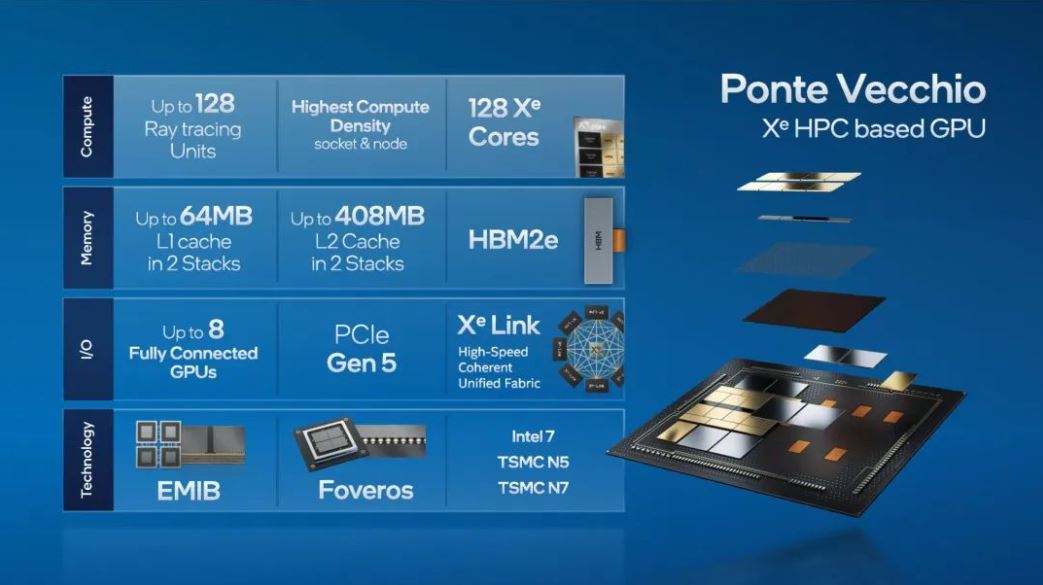

最新出現的一個名稱是“異構集成(heterogeneous integration)”或“3D 異構集成(3D heterogeneous integration)”,目前的關注度越來越高。這個詞涵蓋的內容非常豐富,從向處理器添加"高帶寬存儲器 (HBM) "堆棧,到 Intel的 Ponte Vecchio 產品(復雜性方面的登峰造極者)——

在 5 個不同的制程節點上裝進了超過 47 塊小芯片(chiplets),晶體管總數量超過 1000 億!

這是當之無愧的異構集成!

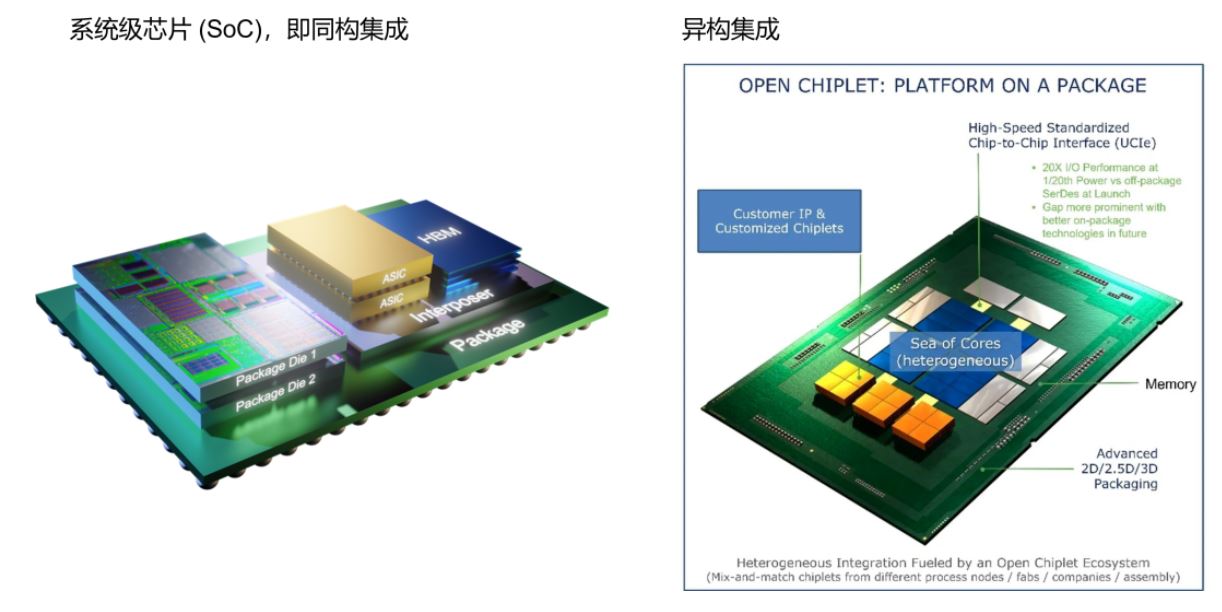

但是,“異構集成”這一詞語依然存在一個問題:我們該如何稱呼采用這種技術的設計?我認為,“系統級封裝”(SiP) 一詞就很貼切。所以說,異構集成是用于創建 SiP 的技術。

顯然,與異構集成形成鮮明對比的是同構集成,即系統級芯片 (SoC)。同構集成最大的缺點在于,必須在同一個半導體制程節點中完成所有組件。如果需要集成差別較大的模塊,例如光子學、射頻、模擬、DRAM、MRAM 等等,這項工作就會變得非常棘手。

挑戰來自成本方面,而不是技術。例如,我們知道如何將 DRAM 擺放在邏輯晶粒上,但實際上,即使芯片上有非 DRAM 的部分(DRAM 掩膜是空白的),我們也要為它們支付成本。同構集成的另一個問題是晶粒的尺寸可能會非常大。如果尺寸過大,晶粒可能會超出光刻極限,最終將無法制造。但即便沒有超出極限,如果芯片面積相同,與四個單獨的小晶粒相比,大晶粒的良率也會比較差。

《異構集成 (HI) 與系統級芯片 (SoC) 有何區別?》一文詳細講述了這兩種設計工藝之間的區別以及各自的優勢和注意事項,歡迎點擊閱讀。

COTS 小芯片

自動化程度更高的異構集成流程存在很多技術挑戰。但最值得關注的問題是在商業領域。在此強調:這些問題暫時還沒有答案。

COTS 指的是“commercial off the shelf(即商用現成品)”。通常情況下,它用于國防等專門行業,將可以輕松購買的芯片與必須為特定用途設計的專門芯片區分開來。關于異構集成,最值得關注的問題之一是 COTS 小芯片是否可用。或許最極端的情況是,能否用Intel的微處理器、NVIDIA的 GPU 和Qualcomm的 5G 調制解調器來構建一個 SiP?

目前已經有一些 COTS 小芯片(或小芯片堆棧)是可用的,如高帶寬存儲器 (HBM) 和 CMOS 圖像傳感器 (CIS) 視覺/AI 子系統。

為了擴大這一市場,讓 COTS 小芯片可用,有幾個重大問題需要解決:

小芯片將以芯片的形式提供,還是僅僅作為授權 IP 提供?

如果有實際的小芯片可用,那么誰將持有庫存?

這是否仍將是一個“酒香不怕巷子深”的市場,依然要按需生產小芯片,只有在收到確定的訂單后才會進行生產?

誰來管理小芯片的生產運營?

是否會出現新的公司來創造/服務這個市場?

這些問題在很大程度上歸結為誰將承擔財務風險:最終用戶、中間商(如分銷商)、設計小芯片的公司、代工廠,還是其他公司或供應商。就像任何價值鏈一樣,所有參與者都希望將自己獲得的收入/利潤最大化,并試圖將其他供應商商品化。當然,如果每個人在這方面都過于激進,那么就很有可能釀成殺雞取卵的悲劇。或者變成揠苗助長,那么這種市場將永遠不會成熟。

審核編輯 黃宇

-

芯片

+關注

關注

455文章

50817瀏覽量

423676 -

COTS

+關注

關注

0文章

23瀏覽量

10841 -

異構集成

+關注

關注

0文章

34瀏覽量

1890

發布評論請先 登錄

相關推薦

2.5D/3D封裝技術升級,拉高AI芯片性能天花板

3D打印技術,推動手板打樣從概念到成品的高效轉化

人工智能應用中的異構集成技術

DMD芯片在3D打印中的創新應用

3D異構集成重塑芯片格局

君正X2600在3D打印機上的優勢:多核異構,遠程控制與實時控制

3D封裝熱設計:挑戰與機遇并存

在微芯片上使用3D反射器堆棧有助于加快6G通信的發展

裸眼3D頻頻“出圈” 電信積極布局并發力裸眼3D領域

3D HMI應用場景和發展趨勢

3D異構集成與 COTS (商用現成品)小芯片的發展問題

3D異構集成與 COTS (商用現成品)小芯片的發展問題

評論