引言

估計很多新手工程師在設計開關電源計算變壓器時發炸現,把電源的開關頻率提高后變壓器磁芯更加不容易飽和,或者說可以用更小的磁性做出同樣功率的電源,甚至在想把開關頻率無限制提高來無限制縮小變壓器的體積。

但實際上一般開關電源的頻率都不會特別高,也不可能使頻率無限提高,其中到底有哪些原因?請看下文!

器件限制、損耗、EMI、PCB布局難度提升等問題都是制約開關頻率無限提升的因素,下面稍微展開來講一下!

器件的限制

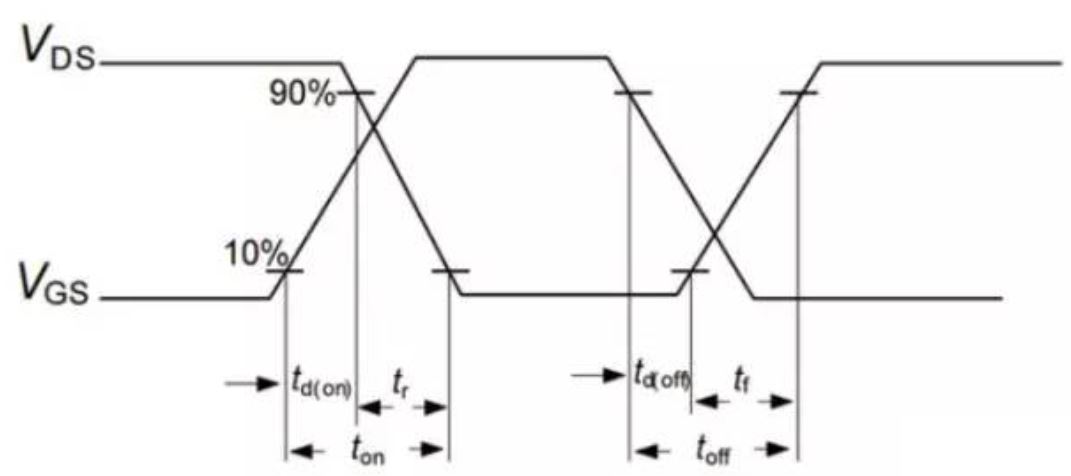

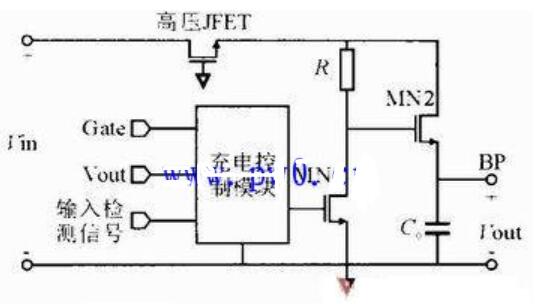

對于一個開關管來說,在實際應用中,不是給個驅動就開,驅動撤掉就關了。它有開通延遲時間(tdon),上升時間(tr),關斷延遲時間(tdoff),下降時間tf,對應的波形如下:

通俗的講,開關管開通關斷不是瞬間完成的,需要一定的時間,開關管本身的開關時間就限制了開關頻率的提升。

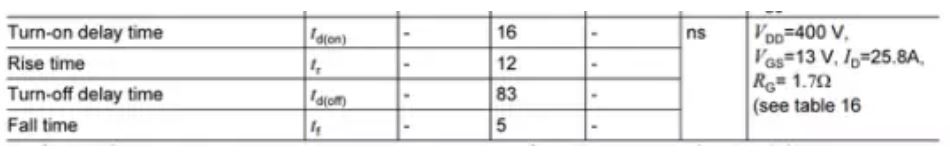

曾經筆者在delta用在3kW的逆變器上的一款600V的coolmos為例。看看這些具體的開關時間是多少?

那么對于這個mos管來說,它的極限開關頻率(在這種極限情況下,mos管剛開通就關斷)fs=1/(16+12+83+5)ns=8.6MHz,當然,在實際應用中,由于要調節占空比,不可能讓開關管一開通就關斷,所以實際的極限頻率是遠低于8.6MHz的,所以器件本身的開關速度是限制開關頻率的一個因素。

開關損耗

當然,隨著器件的進步,開關管開關的速度越來越快,尤其是在低壓小功率場合,如果僅考慮器件本身的開關速度,開關頻率可以run得非常高,但實際并沒有,限制就在開關損耗上面。

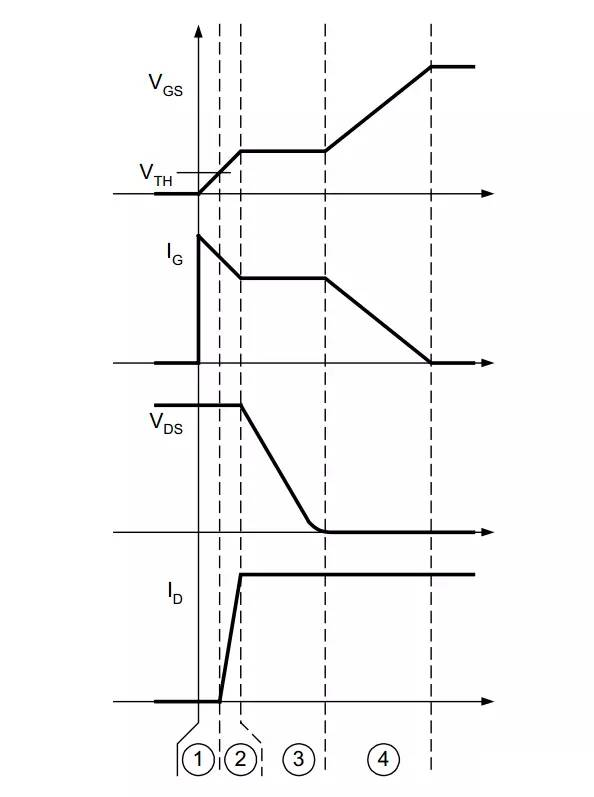

下面給出開關管實際開通的時候對應的波形圖

可以看到,開關管每開通一次,開關管DS的電壓(Vds)和流過開關管的電流(Id)會存在交疊時間,從而造成開通損耗,關斷亦然。假設每次開關管每開關一次產生的能量損耗是一定的,記為Esw,那么開關管的開關損耗功率就為Psw=Esw*fs,顯然,開關頻率越高,開關損耗越大。5M開關頻率下開關損耗比500K要大10倍,這對于重視效率的開關電源來說,顯然是不可接受的。所以,開關損耗是限制開關頻率的第二因素。

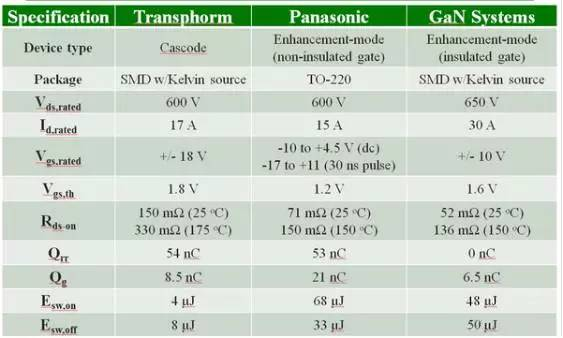

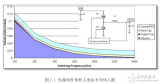

開關損耗確實是限制因素之一,但是氮化鎵器件的推出已經讓開關損耗在1-3Mhz這個范圍內變得可以接受,我下面附一張圖片,這是三家公司推出的650V的GaN device,可以看出最好的管子開通損耗已經4uJ,關斷損耗在8uJ(測試條件在400V, 12A),甚至有家公司的650V的管子基本可以和Transphorm平齊。而同電壓電流等級的硅器件很多管子都還在以mJ為單位。

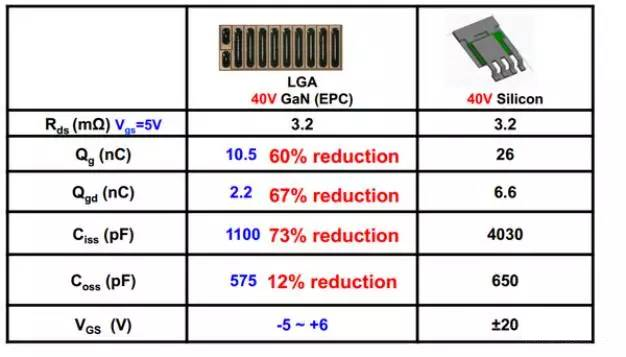

下面在貼出一張低壓氮化鎵和硅器件的比較,可以看出,總體來說,驅動損耗也會變得很小。

還有一點很重要,寬禁帶半導體的工作結溫很高,以目前的工藝來說,Sic的結溫可以工作到200°,氮化鎵可以工作到150°。而硅器件呢,我覺得最多100°就不得了。結溫高,意味著相同損耗下,需要給寬禁帶半導體設計的散熱器表面積要小很多,何況寬禁帶半導體的損耗本身還小。

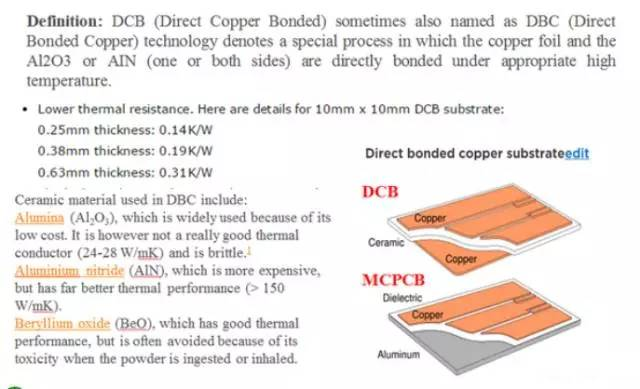

是開關頻率的提高,往往只能使用QFN或者其他一些表貼器件減少封裝寄生參數,這給散熱系統帶來了極大的挑戰,原來To封裝可以加散熱器,減少到空氣對流的熱阻,而現在不行了。所以如果想在高頻下工作,第一問題就是解決散熱,把高開關損耗導出去,尤其是在kW級別,散熱系統非常重要。現在學界解決這個問題的手段偏向于把器件做成獨立封裝,采用一種叫DCB的技術,用陶瓷基板散熱,器件從陶瓷上表面到下表面的熱阻基本為0.4°C/W(有些人也用metal core PCB, 但是要加絕緣層,熱阻一般在4°C/W),而FR4為20°C/W。

半導體不斷在發展,開關損耗也在顯著下降,而封裝越來越小,現在來看,我們要做的是怎么把那些熱量從那么小的表貼封裝下散出去。

磁元件損耗

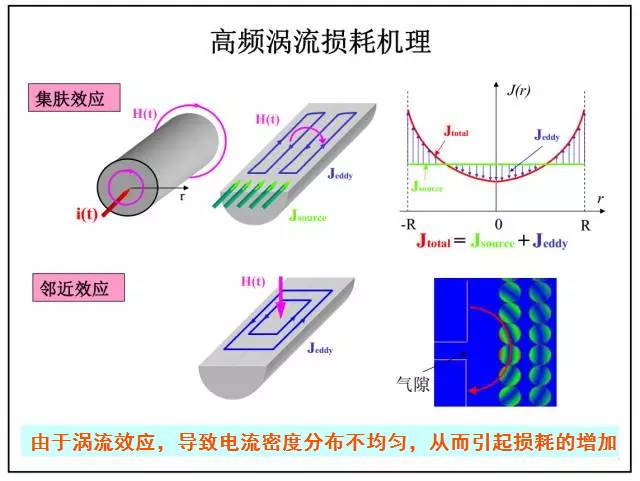

繞組的趨膚效應和臨近效應。在變壓器的高頻工作時,影響更加嚴重。會引起較大的繞組渦流耗損,當然開關頻率提高,繞組的匝數會降低。相應的繞組交流阻抗變大了,但是繞線長度減少了。問題貌似也不會很大,諧振半橋應用,我們經常會選200KHZ的頻率。這樣磁性元件的體積和耗損,是一個比較合適的范圍。

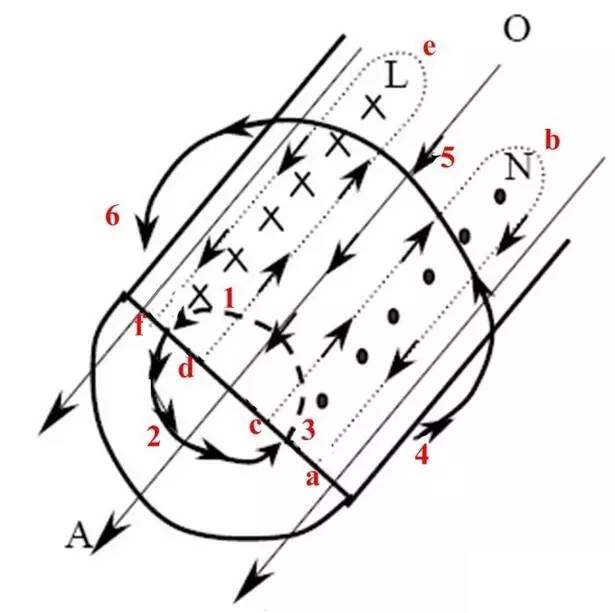

變壓器的鐵損主要由變壓器渦流損耗產生,如下圖所示,給線圈加載高頻電流時,在導體內和導體外產生了變化的磁場垂直于電流方向(圖中1→2→3和4→5→6)。根據電磁感應定律,變化的磁場會在導體內部產生感應電動勢,此電動勢在導體內整個長度方向(L面和N面)產生渦流(a→b→c→a和d→e→f→d),則主電流和渦流在導體表面加強,電流趨于表面,那么,導線的有效交流截面積減少,導致導體交流電阻(渦流損耗系數)增大,損耗加大。

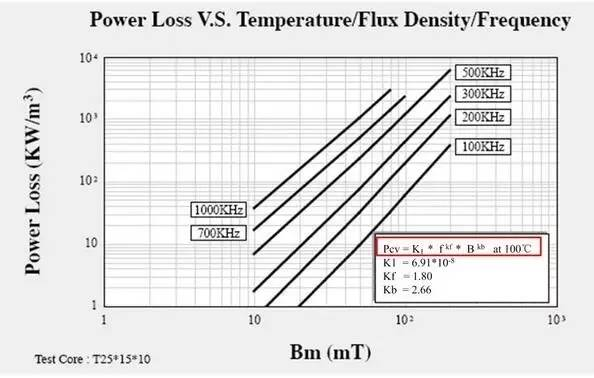

如下圖所示,變壓器鐵損是和開關頻率的kf次方成正比,又與磁性溫度的限制有關,所以隨著開關頻率的提高,高頻電流在線圈中流通產生嚴重的高頻效應,從而降低了變壓器的轉換效率,導致變壓器溫升高,從而限制開關頻率提高。

軟開關的困難

題主提到了軟開關,沒錯,軟開關確實是解決開關損耗的有力手段。而在各種研究軟開關的paper上,提出了無數種讓人眼花繚亂的軟開關方案,似乎軟開關能解決一切問題。但是實際工程應用和理論分析不同,實際工程追求的是低成本,高效率,高可靠性,那些需要添加一堆輔助電路,或者要非常精確控制的軟開關方案在實際工程中其實都是不太被看好的,所以即使到現在,在工業界最常應用軟開關的拓撲也只要移相全橋和一些諧振的拓撲(比如LLC),至于題主提到的flyback,沒錯,我也聽說過有準諧振的flyback(但沒研究過),但即使有類似的方案,對于能不能真正工程應用,題主也需要從我上面提到的幾個問題去考量一下。

ps,對于小功率高頻電源,現在class E非常火,我覺得它火的原因就是電路簡單,所以才能被工業界接受,題主有興趣可以去研究下。

高頻化帶來的一系列問題

假設上面的一系列問題都解決了,真正做到高頻化還需要解決一系列工程上的問題,比如在高頻下,電路的寄生參數往往會嚴重影響電源的性能(如變壓器原副邊的寄生電容,變壓器的漏感,PCB布線之間的寄生電感和寄生電容等等),造成一系列電壓電流波形震蕩和EMI的問題,如何消除寄生參數的影響,甚至進一步地,如何利用寄生參數為電路服務,都是有待研究的問題。

ps,對于高頻化應用的實際工程應用的問題,還有很重要的一塊是高頻驅動電路的設計。

當然,隨著新器件(SiC, GaN)的興起,開關電源高頻化的研究方興未艾,開關電源的高頻化一定是趨勢,而且有望給電力電子帶來又一次革命。讓我們拭目以待。

EMI和干擾,pcb布局難度增大

在我接觸EMI前,很多老工程師以他們有豐富的EMI調試經驗來鄙視我們這些菜鳥,搞的我一直以為EMI是門玄學,也有很多人動不動就拿EMI出來嚇人。我想說EMI確實很難理解,很難有精確的紙面設計,但是通過研究我們還是能知道大概趨勢指導設計,而不是一些工程嘴里完全靠trial and error的流程。我先給出結論,EMI確實和開關頻率不成線性關系,某些開關頻率下,EMI濾波器的轉折頻率較高,但是總體趨勢而言,是開關頻率越高,EMI體積越小!

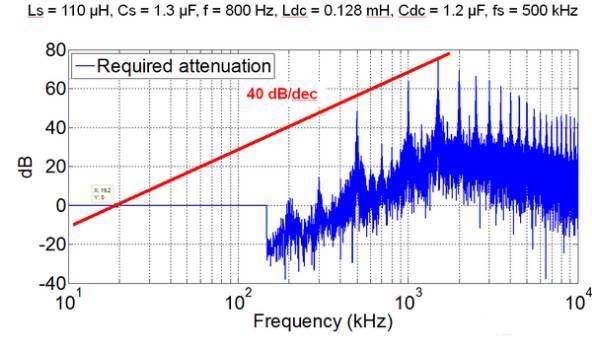

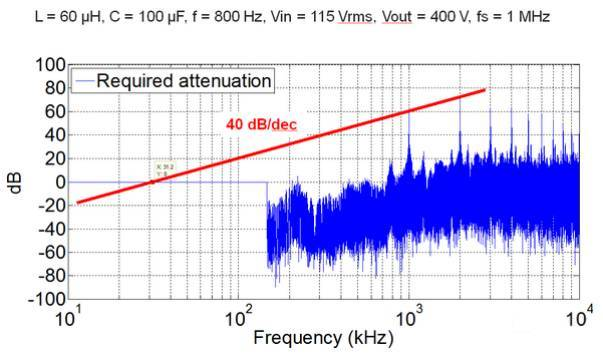

我知道很多人可能開始噴我了,怎么可能,di/dt和dv/dt都大了,怎么可能EMI濾波體積還小了。我想說一句,共模和差模濾波器的沒有區別,相同的截止頻率下,高頻的衰減更大!就算你高頻下共模噪聲越大,但是你的記住,這個頻率下LC濾波器的衰減更大,想想幅頻曲線吧。為了說明這個結論,我給出一些定量分析結果。這些EMI分析均基于AC/DC三相整流,拓撲為維也納整流。我分別給出了1Mhz和500Khz的共模噪聲,可以看出,500khz共模濾波器需要的截止頻率為19.2kHz,1MHz為31.2kHz。

這張圖給出了不同頻率下共模和差模濾波器轉折頻率的關系,可以看出,一些低頻點EMI濾波器體現出了非常好的特性。例如70Khz,140Khz。而這兩個開關頻率是工業界常用的兩個開關頻率,非常討巧,因為EMI噪聲測試是150KHz到30MHz。不過這個也與拓撲有關。

假設上述的功率器件損耗解決了,真正做到高頻還需要解決一系列工程問題,因為在高頻下,電感已經不是我們熟悉的電感,電容也不是我們已知的電容了,所有的寄生參數都會產生相應的寄生效應,嚴重影響電源的性能,如變壓器原副邊的寄生電容、變壓器漏感,PCB布線間的寄生電感和寄生電容,會造成一系列電壓電流波形振蕩和EMI問題,同時對開關管的電壓應力也是一個考驗。

小結

不是開關頻率越高,功率密度就越高,目前這個階段來說真正阻礙功率密度提高的是散熱系統和電磁設計(包括EMI濾波器和變壓器)和功率集成技術。

慎重選擇開關頻率,開關頻率會極大的影響整個變化器的功率密度,而且針對不同器件,拓撲,最佳的開關頻率是變化的。

高頻確實產生很多很難解決的干擾問題,往往要找到干擾回路,然后采取一些措施。

為了繼續維持電力電子變換器功率密度的增長趨勢,高頻肯定是趨勢。只是針對高頻設計的電力電子技術很不成熟,相關配套芯片沒有達到要求,一些高頻的電磁設計理論不完善和精確,使用有限元軟件分析將大大增加開發周期。

要提高開關電源產品的功率密度,首先考慮的是提高其開關頻率,能有效減小變壓器、濾波電感、電容的體積,但面臨的是由開關頻率引起的損耗,而導致溫升散熱設計難,頻率的提高也會導致驅動、EMI等一系列工程問題。

文章來源:電子工程專輯

審核編輯 黃宇

-

變壓器

+關注

關注

159文章

7483瀏覽量

135298 -

開關電源

+關注

關注

6462文章

8337瀏覽量

482051 -

頻率

+關注

關注

4文章

1500瀏覽量

59229

發布評論請先 登錄

相關推薦

開關電源老化炸機,求大神

開關電源設計的那些事,如何防止初次上電“炸機”?

如何避免開關電源初次上電“炸機”?學會這一招即可搞定

開關電源測試,請問有辦法避免上電炸機嗎?

制約開關頻率無限提升的因素及原因分析

開關電源的開關頻率怎么測試?開關電源測試系統如何助力?

把開關電源頻率無限提升,會炸嗎?

把開關電源頻率無限提升,會炸嗎?

評論