最近部門來了一個日本回來的同事,雖然他盡量用非常Poor的中文給我解釋一些東西,其中還夾雜著一些英文讓我很受挫,于是最近來學一下WAT中的常用的單詞含義。

直接去查縮寫、查單詞很難去記住,要把具體的東西放在具體的場景,引發知識的連接才會在腦子里留下一定的映像。

感興趣的一起來學習一下這篇不錯的文章吧。

注釋是我查詢記錄,如有不妥,歡迎指出修正。

正文

CP是把壞的Die挑出來,可以減少封裝和測試的成本。可以更直接的知道Wafer 的良率。

FT是把壞的chip挑出來;檢驗封裝的良率。

現在對于一般的wafer工藝,很多公司多把CP給省了,減少成本。

CP對整片Wafer的每個Die來測試,而FT則對封裝好的Chip來測試。 CP Pass 才會去封裝。然后FT,確保封裝后也Pass。

WAT是Wafer Acceptance Test,對專門的測試圖形(test key)的測試,通過電參數來監控各步工藝是否正常和穩定;

CP是wafer level的chip probing,是整個wafer工藝,包括backgrinding和backmetal(if need),對一些基本器件參數的測試,如vt(閾值電壓),Rdson(導通電阻),BVdss(源漏擊穿電壓),Igss(柵源漏電流),Idss(漏源漏電流)等,一般測試機臺的電壓和功率不會很高;

FT是packaged chip level的Final Test,主要是對于這個(CP passed)IC或Device芯片應用方面的測試,有些甚至是待機測試;

Pass FP還不夠,還需要做process qual 和product qual CP 測試對Memory來說還有一個非常重要的作用,那就是通過MRA計算出chip level 的Repair address,通過Laser Repair將CP測試中的Repairable die 修補回來,這樣保證了yield和reliability兩方面的提升。

Pass FP:這里的"Pass FP"可能指的是通過Failure Analysis(故障分析)的過程。在這個過程中,對可能存在的故障或問題進行檢測和識別,并對其進行修復和改進。

process qual:過程質量保證(process qual)是指通過嚴格控制生產或服務過程的質量標準,以確保產品或服務的質量達到預期水平。

product qual:產品品質保證(product qual)是一種質量控制方法,以確保產品或服務的質量符合客戶的需求和期望。

CP 測試:這里的"CP"可能指的是Copy Protection(復制保護)。這是一種保護數字內容免遭未經授權的復制、分發或展示的技術。這種測試的目的是為了確保復制保護機制的有效性和安全性。

MRA:MRA可能指的是Memory Read Access(內存讀取訪問)。這通常涉及到在計算機內存中讀取數據的過程。

chip level:在電子工程中,"chip level"通常指的是在芯片級別進行操作或分析。這可能涉及到對集成電路(Integrated Circuit)或其他微型電子設備進行測試、修復或改進。

Rerepair address:這可能指的是在內存中用于修復或替換數據的地址。這通常涉及到數據存儲和訪問的過程。

Laser Repair:激光修復是一種用于修復或替換半導體芯片中損壞部分的工藝。這種技術使用激光束來消除損壞的電路元件,并替換為新的、健康的元件。

yield:這里指的是生產率或產量。這是衡量生產效率或生產出的產品數量的指標。

reliability:可靠性是指產品或服務在特定條件下、在一定時間內完成特定功能的能力。這里的"reliability"指的是產品或服務的可靠性水平。

?CP是對wafer進行測試,檢查fab廠制造的工藝水平?FT是對package進行測試,檢查封裝廠制造的工藝水平

對于測試項來說,有些測試項在CP時會進行測試,在FT時就不用再次進行測試了,節省了FT測試時間;

但是有些測試項必須在FT時才進行測試(不同的設計公司會有不同的要求)

一般來說,

?CP測試的項目比較多,比較全;?FT測的項目比較少,但都是關鍵項目,條件嚴格。

但也有很多公司只做FT不做CP(如果FT和封裝yield高的話,CP就失去意義了)。

在測試方面,CP比較難的是探針卡的制作,并行測試的干擾問題。

FT相對來說簡單一點。

還有一點,memory測試的CP會更難,因為要做redundancy analysis,寫程序很麻煩。

CP在整個制程中算是半成品測試,目的有2個,

?1是監控前道工藝良率,?2是降低后道成本(避免封裝過多的壞芯片),

其能夠測試的項比FT要少些。

最簡單的一個例子,碰到大電流測試項CP肯定是不測的(探針容許的電流有限),這項只能在封裝后的FT測。

不過許多項CP測試后FT的時候就可以免掉不測了(可以提高效率),所以有時會覺得FT的測試項比CP少很多。

應該說WAT的測試項和CP/FT是不同的。

CP不是制造(FAB)測的! 而CP的項目是從屬于FT的(也就是說CP測的只會比FT少),項目完全一樣的;不同的是卡的SPEC而已;

因為封裝都會導致參數漂移,所以CP測試SPEC收的要比FT更緊以確保最終成品FT良率。

還有相當多的DH把wafer做成幾個系列通用的die,在CP是通過trimming來定向確定做成其系列中的某一款,這是解決相似電路節省光刻版的最佳方案;

所以除非你公司的wafer封裝成device是唯一的,且WAT良率在99%左右,才會盲封的。

這里的“DH”指的是“Design House”,即設計公司。這些公司通常為電子設備制造商提供芯片設計和芯片組解決方案。它們可能會將wafer(晶圓)做成幾個系列通用的die(芯片),以提供給不同的客戶使用。

“WAT”可能是指“Wafer Acceptance Test”,即晶圓接受測試。這是在半導體制造過程中進行的一種測試,用于確保晶圓的質量和可靠性。

“device”在這里指的是通過WAT測試后的芯片設備,即將wafer封裝成一個個獨立的芯片。

“盲封”在這里可能指的是在不知道芯片具體功能或規格的情況下進行封裝。通常情況下,為了確保封裝的質量和可靠性,需要進行嚴格的測試和驗證。如果公司的晶圓封裝成芯片的過程是唯一的,且WAT良率在99%左右,那么就可以進行盲封,即在不了解芯片具體功能或規格的情況下進行封裝。

據我所知盲封的DH很少很少,風險實在太大,不容易受控。

?WAT:wafer level 的管芯或結構測試?CP:wafer level 的電路測試含功能?FT:device level 的電路測試含功能CP=chip probingFT=Final Test

CP 一般是在測試晶圓,封裝之前看,封裝后都要FT的。不過bump wafer是在裝上錫球,probing后就沒有FT

FT是在封裝之后,也叫“終測”。意思是說測試完這道就直接賣去做application。

?CP用prober,probe card。FT是handler,socket CP比較常見的是room temperature=25度,FT可能一般就是75或90度 CP沒有QA buy-off(質量認證、驗收)

CP兩方面

?1.監控工藝,所以呢,覺得probe實際屬于FAB范疇?1.控制成本。Financial fate。我們知道FT封裝和測試成本是芯片成本中比較大的一部分,所以把次品在probe中reject掉或者修復,最有利于控制成本

?FT: 終測通常是測試項最多的測試了,有些客戶還要求3溫測試,成本也最大。 至于測試項呢,?1.如果測試時間很長,CP和FT又都可以測,像trim項,加在probe能顯著降低時間成本,當然也要看客戶要求。?1.關于大電流測試呢,FT多些,但是我在probe也測過十幾安培的功率mosfet,一個PAD上十多個needle。?1.有些PAD會封裝到device內部,在FT是看不到的,所以有些測試項只能在CP直接測,像功率管的GATE端漏電流測試Igss CP測試主要是挑壞die,修補die,然后保證die在基本的spec內,function well。 FT測試主要是package完成后,保證die在嚴格的spec內能夠function。

關于3溫測試:這是一種特殊的測試方法,它要求在三個不同的溫度下對產品進行測試,通常是常溫(25℃左右)、高溫(如60℃或70℃)和低溫(如-20℃或-40℃)。這種測試的目的是為了檢查產品在不同溫度下的性能和可靠性,以確保產品能在不同環境下正常工作。

關于Trim項:Trim在這里可能指的是微調或者校準的意思。在電子產品測試中,Trim測試通常指的是對一些可以調整的參數進行微調或校準,以確保產品的性能達到最佳。例如,在測試一個頻率調整的振蕩器時,Trim測試可能包括在不同的頻率設置下測試振蕩器的性能,以找到最佳的工作頻率。

關于加在probe能顯著降低時間成本:這可能指的是在測試過程中使用一些特定的測試工具或設備(probe),這些工具或設備可以更快地完成某些測試,從而顯著降低測試所需的時間和成本。例如,使用自動化測試設備進行功能測試,可以比手動測試更快、更準確地完成測試,從而降低測試時間和成本。

關于客戶要求:客戶要求通常是指在產品設計和生產過程中,客戶對產品的性能、功能、質量、可靠性等方面的要求。這些要求可能會影響測試的策略和方法,例如客戶可能要求進行更嚴格的測試以保證產品的質量和可靠性。

?CP的難點在于,如何在最短的時間內挑出壞die,修補die。?FT的難點在于,如何在最短的時間內,保證出廠的Unit能夠完成全部的Function。

小結

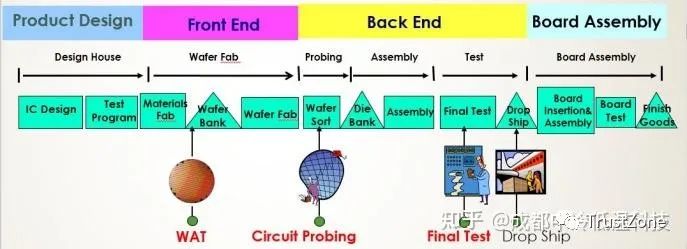

半導體生產流程由

而測試環節主要集中在

?WAT,?CP?FT

三個環節。

圖1 集成電路設計、制造、封裝流程示意圖

WAT

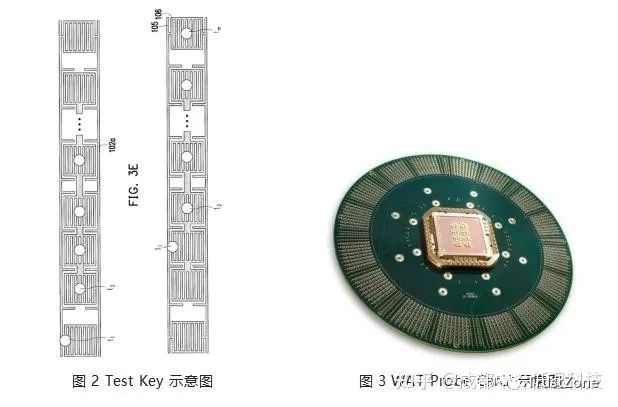

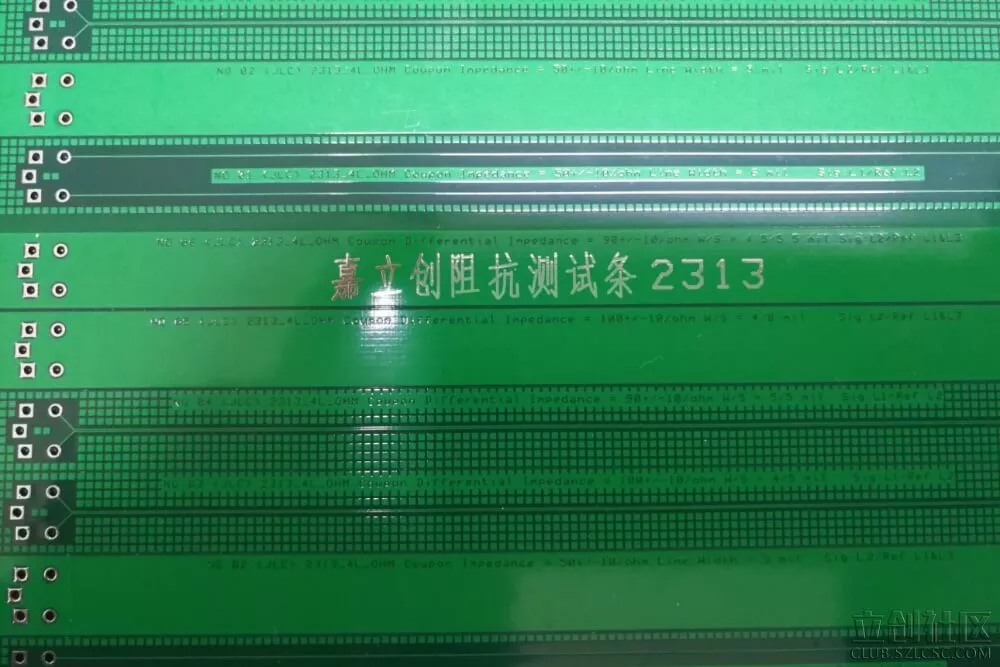

WAT(Wafer Acceptance Test)測試,也叫PCM(Process Control Monitoring),對Wafer 劃片槽(Scribe Line)測試鍵(Test Key)的測試,通過電性參數來監控各步工藝是否正常和穩定.

例如CMOS的電容,電阻, Contact,Metal Line 等,一般在wafer完成制程前,是Wafer從Fab廠出貨到封測廠的依據,測試方法是用Probe Card扎在Test Key的Metal Pad上,Probe Card另一端接在WAT測試機臺上,由WAT Recipe自動控制測試位置和內容,測完某條Test Key后,Probe Card會自動移到下一條Test Key,直到整片Wafer測試完成。

WAT測試有問題,超過SPEC,一般對應Fab各個Module制程工藝或者機臺Shift,例如Litho OVL異常,ETCH CD 偏小,PVD TK偏大等等。WAT有嚴重問題的Wafer會直接報廢。

WAT測試:這是對半導體晶圓(Wafer)的接受測試,用于監控各步工藝是否正常和穩定。它也被稱為PCM(Process Control Monitoring),是一種通過電性參數來檢驗半導體制造過程中工藝控制的方法。

劃片槽(Scribe Line)和測試鍵(Test Key):這是在半導體制造過程中用于WAT測試的兩個關鍵元素。劃片槽是沿著晶圓邊緣的窄條,用于后續的切割(dicing)過程。測試鍵則是設在劃片槽內或者邊緣的特定區域,用于WAT測試。 電性參數:這些參數包括電容、電阻、接觸以及金屬線路等,這些都是在制造過程中需要監控的重要指標。它們反映了半導體器件的電氣特性,如電流傳導能力、電壓承受能力等。

Probe Card:這是一種測試工具,用于連接WAT測試機臺和測試鍵。它的一端與測試鍵的金屬pad接觸,另一端連接到WAT測試機臺。

WAT Recipe:這應該是某種自動控制測試位置和內容的軟件或者程序,它可以根據預先設定的參數來指導Probe Card進行準確的測試。

SPEC:這應該是特定于WAT測試的規格或者標準,超出這個規格或者標準可能意味著半導體制造過程中的某些工藝或者機臺存在問題。

Module制程工藝或者機臺Shift:這是指在半導體制造過程中,如光刻(Litho)、蝕刻(Etch)、薄膜沉積(PVD)等工藝模塊出現問題,或者是機臺的運行狀態發生變化。

Litho OVL異常、ETCH CD 偏小、PVD TK偏大:這些都是對半導體制造過程中可能出現的問題的描述。其中Litho OVL異常可能指的是光刻過程中的光學臨近效應(Optical Proximity Effect)異常;ETCH CD 偏小可能指的是蝕刻后線條寬度小于預期;PVD TK偏大可能指的是薄膜沉積過程中的厚度偏差。

報廢:如果WAT測試出現嚴重問題,比如大量電性參數超出規格,或者連續出現工藝問題,那么整片半導體晶圓會被判定為不合格,進行報廢處理。

IC測試鍵(Test Key)是指用于測試半導體芯片上電路性能和可靠性的特定鍵。這些鍵通常在芯片制造過程中設置,用于在生產線上進行自動化測試。測試鍵的設計和位置取決于芯片的類型和功能。

通過使用測試鍵,可以測試芯片的電性能、功能和可靠性。測試鍵通常會連接到芯片上的電路,以便在測試期間測量電流、電壓和其他電氣參數。此外,測試鍵還可以用于驗證芯片的功能,例如通過施加特定的輸入信號并檢查輸出信號來測試芯片的邏輯功能。

測試鍵對于確保芯片的質量和可靠性非常重要。通過使用測試鍵,可以檢測到制造過程中的缺陷和問題,并及時采取措施進行修復和改進。因此,測試鍵是確保半導體芯片質量和性能的重要工具之一。

CP

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是對整片Wafer的每個Die的基本器件參數進行測試,例如Vt(閾值電壓),Rdson(導通電阻),BVdss(源漏擊穿電壓),Igss(柵源漏電流),Idss(漏源漏電流)等,把壞的Die挑出來,會用墨點(Ink)標記,可以減少封裝和測試的成本,CP pass才會封裝,一般測試機臺的電壓和功率不高,CP是對Wafer的Die進行測試,檢查Fab廠制造的工藝水平。

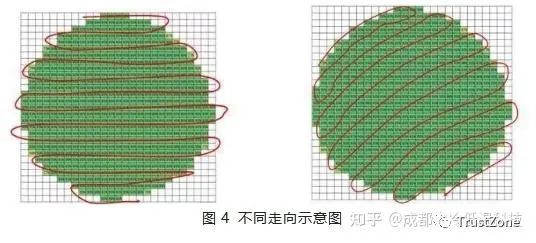

CP測試程序和測試方法優化是Test Engineer努力的方向,下面介紹幾種降低CP測試成本的方法。

?1.同一個Probe Card可以同時測多個Die,如何排列可以減少測試時間?假設Probe Card可以同時測6個Die,那么是2×3排列還是3×2,或者1×6,都會對扎針次數產生影響,不同的走針方向,也會產生Test時間問題。?2.隨著晶圓尺寸越來越大,晶圓上的Die越來越多,很多公司CP Test會采用抽樣檢查(Sampling Test)的方式來減少測試時間,至于如何抽樣,涉及不同的Test Recipe,一些大數據實時監控軟件可以在測試的同時按照一定算法控制走針方向,例如抽測到一個Die失效后,Probe Card會自動圍繞這個Die周圍一圈測試,直到測試沒有問題,再進行下一個Die的抽測,這種方法可以明顯縮短測試時間。

FT

FT(final test)是對封裝好的Chip進行Device應用方面的測試,把壞的chip挑出來,FT pass后還會進行process qual和product qual,FT是對package進行測試,檢查封裝造廠的工藝水平。

FT的良率一般都不錯,但由于FT測試比CP包含更多的項目,也會遇到Low Yield問題,而且這種情況比較復雜,一般很難找到root cause。

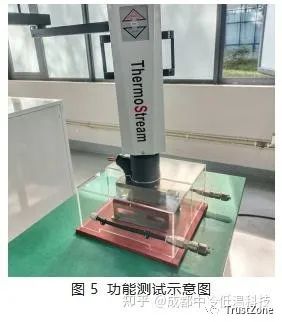

廣義上的FT也稱為ATE(Automatic Test Equipment),一般情況下,ATE通過后可以出貨給客戶,但對于要求比較高的公司或產品,FT測試通過之后,還有SLT(System Level Test)測試,也稱為Bench Test。

SLT

SLT測試比ATE測試更嚴格,一般是功能測試,測試具體模塊的功能是否正常。成都中冷低溫的ThermoStream TS-780高低溫沖擊氣流儀以速度、精度和可靠性作為基本設計標準,提供了非常先進的溫度測試能力。

溫度轉換從-55℃到+125℃之間轉換約10秒,并有更廣泛的溫度范圍-80℃到+225℃; 經長期的多工況驗證,滿足更多生產環境和工程環境的要求。

TS-780應用于提供老化測試、特性分析、高低溫溫變測試、溫度沖擊測試、失效分析等可靠性試驗,用于芯片、微電子器件、集成電路 (SOC、FPGA、PLD、MCU、ADC/DAC、DSP 等) 、閃存 Flash、UFS、eMMC 、PCBs、MCMs、MEMS、IGBT、傳感器、小型模塊組件等電子元器件/模塊冷熱測試。

?WAT是在晶圓制造過程中進行的測試,通過對Die與Die之間Scribe Line Test Key電學性能的測試,來監控Fab制程的穩定性;?CP測試是制造完成后,封測之前進行的電學測試,把壞的Die標記出來,減少封裝的成本;?FT是Die切割,打磨,封裝后進行器件功能性的測試,可以評價封測廠的封裝水平,只有所有的測試都通過后,才可以應用到產品上。

附錄一芯片量產測試常用“黑話”

1、TO

Tape Out,流片,指提交最終GDSII文件給到Foundry進行fab加工。

2、MPW

Multi Project Wafer,多項目晶圓,將多個使用相同工藝的集成芯片放在同一晶圓片上進行流片,制造完成后,每個設計可以得到數十片芯片樣品,多用于出前期工程片。

3、Full Mask

全掩膜,即制造流程中全部掩膜都為某集成芯片設計服務,小批試產及量產階段。

4、Shuttle

MPW時間,每月或每季度固定時間,即“班車”。

5、SEAT

一次MPW的最小面積,可一次選擇多個Seat。

6、Wafer

晶圓,多為8寸、12寸。

7、notch

缺口,用于判別晶圓方向。

8、Yield

良率,CP良率、FT良率、綜合良率。

9、CP

Circuit Probing、Chip Probing,晶圓測試,一般遍歷測試整片Wafer的每個die,確保die滿足DC、AC、功能設計要求。一般有多道CP,如MCU類芯片:CP1、CP2測試Flash,CP3測試定制化功能,CP4高溫測試等。CP測試項理論上較FT測試項多,提前篩除Fail die以節省成本,且一般情況下CP測試扎針pad少,同測Site數多,機時成本較FT低。

10、FT

Final Test,終測、成測,對package后的芯片進行定制化測試,芯片出廠前最后一道關卡。

11、Foundry

晶圓廠,如臺積電(TSMC)。

12、Die

wafer切割后的最小單元,即封裝前的芯片。

13、Chip

芯片,即我們見到的封裝好后的芯片。

14、IP

Intellectual Property Core,非網絡中所說的IP地址、IP協議,而是芯片設計行業中的IP核,即知識產權核,是可重用設計方法學中的可重用模塊,如UART、SPI、IIC等。

15、SOC

System On Chip,片上系統,包含CPU、總線、外設等都在一顆芯片內部實現。

16、MCU

Microcontroller Unit,微控制器單元,概念和SOC類似,但MCU是芯片類型,SOC是設計方式。將CPU、memory、Timer、ADC、DMA等整合在一顆芯片上,形成的微型芯片級計算機。

17、RTL

register-transferlevel,描述同步數字電路的硬件描述語言。

18、Netlist

網表,RTL經過綜合生成。

19、SDC

設計提供約束文件,綜合工具需要SDC才能將RTL轉換成netlist,主要包括:芯片工作頻率,芯片IO時序,設計規則,特殊路徑等。

20、GDS

netlist經過后端工具編程版圖,而版圖提交給foundry的就是GDS II

21、Merge

拼接,將模塊、程序等合并。

22、Margin

邊界,如Margin Test以確定芯片設計上下限值是否滿足需求。

23、OD

針壓,指CP測試階段,Prober扎在wafer pad上的機械壓力值,一般根據工藝、晶圓、測試者經驗、彈坑實驗確定。

24、彈坑

彈坑實驗,CP廠使用不同的針壓力對未扎過針的die進行扎針驗證,在封裝廠進行鋁層腐蝕后,觀測哪組針壓下出現彈坑;將結果反饋CP廠,由其參考實驗結果調整在CP測試時施加針壓大小。彈坑實驗die作報廢處理,在wafer制程及pad鋁層厚度不變情況下,只需進行1次彈坑實驗。

25、TD

Touch down,下針,CP測試中單次扎針。

26、fab

將設計文件交付工廠生產的過程,也代指fab廠。

27、layout

設計。

28、tolerance

容忍度,一般在LB布局布線時提到,如測試項要求有哪些Pin腳的走線線長要一致,阻抗限制等。

29、LB

Load Board,ATE上放置的根據不同芯片定制的母版,用以承載芯片進行批量測試。

30、probe

探針,一般指CP階段給pad扎針的針,在針卡上,針卡需針對wafer定制。

31、prober

放置并傳輸wafer的機器,CP測試時的設備。

32、Site

測試座位,一般指同測數,需根據芯片測試所需資源評估同測數量。

33、Socket

測試座、治具,芯片放置其中,需定制。

34、Kit

FT量產測試時使用,連接Handler和LB,吸取芯片并壓緊進行測試后分bin,需定制。

35、Handler

機械手,安裝Kit后設置操作流程自動進行FT測試。

36、ATE

Automatic Test Equipment,自動化測試設備,專用于芯片量產測試,量產測試工程師吃飯的家伙。

37、板卡

ATE內部搭載的資源,不同板卡不同功能、資源,搭配不同板卡可實現各種測試要求。

38、probe card

針卡,一般根據芯片pad位置定制針卡,分為工程卡和量產卡,對應調試階段和量產階段,插在共板上連接測試機。

39、GU

Golden Unit,金手指,也叫Golden Sample,指經過測試驗證的good chip,可用于環境調試時驗證環境是否正常。

40、pitch

中心距(間距),die pitch、pad pitch。

41、cable

cable連接線,一般一端連接測試機母板,一端連接芯片測試板。

42、IQC

Incoming Quality Control,來料檢驗。

43、bake

烘烤,CP測試中可選步驟。

44、pad

die的pin,pad數量多于pin數。

45、pin

chip的pin。

46、map

一般用在wafer測試中,顯示測試結果pass/fail、分bin等。

47、UV

紫外線照射,封裝時進行,memory芯片除外。

48、自主回收

CP、FT測試中對第一次測試fail die的處理,將對其自動進行重新復測,稱為自主回收。

49、package

封裝,wafer做完CP測試后,會在封裝廠經過磨劃、拋光、切割等工序,形成die,同時將CP測試中暴露出的fail die挑粒,最后對good die進行封裝,進行FT測試。

50、Bin

分類,測試時pass/fail芯片放置或編號作區分,分為HW Bin和SW Bin,Bin號由工程師定義,一般與DC、AC等測試參數相關。

51、Spacing

間距。

-

芯片

+關注

關注

456文章

50954瀏覽量

424773 -

電路

+關注

關注

172文章

5938瀏覽量

172486 -

導通電阻

+關注

關注

0文章

349瀏覽量

19822

原文標題:附錄一芯片量產測試常用“黑話”

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【U盤量產問題】常見U盤量產的七大問題

nRF51822藍牙芯片量產燒錄工具

測試測量產品設計中,如何避免共地干擾?

請問安卓開飯量產測試有專門測試程序嗎?

ZETag云標簽芯片于2021年實現產品量產

VoIP 芯片測試驗證及量產解決方案

CSP封裝量產測試中存在的問題

Achronix完成其基于16nm FinFET+工藝的Speedcore eFPGA技術量產級測試芯片的驗證

附錄一芯片量產測試常用“黑話”

附錄一芯片量產測試常用“黑話”

評論