怎樣通過安排疊層來減少EMI問題?

通過合理安排疊層結構可以顯著減少電磁干擾(EMI)問題。在本文中,我們將詳細探討疊層的概念,以及如何運用正確的材料和設計來最大程度地抑制EMI。

首先,讓我們簡要介紹一下電磁干擾(EMI)的概念。EMI是指電子設備相互之間產生的電磁場干擾,導致設備之間的相互干擾和功能性能的下降。EMI問題可能導致重要的信息丟失、設備故障、性能下降以及對周圍環境安全的影響。

安排疊層是一種常用的方法來減少EMI問題。它通過在電路板上引入一層或多層屏蔽材料來阻止電磁輻射和吸收外部電磁干擾。以下是一些關鍵步驟和注意事項,以確保疊層安排有效地減少EMI問題的詳細解釋。

首先,選擇適當的屏蔽材料非常重要。常見的屏蔽材料包括金屬箔、金屬網格、導電涂層等。金屬箔是最常用的屏蔽材料之一,具有良好的抗干擾性能和導電性能。金屬網格則可以提供更好的透明性和通氣性,但對于高頻干擾的屏蔽效果較差。導電涂層則可以直接應用在電路板上,形成連續的保護層。

其次,疊層結構的設計也是至關重要的一環。要確保疊層結構的效果,需要遵循以下幾個原則。

首先,疊層應該是連續的,沒有中斷。任何中斷都會導致信號泄漏或干擾發生。因此,在設計和制造疊層結構時,必須確保層與層之間的連接是可靠和完整的。

第二,疊層的面積和形狀應該適合需要屏蔽的設備或電路板。層厚度和形狀可能會對屏蔽效果產生影響。例如,對于高頻屏蔽,應選擇較薄的屏蔽材料,以減少信號衰減和反射。此外,對于復雜形狀的電路板,可能需要根據需要對疊層結構進行局部調整和優化。

第三,疊層之間的各層應保持一定的距離。距離的選擇應該考慮到電磁場傳播和反射的特性。通常情況下,疊層之間的距離越大,屏蔽效果越好,但同時也會增加成本和尺寸。

第四,疊層應盡量覆蓋整個電路板或設備,以減少電磁輻射和敏感區域。對于較小的電路板或設備,可能需要精確計算和測量以確定最佳疊層尺寸和位置。

最后,進行電磁兼容性(EMC)測試和測量是確保疊層結構有效的關鍵環節。在制造和裝配過程中,應定期檢查疊層之間的連接和完整性。在整個生產過程中,應使用適當的測試設備和技術來驗證疊層結構的屏蔽性能,以確保其達到設計要求。

綜上所述,通過合理安排疊層結構可以有效減少EMI問題。選擇適當的屏蔽材料,設計合理的疊層結構,確保層與層之間的連續性和距離,以及進行EMC測試和測量,都是關鍵的步驟。良好的疊層設計可以顯著提高電子設備的抗干擾性能,減少不必要的電磁干擾,確保設備的正常運行和安全性能。

-

emi

+關注

關注

53文章

3589瀏覽量

127690 -

電磁干擾

+關注

關注

36文章

2316瀏覽量

105444

發布評論請先 登錄

相關推薦

EMI電磁干擾如何減少

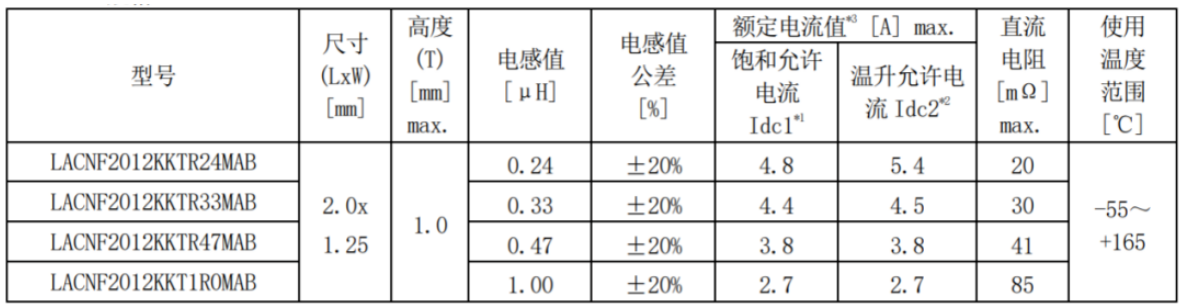

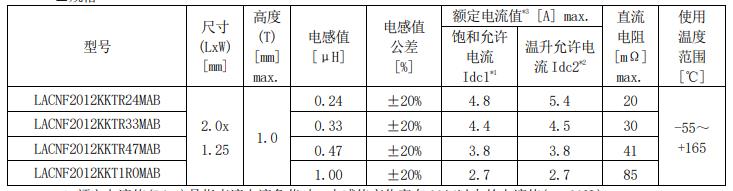

如何根據貼片疊層電感參數進行選型

AMEYA360:太陽誘電應對 165℃的疊層金屬類功率電感器實現商品化!

晶科能源獲批浙江省先進疊層光伏技術重點實驗室認定

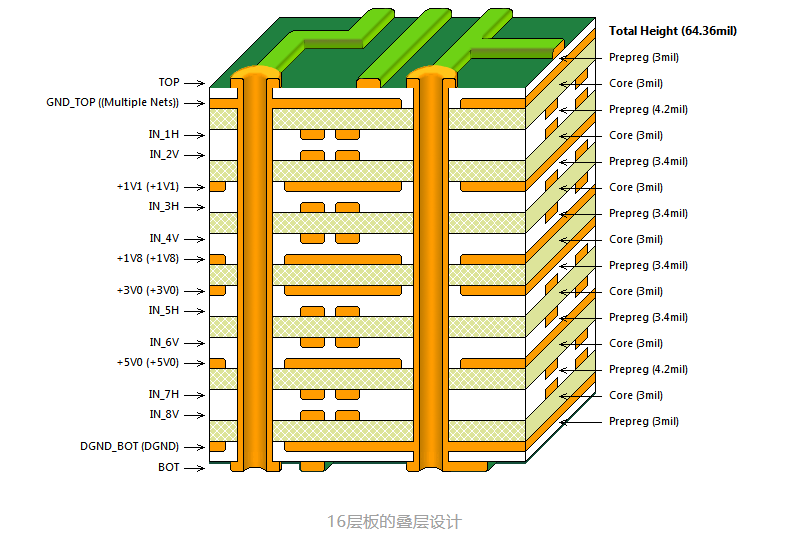

一文讓你了解PCB六層板布局

繞線電感和疊層電感的區別是什么

太陽誘電:應對165℃的疊層金屬類功率電感器實現商品化

晶科能源基于N型TOPCon的鈣鈦礦疊層電池轉化效率再創紀錄

谷景揭秘貼片疊層電感精度是不是越高越好

鈣鈦礦疊層電池:Topcon與HJT底電池性能對比研究

PCB疊層結構與阻抗計算筆記分享

PCB疊層設計優化ESD性能設計

怎樣通過安排疊層來減少EMI問題?

怎樣通過安排疊層來減少EMI問題?

評論