上周微信群里的一個小伙伴提到的一個關于仿真中不達預期的一個問題,其中牽涉到關于仿真中信號競爭等問題。這個問題之前算是不求甚解。這周經一位大佬的提點,結合GPT4的幫助,來好好梳理下這個問題。

由于本人對底層不求甚解,僅做總結與梳理,真實細節還需扒代碼底層,有感興趣的可自行去探索。

不得不說科技改變生活,GPT確實強大。

不達預期的仿真行為

先來看一個簡單的電路:

caseclass Test() extends Component { val pc=outUInt(8bits) setAsReg() init(0) val inst=inUInt(8bits) pc:=pc+1 }

小伙兒的需求很簡單。在仿真中根據當前的pc值加1后反饋給inst輸入引腳。不假思索即可寫出下面的仿真代碼:

object TestApp extendsApp {

SimConfig.withFstWave.compile(bootTest()).doSim{dut=>

dut.clockDomain.forkStimulus(10)

fork{

while(true){

dut.clockDomain.waitSampling()

dut.inst#=dut.pc.toInt+1

}

}

dut.clockDomain.waitSampling(10)

}

}

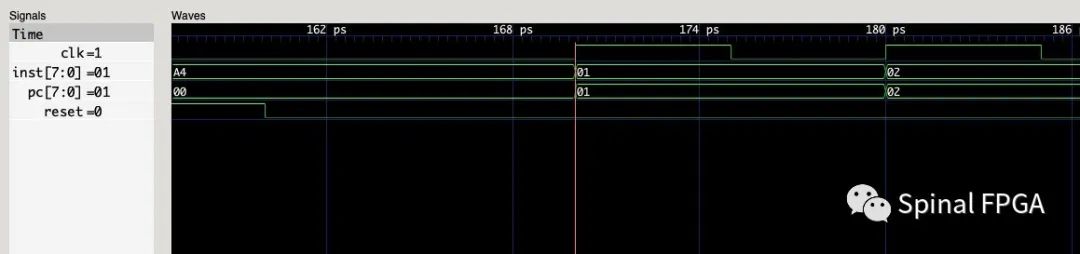

看起來沒啥毛病是吧,時鐘上升沿之后將pc+1驅動給dut.inst。然而仿真結果卻并不如人意:

按照正常的理解,這里面inst的值應該等于pc的值加1才行對吧,然而仿真波形卻顯示inst的值和pc的值一致。仿真器腦抽了?

在執行inst賦值前加上一行打印:

object TestApp extends App {

SimConfig.withFstWave.compile(bootTest()).doSim{dut=>

dut.clockDomain.forkStimulus(10)

fork{

while(true){

dut.clockDomain.waitSampling()

println(s"time:${simTime()} pc:${dut.pc.toInt} isnt_in:${dut.inst.toInt} clk:${dut.clockDomain.clockSim.toBoolean}")

dut.inst#=dut.pc.toInt+1

}

}

dut.clockDomain.waitSampling(10)

}

}

仿真執行時打印信息如下:

time:170pc:0isnt_in:64clk:true time:180pc:1isnt_in:1clk:true time:190pc:2isnt_in:2clk:true time:200pc:3isnt_in:3clk:true time:210pc:4isnt_in:4clk:true time:220pc:5isnt_in:5clk:true time:230pc:6isnt_in:6clk:true time:240pc:7isnt_in:7clk:true time:250pc:8isnt_in:8clk:true

這就有點意思了,在170時刻,明明clk已經是高電平,按道理來時鐘上升沿已然產生,然而pc打印出來的值仍然是0!

先說這里如何修復這個問題,你只需添加一個sleep(0):

object TestApp extends App {

SimConfig.withFstWave.compile(bootTest()).doSim{dut=>

dut.clockDomain.forkStimulus(10)

fork{

while(true){

dut.clockDomain.waitSampling()

sleep(0)

println(s"time:${simTime()} pc:${dut.pc.toInt} isnt_in:${dut.inst.toInt} clk:${dut.clockDomain.clockSim.toBoolean}")

dut.inst#=dut.pc.toInt+1

}

}

dut.clockDomain.waitSampling(10)

}

}

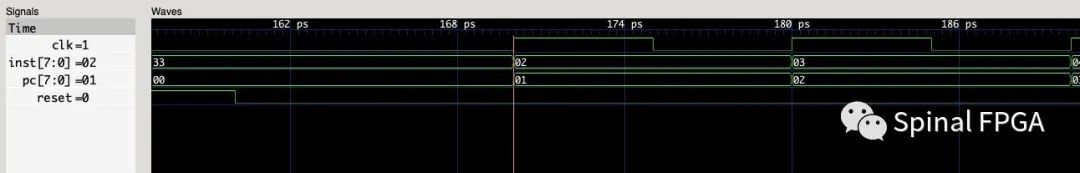

如此,即可符合仿真預期:

Log打印:

time:170pc:1isnt_in:51clk:true time:180pc:2isnt_in:2clk:true time:190pc:3isnt_in:3clk:true time:200pc:4isnt_in:4clk:true time:210pc:5isnt_in:5clk:true time:220pc:6isnt_in:6clk:true time:230pc:7isnt_in:7clk:true time:240pc:8isnt_in:8clk:true time:250pc:9isnt_in:9clk:true

如果覺得能用即可,那么針對這種問題看到這里就可以了~

審核編輯:劉清

-

高電平

+關注

關注

6文章

152瀏覽量

21460 -

CLK

+關注

關注

0文章

127瀏覽量

17196 -

GPT

+關注

關注

0文章

355瀏覽量

15454

原文標題:借助GPT4好好理解下仿真中競爭的處理

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電子元器件在電路仿真中如何建模

saber仿真中的問題處理方法

淺談ChatGPT的最新“升級版本”——GPT4模型

GPT4做Leetcode的能力

你考慮用GPT4搞電機嗎?

gpt-4怎么用 英特爾Gaudi2加速卡GPT-4詳細參數

chatGPT和GPT4有什么區別

ChatGPT Plus怎么支付 GPT4得訂閱嗎?

MATLAB電路仿真中能講電流匯總的元件

股價久違飆漲,商湯要用自己的Scaling law挑戰GPT4

借助GPT4理解仿真中競爭處理的方法

借助GPT4理解仿真中競爭處理的方法

評論