導(dǎo)讀:在基于FPGA的網(wǎng)絡(luò)設(shè)備中,精確的時間同步至關(guān)重要。IEEE 1588標(biāo)準定義的精確時間協(xié)議(PTP)為網(wǎng)絡(luò)中的設(shè)備提供了納秒級的時間同步。本文將介紹虹科提供的適用于基于FPGA的網(wǎng)絡(luò)設(shè)備的IEEE 1588透明時鐘(TC)架構(gòu),幫助您實現(xiàn)精確時間同步和高效通信。

在分布式系統(tǒng)中,傳感器/執(zhí)行器的事件和操作需要進行精確的時間協(xié)調(diào),因為時鐘差異可能導(dǎo)致操作失敗。為了確保時間同步,每個組件都需要具備與其對等組件一致的實時時鐘,這需要時間同步的常識。

隨著電信網(wǎng)絡(luò)從傳統(tǒng)的時分復(fù)用 (TDM)發(fā)展到基于分組的網(wǎng)絡(luò),額外的同步協(xié)議已成為必要。因此,近幾十年來開發(fā)了多種同步技術(shù),如 IRIG-B、LORAN-C、NTP、基于GPS的同步和SyncE。然而,它們不適合需要精確時間且成本較低的應(yīng)用領(lǐng)域。

通過精確時間協(xié)議 (PTP),能夠以最少的網(wǎng)絡(luò)、計算和硬件資源需求達到亞微秒精度。鑒于此,IEEE 1588標(biāo)準中定義的PTP正在成為許多需要精確時間同步的應(yīng)用的最可行的解決方案。虹科推出用于可重新配置設(shè)備的IEEE 1588透明時鐘 (TC)可擴展架構(gòu),該邏輯解決了PTP實現(xiàn)的主要缺點之一,即級聯(lián)拓撲中的錯誤累積。

一、PTP操作過程

1、PTP操作類型

PTP操作可分為兩個過程:時間同步和頻率同步

時間同步(或偏移調(diào)整):偏移量計算為主從時間之差

頻率同步(或頻率調(diào)整):頻率漂移為在兩個N間隔的同步消息之間傳遞的從機時間差和主機時間差之間的比率。

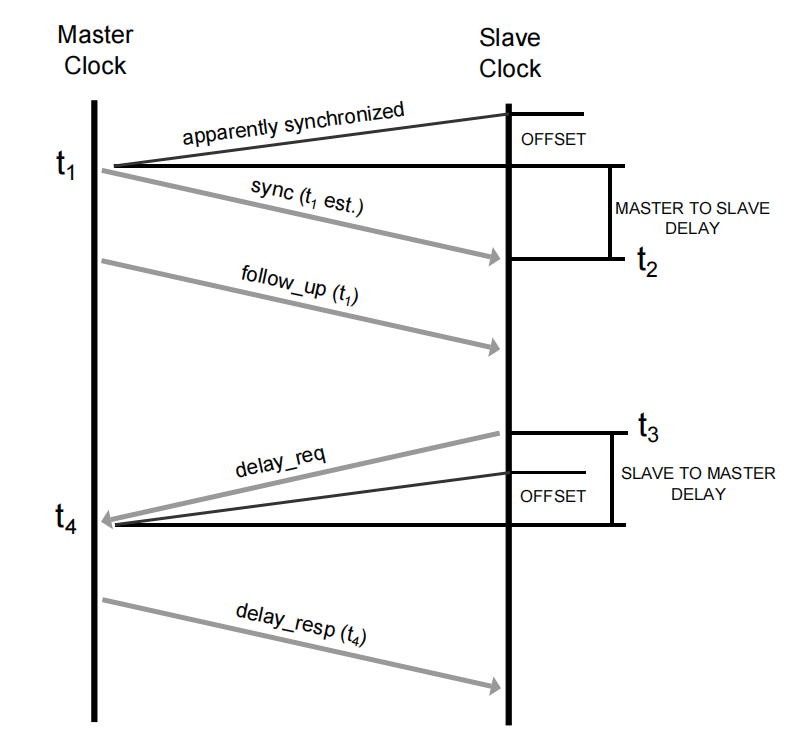

圖1.延遲請求響應(yīng)機制

2、延遲測量

PTP消息中發(fā)送的時間戳必須通過傳播延遲進行糾正,傳播延遲可以使用標(biāo)準中定義的兩種機制之一進行測量:延遲請求響應(yīng)機制或?qū)Φ妊舆t機制。

3、PTP時鐘設(shè)備

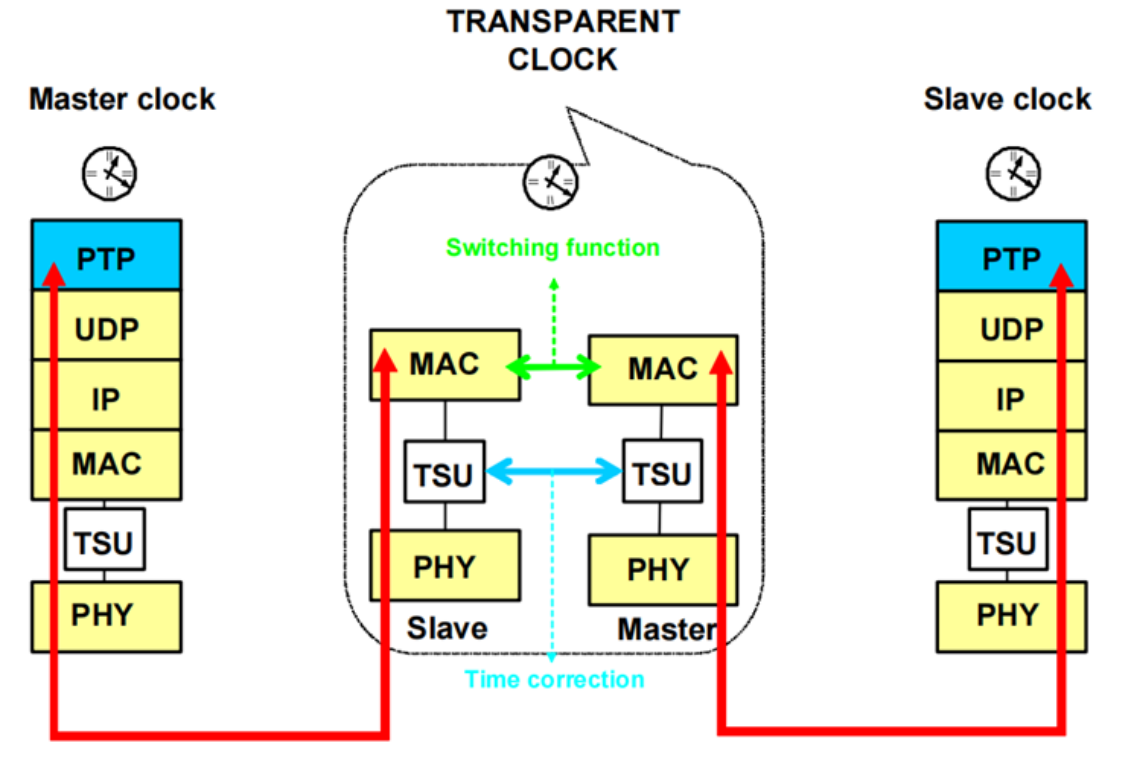

PTP系統(tǒng)由PTP和非PTP設(shè)備的組合組成。PTP設(shè)備分為普通時鐘(OC)、邊界時鐘(BC)、透明時鐘(TC)和管理節(jié)點(MN)。

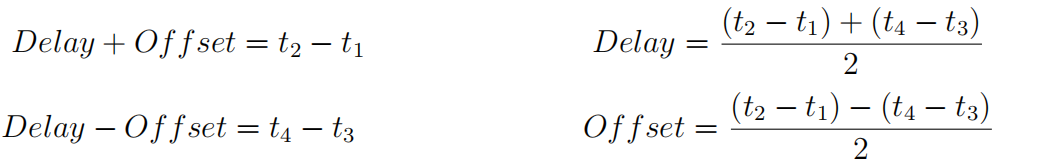

圖2. PTP網(wǎng)絡(luò)示意圖

圖2展示了一個簡單PTP網(wǎng)絡(luò):OC是包含PTP時鐘和單個物理網(wǎng)絡(luò)連接的系統(tǒng)終端設(shè)備,而BC是具有多個物理端口的網(wǎng)絡(luò)設(shè)備,它們不轉(zhuǎn)發(fā)PTP接收到的消息,而是與主站同步并生成新的PTP消息以與其余從站共享其自己的定時參考。TC有兩種類型:端到端(E2E)TC和點對點(P2P)TC,它們也是網(wǎng)絡(luò)設(shè)備。

一方面,E2E TC像正常網(wǎng)絡(luò)節(jié)點一樣轉(zhuǎn)發(fā)所有PTP和非PTP消息,此外,它們測量消息穿越TC所需的時間,稱為駐留時間,并將其累積在PTP中稱為 CorrectionField的特殊字段。另一方面,P2P TC使用對等延遲機制來測量兩個直接連接的端口(鏈路對等點)之間的鏈路延遲,并使用與Sync消息的入口傳輸路徑相關(guān)的駐留時間和鏈路延遲來更新CorrectionField,允許在網(wǎng)絡(luò)拓撲更改后更快地重新配置。

此外,每個PTP設(shè)備可以作為一步或兩步模式工作:一步時鐘根據(jù)同步和延遲請求事件消息實時生成時間戳,而兩步時鐘則根據(jù)Follow Up和Delay Resp一般消息。

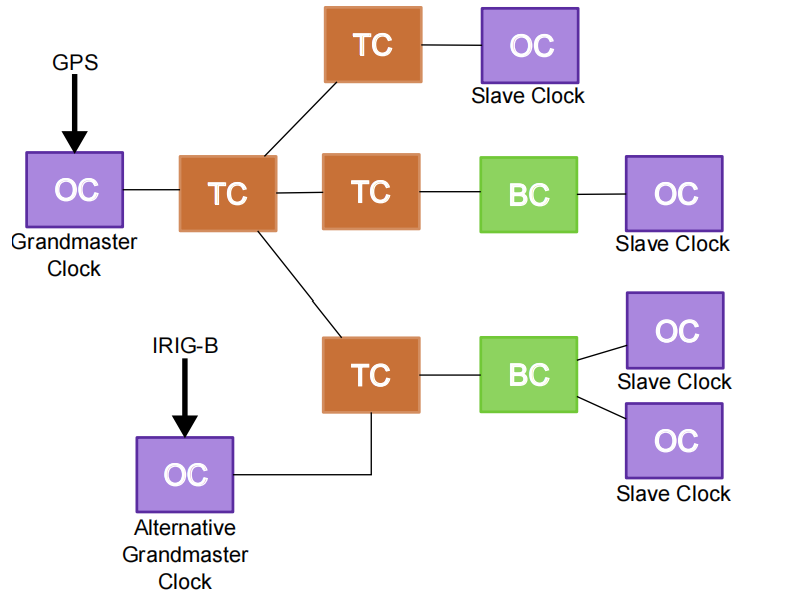

4、PTP執(zhí)行

硬件與軟件實現(xiàn):PTP環(huán)境提供不同的可能時間戳點,如圖3所示。結(jié)果的精度取決于時間戳的精度 。一方面,在網(wǎng)絡(luò)接口卡 (NIC)驅(qū)動程序或應(yīng)用程序?qū)又蝎@取時間戳的純軟件解決方案具有平臺獨立性的優(yōu)勢,但會經(jīng)歷通過協(xié)議棧的消息傳輸延遲的巨大變化(也稱為抖動)。驅(qū)動程序級別的時間戳是最佳軟件解決方案,但需要修改網(wǎng)絡(luò)驅(qū)動程序。

圖3.可能的時間戳點

另一方面,在硬件輔助方法中,時間戳是在介質(zhì)獨立接口(MII)處獲取的。帶有時間戳的消息越接近物理層,所達到的準確性就越好。由于硬件的幫助,使用IP內(nèi)核和現(xiàn)場可編程門陣列 (FPGA)已成為最精確和準確的時間戳方法。

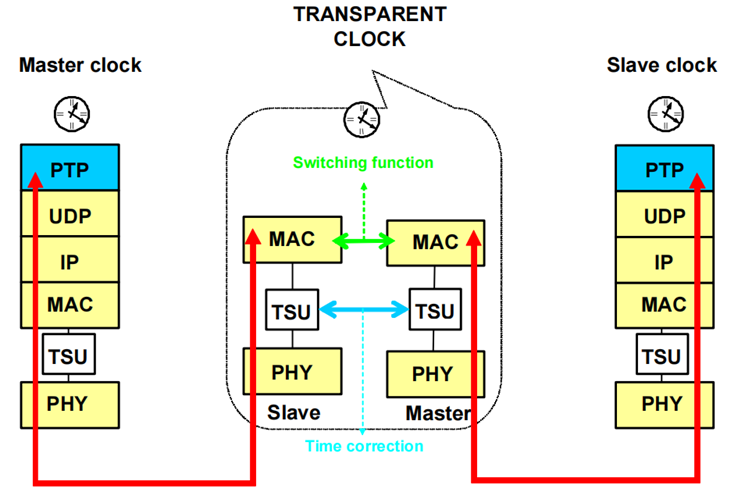

其他實現(xiàn)方面:不同供應(yīng)商的PTP IP核往往具有相似的架構(gòu)。他們通常使用軟CPU,例如Xilinx FPGA中的Microblaze,包含用戶應(yīng)用程序和PTP堆棧軟件,并在同一FPGA中構(gòu)建完整的SoC解決方案。這些IP核通常由至少兩個稱為實時時鐘 (RTC)和時間戳單元 (TSU)的硬件模塊組成。RTC通常是一個64位計數(shù)器,表示秒和納秒,并且可以通過更改內(nèi)核的某些配置寄存器的值進行調(diào)整。TSU負責(zé)存儲有關(guān)幀的信息,例如序列 ID、消息類型或時鐘標(biāo)識,以及時間戳信息。

二、基于FPGA的TC架構(gòu)

1、實時時鐘(RTC)

名為RTC的塊代表可選的同步時鐘源,例如,它可以是 IEEE 1588或GPS時鐘。RTC可以由一個計數(shù)器形成,該計數(shù)器在每個時鐘周期按系統(tǒng)時鐘周期遞增。

2、循環(huán)冗余校驗 (CRC)檢查器/發(fā)生器

CRC檢查器模塊檢查接收到的以太網(wǎng)幀的幀校驗序列(FCS)字段,以便檢測傳輸過程中損壞的數(shù)據(jù)(由 于數(shù)據(jù)丟失或更改而導(dǎo)致的錯誤)。另一方面,CRC生成器模塊重新生成新的FCS字段并將其附加在幀末尾,如IEEE 802.3標(biāo)準中所定義。

3、On-The-Fly (OTF)更正

OTF Correction的模塊負責(zé)將相應(yīng)的駐留時間動態(tài)添加到PTPv2事件數(shù)據(jù)包的CorrectionField字段中,如IEEE 1588-2008中針對單步TC的定義。也就是說,它不會等到接收到整個PTP消息才計算停留時間并將其添加到CorrectionField中。相反,一旦知道傳入消息的CorrectionField,就會盡快將停留時間添加到其中。

4、駐留時間橋

該模塊計算自PTP幀進入和離開TC以來經(jīng)過的時間。每個消息的停留時間值被向下傳遞到OTF校正模塊。由于入口時間戳臨時存儲在存儲器中,并且計算的停留時間被傳遞到負責(zé)更新CorrectionField的模塊。

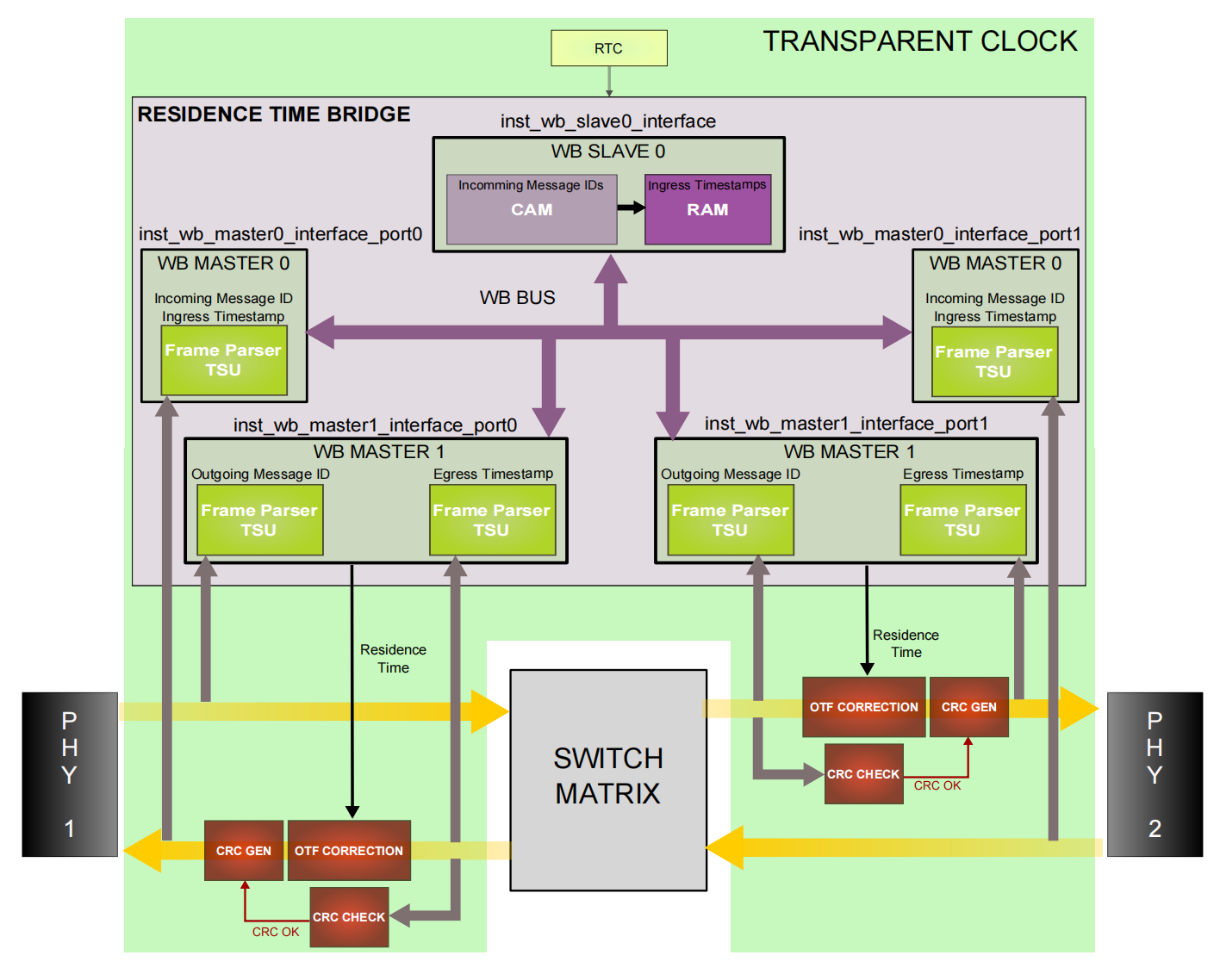

圖4.駐留時間橋框圖

5、實驗結(jié)果

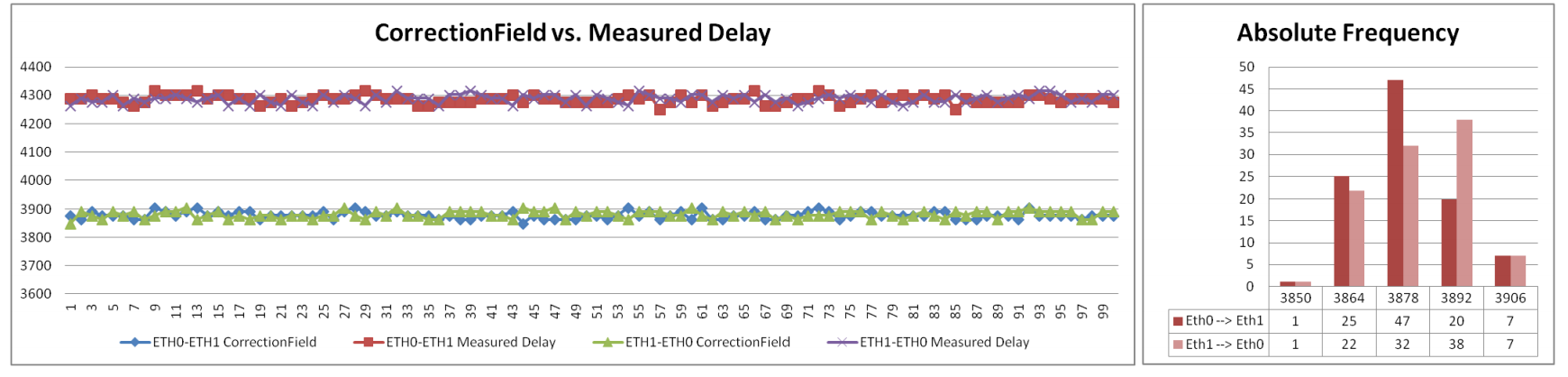

圖5.左側(cè)為CorrectionField和測量延遲樣本之間的比較;右側(cè)為停留時間出現(xiàn)的頻率

通過復(fù)制必要的模塊,該設(shè)計可以輕松擴展到兩個以上的端口:除了新的OTF校正器之外,每個新端口還應(yīng)將兩個額外的WB Master 0和WB Master 1子模塊集成到駐留時間橋中,CRC檢查器和CRC生成器連接到每個新的出口端口。在資源利用方面,每個額外端口的空間需求比較少數(shù)的Slices Registers和LUTs。不需要復(fù)制WB Slave 0,但必須調(diào)整CAM/RAM存儲器的大小以應(yīng)對PTP流量并在擁塞條件下正確執(zhí)行。

三、虹科IEEE1588IP核方案

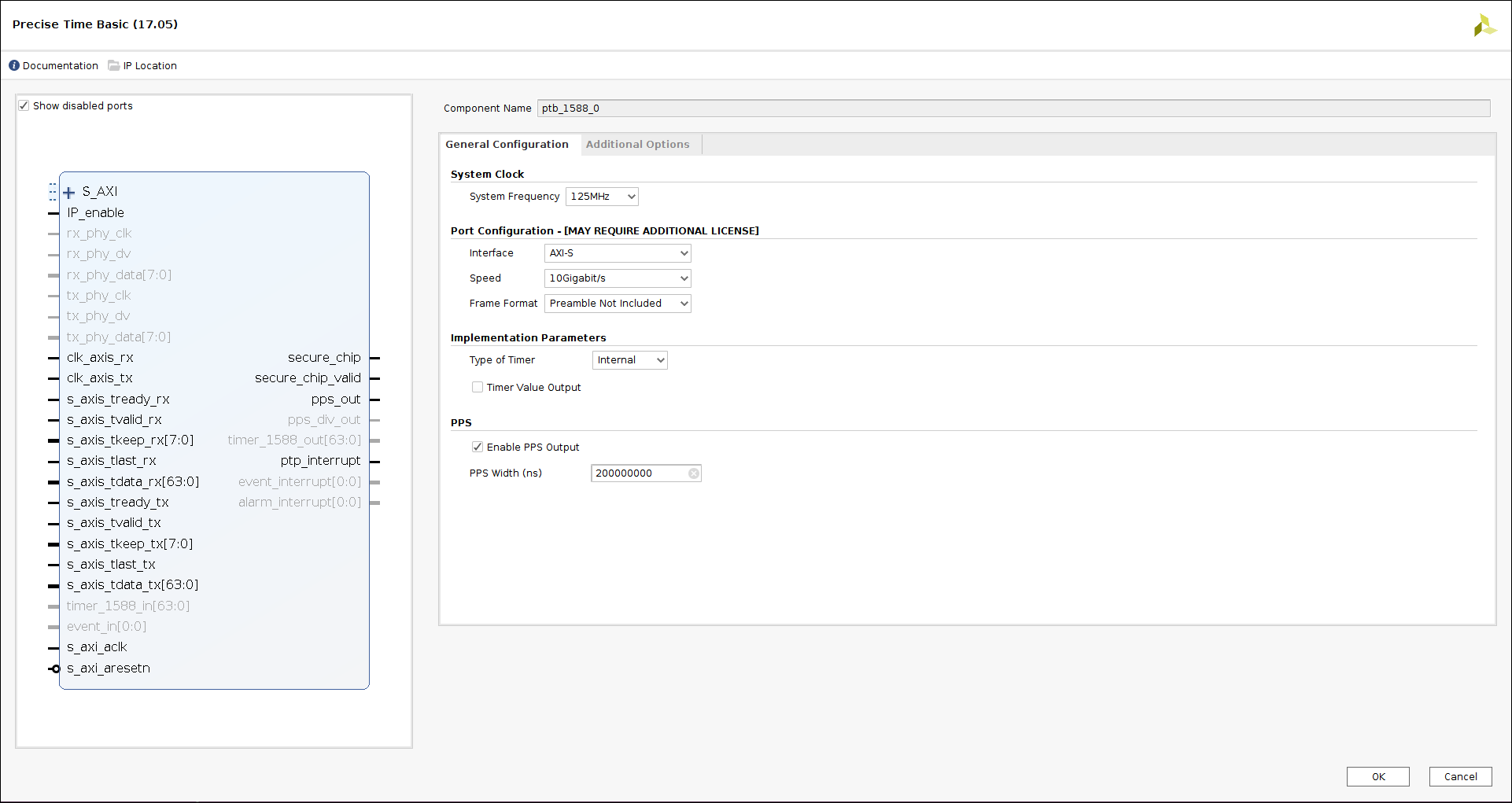

虹科IEEE1588v2兼容時鐘同步IP內(nèi)核,它能夠準確地為IEEE1588報文打上時間戳,并提供兼容的計時器,廣泛應(yīng)用于汽車、工業(yè)、廣播和航空航天等行業(yè)。其能夠提供許多應(yīng)用所需的精確時間同步,而不需要任何新的基礎(chǔ)設(shè)施。

TC應(yīng)在級聯(lián)拓撲中使用,其中網(wǎng)絡(luò)設(shè)備擁塞狀況導(dǎo)致的延遲可能會影響協(xié)議性能。所提出的TC架構(gòu)是以簡單的方式開發(fā)具有TC功能的以太網(wǎng)交換機的可行解決方案,具有完全的可擴展性和最小的資源利用率。由于塊RAM是利用率最高的資源,并且它們直接取決于CAM和RAM大小,因此應(yīng)在實現(xiàn)過程中優(yōu)化這兩個元素。如需進一步了解虹科IEEE1588PTPIP核解決方案,歡迎隨時聯(lián)系我們。

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1638文章

21860瀏覽量

609874 -

IEEE

+關(guān)注

關(guān)注

7文章

388瀏覽量

47633 -

時鐘

+關(guān)注

關(guān)注

11文章

1765瀏覽量

132377 -

PTP

+關(guān)注

關(guān)注

0文章

67瀏覽量

8801

發(fā)布評論請先 登錄

相關(guān)推薦

IEEE1588的原理

FPGA項目開發(fā)之初始時鐘架構(gòu)和相關(guān)的復(fù)位架構(gòu)繪制

P2P透明時鐘駐留時間誤差測試方法

新UltraScale ASIC時鐘架構(gòu)的使用及好處

虹科干貨 | TSN標(biāo)準——IEEE802.1AS-2020和IEEE802.1AS-2011有哪些不同?

【虹科】5分鐘弄懂IEEE 1588時鐘類型

【虹科】5分鐘弄懂為什么IEEE 1588如此精確?

虹科干貨 | 如何測試與驗證復(fù)雜的FPGA設(shè)計(3)——硬件測試

【虹科】5分鐘弄懂為什么IEEE 1588如此精確?

適用于基于FPGA的網(wǎng)絡(luò)設(shè)備的IEEE 1588透明時鐘架構(gòu)

PTP時鐘源設(shè)備全攻略:從普通時鐘到透明時鐘的進階之路

虹科技術(shù)丨PTP時鐘源設(shè)備全攻略:從普通時鐘到透明時鐘的進階之路

虹科技術(shù)|PTP時鐘源設(shè)備全攻略:從普通時鐘到透明時鐘的進階之路

評論