AMD自適應計算加速平臺(ACAP)是一個完全軟件可編程資源集合,這些資源結合在一起構成片上系統(tǒng) (SoC),包括以下主要的資源塊:

AI 引擎(AI 引擎可用性與器件相關)

可編程邏輯(PL)

片上網絡(NoC)

高速 I/O(XPIO)

處理器系統(tǒng)(PS)

平臺管理控制器(PMC)

IntegratedBlock for PCIe ,含 DMA 和高速緩存一致性互連(CPM)(CPM 可用性與器件相關)

收發(fā)器 (GT)

高速連接和加密集成 IP

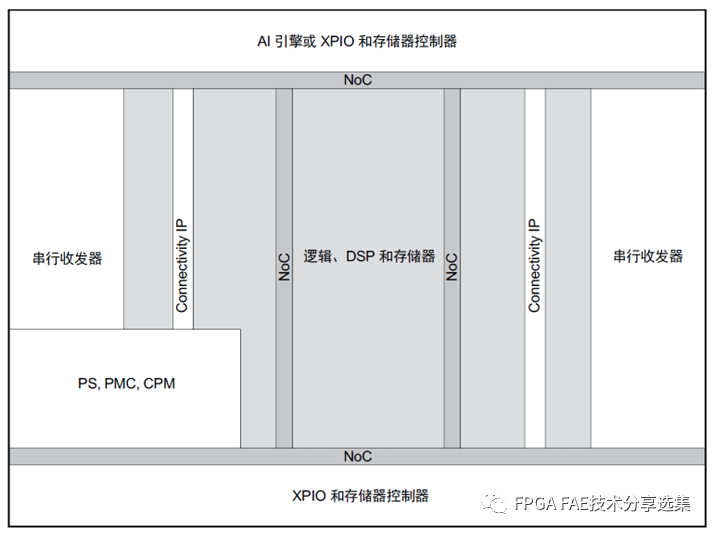

Versal ACAP 應用可以利用這些資源中的功能。要創(chuàng)建設計或將設計移植到 Versal ACAP,必須確定哪些資源最能滿足應用的不同需求,并跨資源對應用進行分區(qū)。下圖顯示了 Versal ACAP 的布局。

圖1 Versal 器件布局

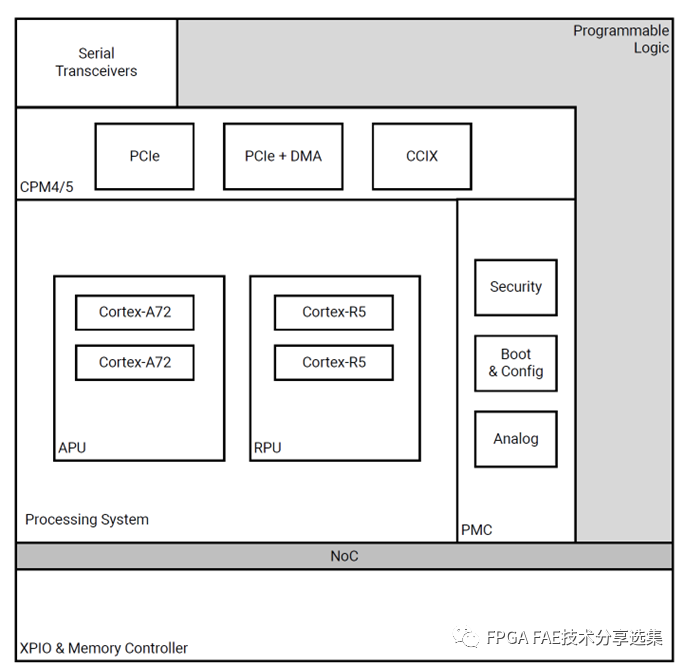

所有器件都包含一個由標量引擎(APU和RPU)和外設組成的處理系統(tǒng)(PS)。PS是包括平臺管理在內的一組體系結構元素的一部分控制器、CPM塊、NoC和集成內存控制器是緊耦合的,但也是能夠彼此獨立操作。簡化的布局如下圖所示。

圖2 PS和周圍的功能塊

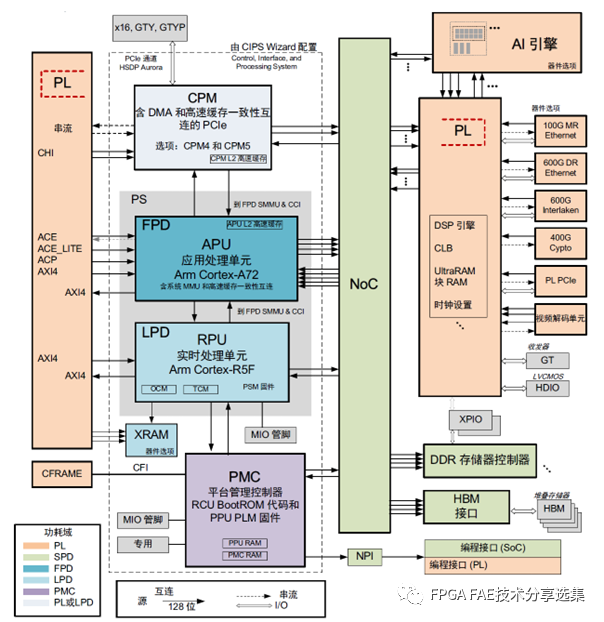

主要功能模塊互連

如下圖所示,PS 模塊、PMC 模塊與 CPM 模塊組合在一起,并使用 Control, Interface, and Processing System (CIPS) IP核進行配置。

圖3 器件級互連架構

CIPS IP 核支持您完成以下配置:

1、配置 PMC、PS、NoC 和(可選)PL 的器件時鐘設置

2、配置 PMC 閃存控制器、外設及其關聯的多路復用 I/O (MIO)

3、配置 PS 外設及其關聯的 I/O

4、配置 PS-PL 中斷和交叉觸發(fā)

5、配置 CPM(含 DMA 和高速緩存一致性互連的 Integrated Block for PCIe)

6、配置連接至 NoC 和 PL 的 PS 和 CPM AXI 接口

7、配置系統(tǒng)監(jiān)控器供電和溫度監(jiān)控和警報

8、配置 HSDP 用于高速調試

CIPS相關IP核定制和作用解析

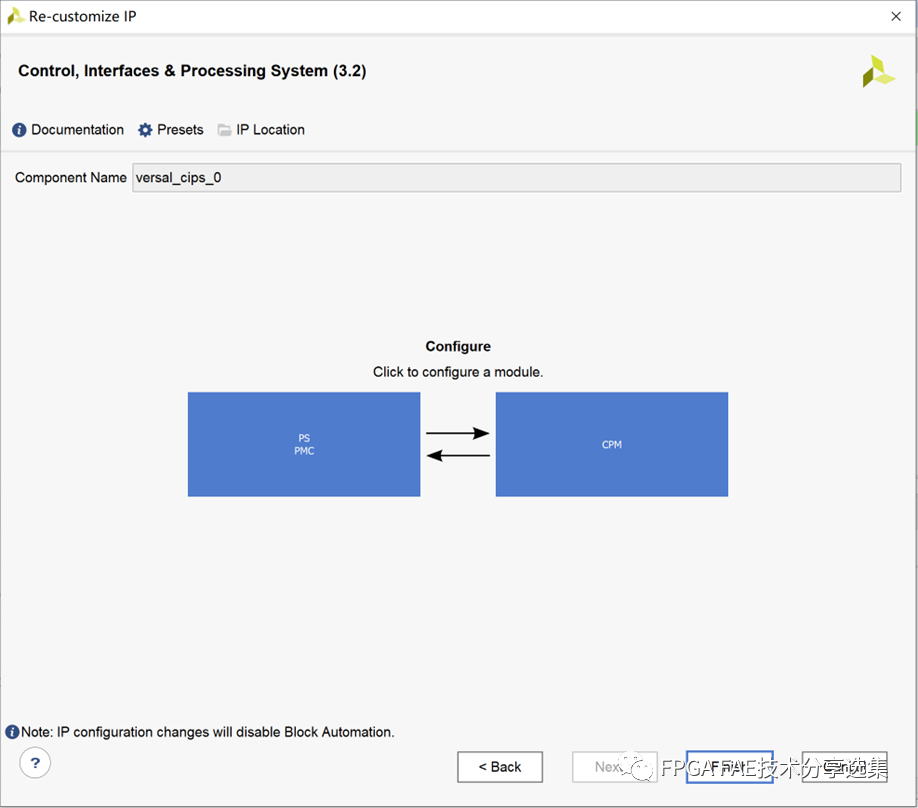

Versal ACAP 支持 2 種設計流程:傳統(tǒng)設計流程和基于平臺的設計流程。但所有 Versal 器件設計必須包含 CIPS IP。平臺管理控制器 (PMC) 整合到 CIPS IP 中,必須對其加以配置才能使 Versal 器件正確啟動。

1、CIPS IP核心模塊設計

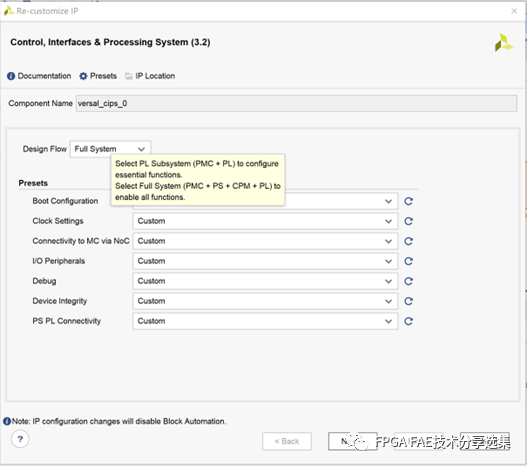

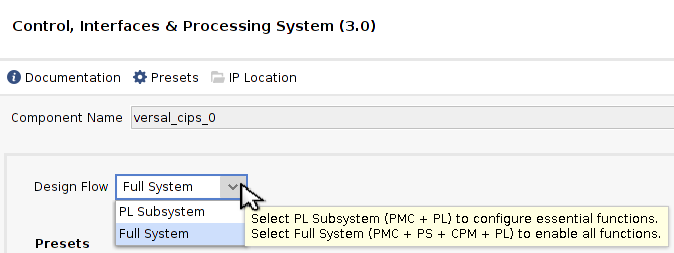

單擊CIPS IP,可以自定義控制接口和處理系統(tǒng)IP核。選擇定制的框圖如下圖所示。

???

???

圖4 CIPS IP 核模塊設計

a、選擇設計流程

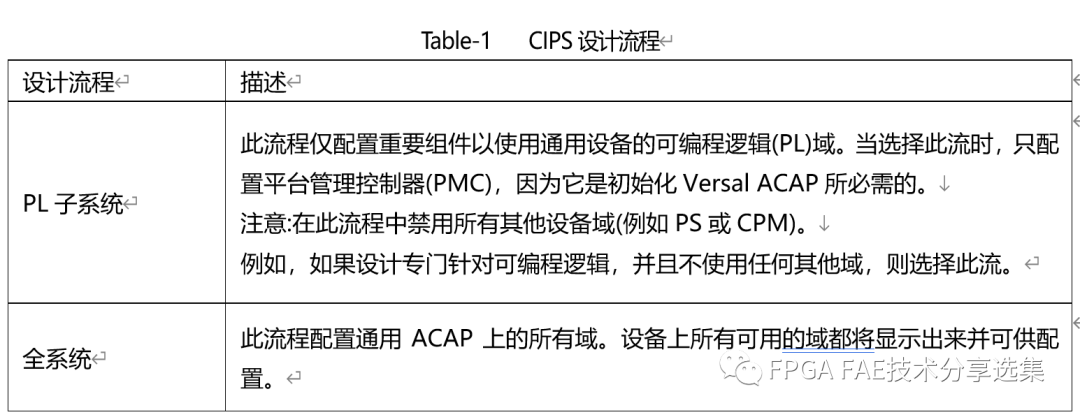

CIPS非常靈活,可以用幾種不同的方式進行配置。CIPS IP允許配置許多操作參數。有兩個設計流程可用于配置這些參數。這兩個流程基于兩個用戶的傳統(tǒng)典型應用,如下表所示。

CIPS IP為設計人員提供塊/板卡自動化等輔助。塊自動化提供初始配置并連接到其他相關IP塊。當選擇單板部件并設置預置時,Board Automation會對CIPS IP應用特定的配置預置,以配合目標板卡。此外,其他IP可以為連接到CIPS IP的附加外設/連接提供連接自動化。塊自動化不可重入。除非將IP從IP集成器中刪除并再次添加,否則它不能被再次調用。

b、塊自動化

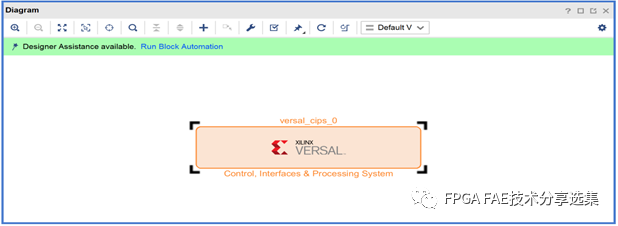

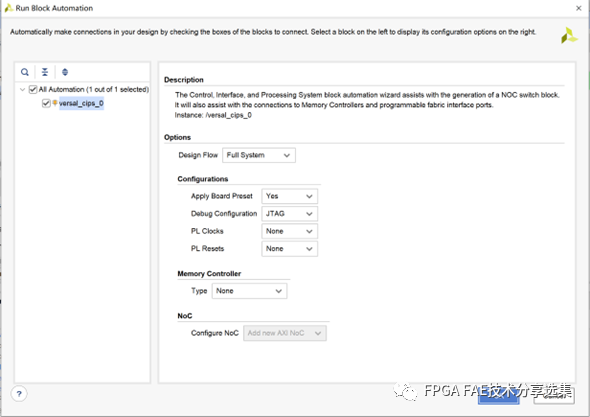

Vivado支持CIPSIP的塊自動化以幫助將其集成到更大的設計中。將CIPS IP添加到框圖后將彈出塊自動化橫幅,如下圖5所示。單擊Run Block Automation打開塊自動化頁面。

有兩種設計流程可供選擇,選擇的流程將反映在CIPS IP中。建議利用塊自動化來配置DDR內存控制器,因為它可以確保CIPS和NoC IP的專用接口之間的適當連接。

圖5 塊自動化

圖6 運行塊自動化

c、板卡自動化

創(chuàng)建針對單板而不是特定器件的Vivado項目時,可以使用單板預設來初始化具有單板特定設置的CIPS IP核。在塊設計中實例化CIPS IP后,將出現一個綠色橫幅,要訪問板自動化,請單擊此橫幅上的運行塊自動化。

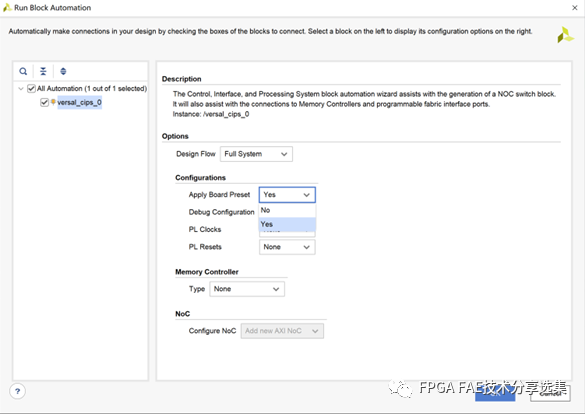

如果要設置單板預置,請在“運行塊自動化”窗口中將“應用單板預置”設置為“是”。

圖7 應用塊自動化實現板自動化

d、CIPS預置

CIPS是通過CIPS參數的默認配置(稱為Presets)啟用的。預置方便設計創(chuàng)建和塊自動化,并使用戶能夠通過GUI快速配置IP,而無需深入參數細節(jié)。根據所選擇的設計流程,可以使用不同的預設。默認預設表示最簡單和必要的設置選項。這些選項基于傳統(tǒng)的、大多數遇到的用例,以及設備最小的啟動和運行時需求。

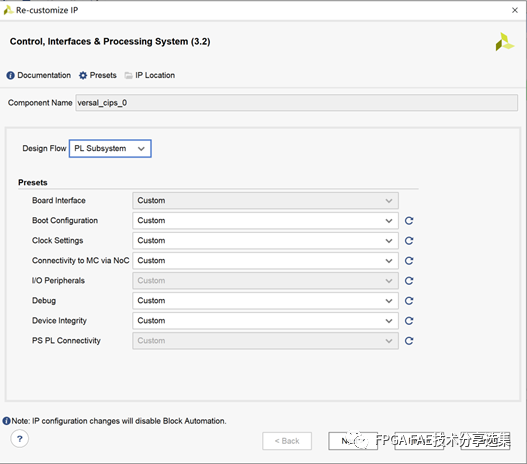

有兩個可用的設計流程,即PL子系統(tǒng)和整個系統(tǒng)。在選擇設計流的基礎上,將默認的預置配置啟用到所選參數中。下圖所示為CIPS IP核全系統(tǒng)與PL子系統(tǒng)預置。

圖8 CIPS 預置

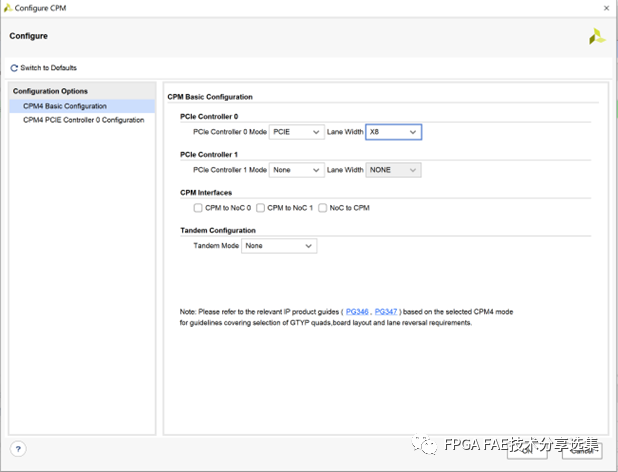

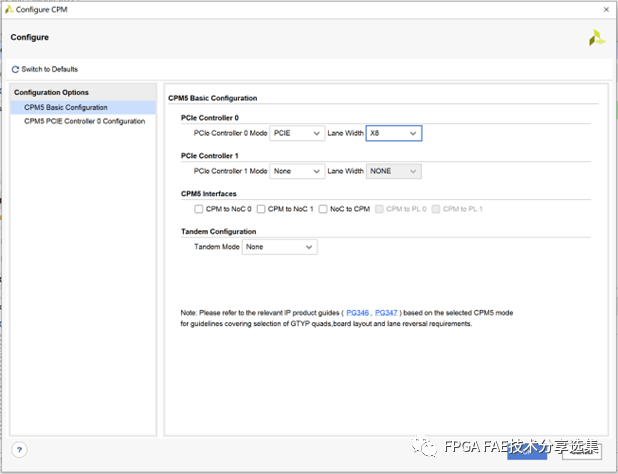

2、CPM模塊

Versal 架構包括多個塊,用于實現基于 PCITM-SIG 技術的高性能標準接口。在包含 CPM 的 Versal ACAP 中,CPM 遵循服務器系統(tǒng)方法論來為設計提供主要接口。作為 Versal 架構集成 shell 的一部分,CPM 與 NoC 之間存在專用連接,通過該連接可以訪問 DDR 和其他硬化 IP。CPM 與可編程邏輯分開配置,使集成 shell 在啟動后即可快速運行,而無需配置 PL。這種單獨配置方法解決了 PCIe 規(guī)范帶來的常見上電和復位時序問題。CPM 有 2 種實現方式:CPM4 和CPM5。

不同系列的 Versal 的器件可支持的 PCIE 最高速率不同,能夠支持PCIE5.0協議的產品,例如 VPK120,其 CIPS 內使用的是CPM5,而只能支持到 PCIE 4.0 協議的產品,例如VCK190,其 CIPS 內使用的是 CPM4,某些器件不提供CPM。

目前,只有Full System (PS + PMC + CPM + PL)流程支持CPM塊中的PCIe配置。

圖9 CPM4基本配置

??????

??????

圖10 CPM5基本配置

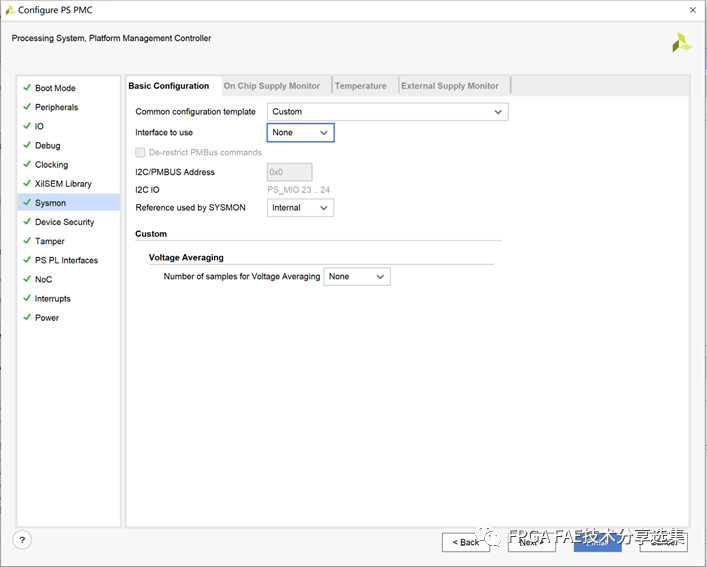

3、系統(tǒng)監(jiān)控器

系統(tǒng)監(jiān)測器(SYSMON)既可在VersalACAP本身內監(jiān)測物理環(huán)境,也可在使用外部輸入的更廣泛的系統(tǒng)內監(jiān)測物理環(huán)境。它是用來確保通用ACAP和整個系統(tǒng)以安全、穩(wěn)妥、可靠的方式運行的。SYSMON為客戶提供溫度和應用電壓供應的數字測量,以及在更廣泛的系統(tǒng)范圍內的片外電壓測量。

CIPS IP核可以實現以下措施:

1、芯片供電監(jiān)控

2、溫度測量

3、外部供應測量

基本配置選項卡具有默認和自定義選項,如下圖所示。

????

????

圖11 SYSMON基本配置

默認窗口具有不同的預設選項,為SYSMON使用提供了一個典型用法。每個測量都有相關的閾值水平,控制報警斷言。報警默認啟用。對于對SYSMON測量的外部訪問,支持I2C和PMBus接口。為確保不誤觸發(fā)SYSMON告警,請檢查預置告警值,確保當前選擇的值符合所需用例。

默認窗口還提供了設置電壓平均水平為2、4、8和16的選項。MIO引腳分配可以通過IO面板進行修改。任何MIO沖突都以圖標突出顯示。

“片上電源監(jiān)視器”選項支持不同類型的電壓測量,包括客戶電源電壓和客戶專用焊盤電壓。

“溫度配置”選項配置設備溫度監(jiān)控選項,包括過溫關機。

CIPS IP 核心允許最多選擇 16 個引腳進行外部電源測量。所有 AUXIO 均應分配到同一Bank。AUXIO支持 PMC MIO、LPD MIO 和 HDIO。

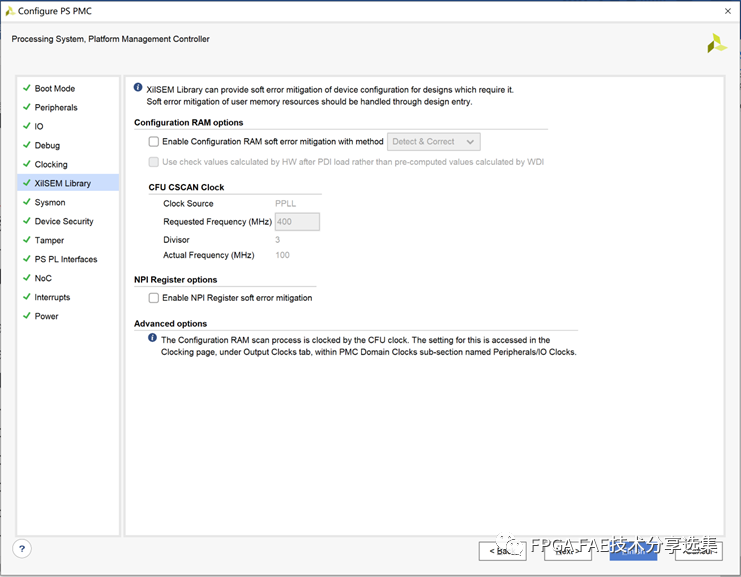

4、Xilinx SoftError Mitigation (XilSEM)庫配置

Xilinx Soft Error Mitigation (XilSEM)庫提供了一種預配置和預驗證的解決方案,用于檢測并可選地糾正VersalACAP配置存儲器中的軟錯誤。CIPS可以啟用XilSEM庫的基本功能。XilSEM庫的高級功能可以通過應用于設計的屬性進行訪問。

???????????

???????????

圖12 XilSEM庫配置

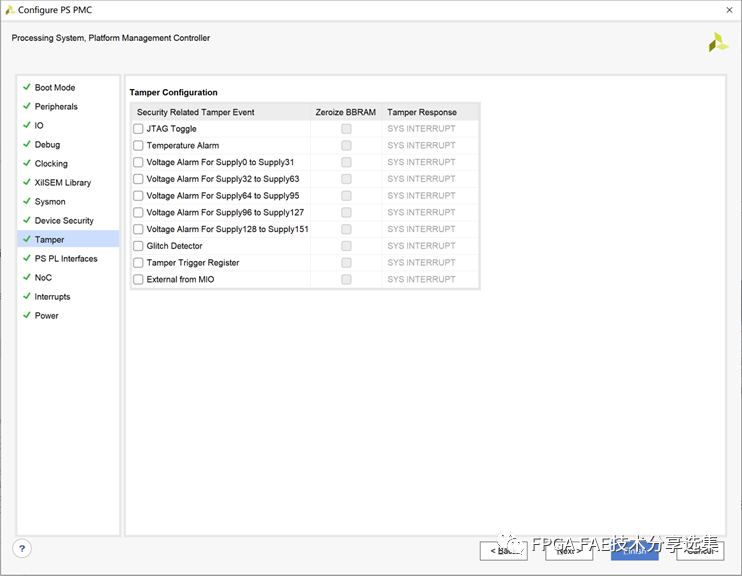

5、篡改事件/響應配置

Tamper事件是來自篡改監(jiān)測功能的中斷。Tamper監(jiān)測系統(tǒng)在檢測到電源毛刺、溫度偏差、調試(JTAG)切換檢測、自定義用戶(外部MIO)事件、Tamper寄存器事件和電壓告警事件時,CIPS中產生中斷,對上述每個篡改事件有不同的響應,用戶可以為每個篡改事件選擇不同的響應。

??????

??????

圖13 Tamper事件/響應 配置

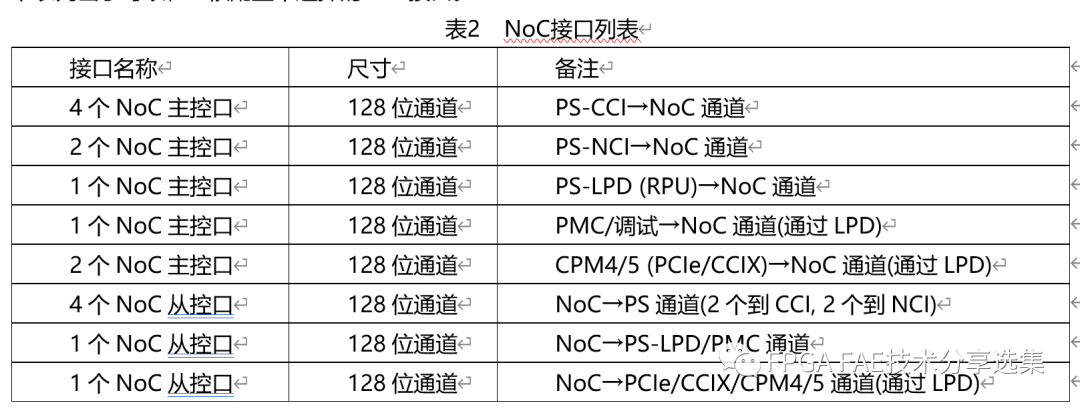

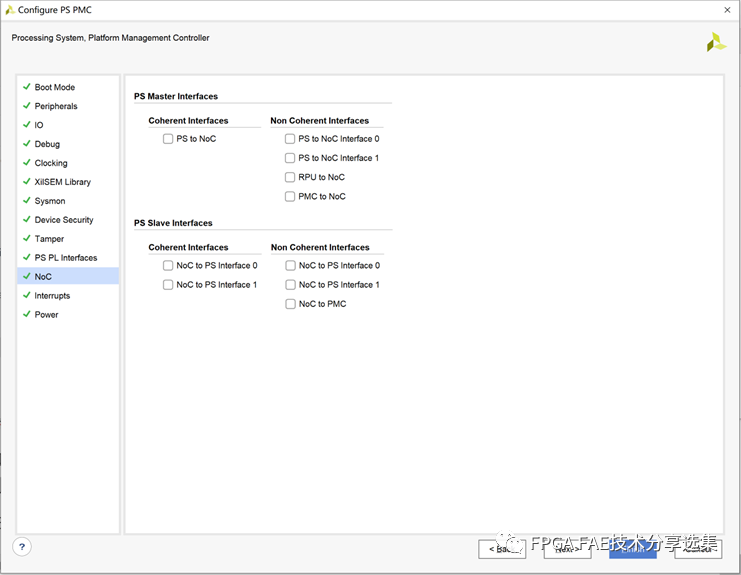

6、PS-NOC接口

PS-NoC接口選項支持從CIPS處理器到其他通用設備資源(如DDR、AI引擎和PL)的內存映射連接。下表列出了可以在IP核配置中選擇的NoC接口。

CIPS IP核PS-NoC接口顯示了啟用這些端口的不同NoC主/從端口選項,如圖17所示。

下表3顯示了可以分配給連接到CIPS主NoC端口的DDR/AI Engine/PL從機的地址。

????????

????????

圖14 PS-NoC接口

以下是關于PS-NoC端口使用的一些建議。

如果設計有AI引擎,那么你必須啟用PMC NoC端口來配置AI引擎。

默認情況下,32位RPU無法訪問或控制其32位地址的AI引擎。

所有4個PS到NoC的CCI端口必須連接到NoC。

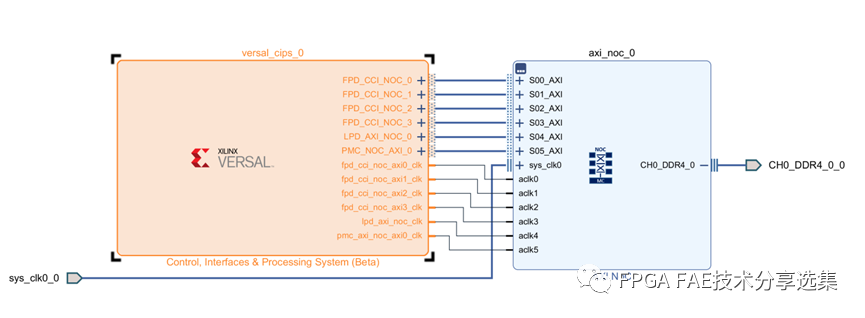

NoC上CIPS +DDR + PL從連接示意圖如下圖18所示:

圖15 CIPS NOC

關于NOC可以同時參閱公眾號里面“AMD Versal系列FPGA NoC介紹及實戰(zhàn)”文章。

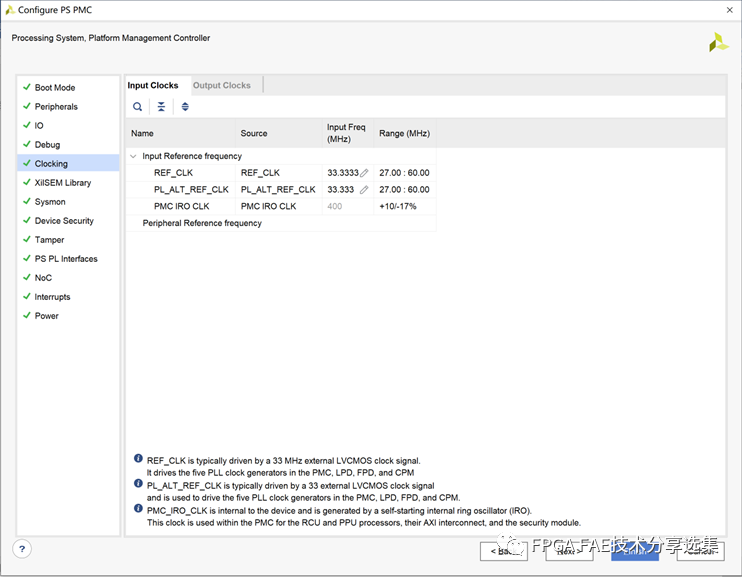

7、時鐘配置

該界面可以用來配置外設時鐘、PL時鐘、DDR內存、AI引擎和CPU時鐘。時鐘組分為如下三種:

主時鐘組(MCG):包括RPU PLL、APU PLL、PMC PLL、NOC PLL以及CPM4/5PLL。

RTC時鐘組(RCG)。這是一個實時時鐘,一個專用于RTC的內部時鐘。這個時鐘不需要時鐘分頻器。

ICG (interface Clock Group)。該組具有外部提供的時鐘,例如來自物理端接口(PHY)和PL的時鐘。PL側外設可以通過PL時鐘(PL_REF_CLK)操作。

輸入時鐘:

輸入參考頻率:這是來自板載時鐘源(REF_CLK)的時鐘頻率。

外設參考頻率:本節(jié)列出時鐘引腳和由MIO引腳驅動時鐘的外設的輸入頻率。

?????????????

?????????????

圖16 輸入時鐘配置

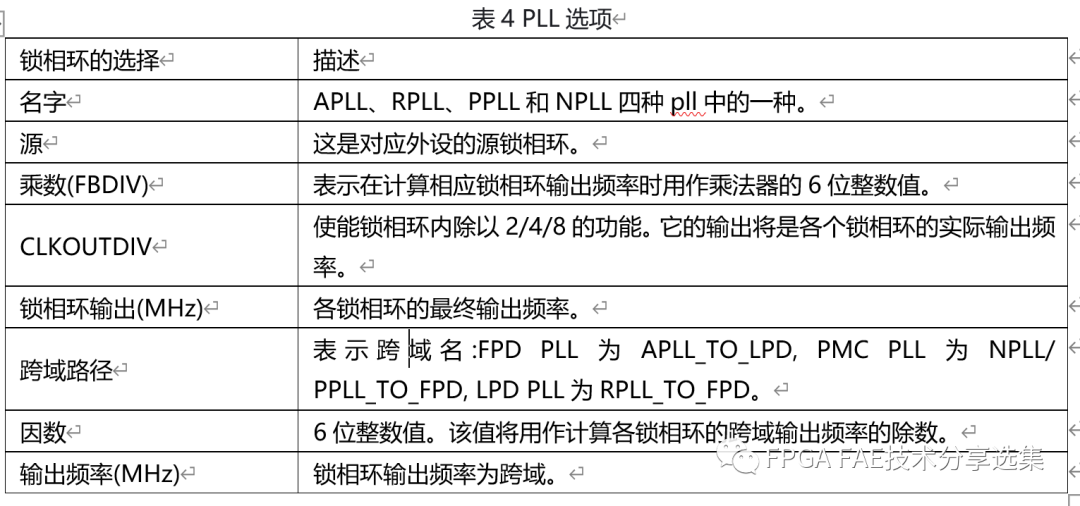

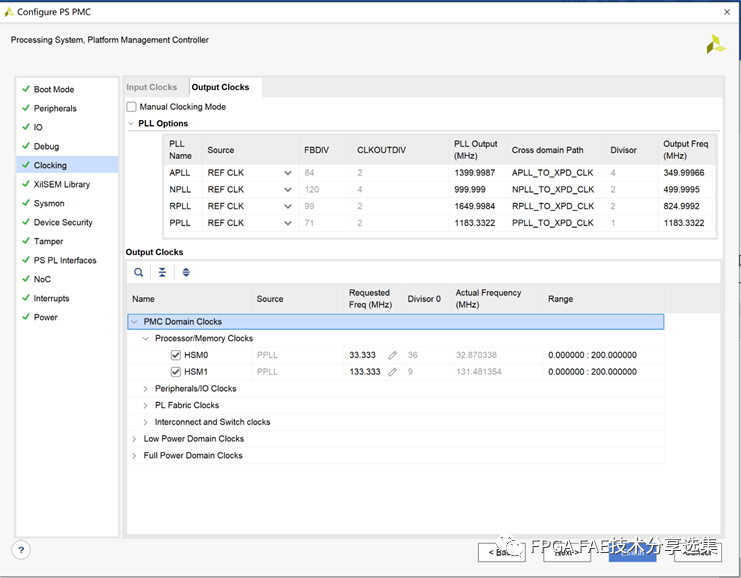

輸出時鐘顯示允許更新頻率的默認/用戶選擇的外圍時鐘,輸出時鐘保持不同的域鎖相環(huán)。

PS和PMC中的PLL是:

?APLL:位于FPD領域的APU PLL

?NPLL:位于PMC域中的NoC PLL

?RPLL:位于LPD域的RPU PLL

?PPLL:位于PMC域中的PMC PLL

在默認模式下(當手動模式關閉時),核自動選擇源鎖相環(huán)并計算M(乘法器)和D(除數器)值,以確保工具滿足請求的頻率到最接近的可能值。因為每個PLL都滿足多個外設的需求,核可能無法實現所有請求的值。如下圖17所示。

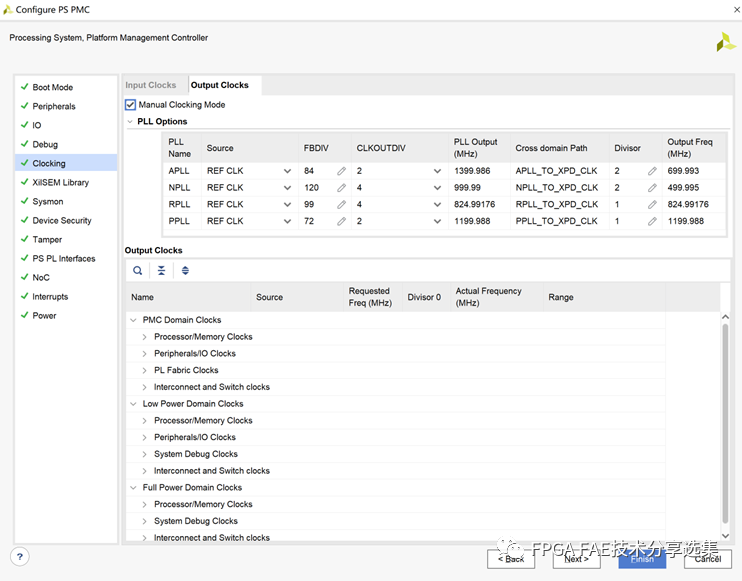

啟用手動時鐘模式時,會顯示不同的選項。用戶可以直接輸入各種鎖相環(huán)的源鎖相環(huán),M和D值以及單個外圍時鐘除數值,從而實現更精細的控制。在手動時鐘模式下,輸入Ref時鐘頻率為33.33 MHz時給出默認除數值。如果您以不同的參考時鐘頻率移動到手動模式,那么您將遇到用戶需要手動解析除數值的DRC。如下圖18所示。

?????????

?????????

圖17 輸出時鐘配置(默認模式)

???????????

???????????

圖18 輸出時鐘配置(手動模式)

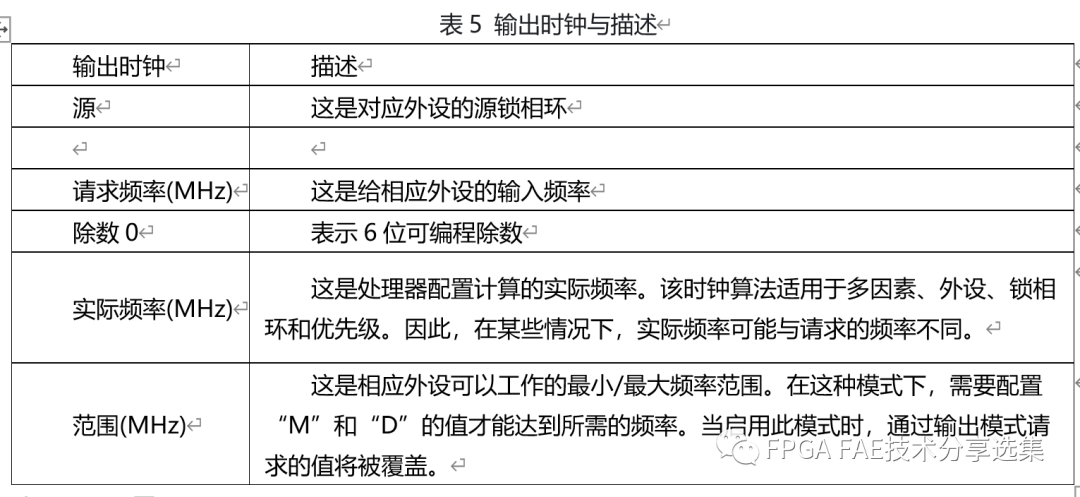

? ?

? ?

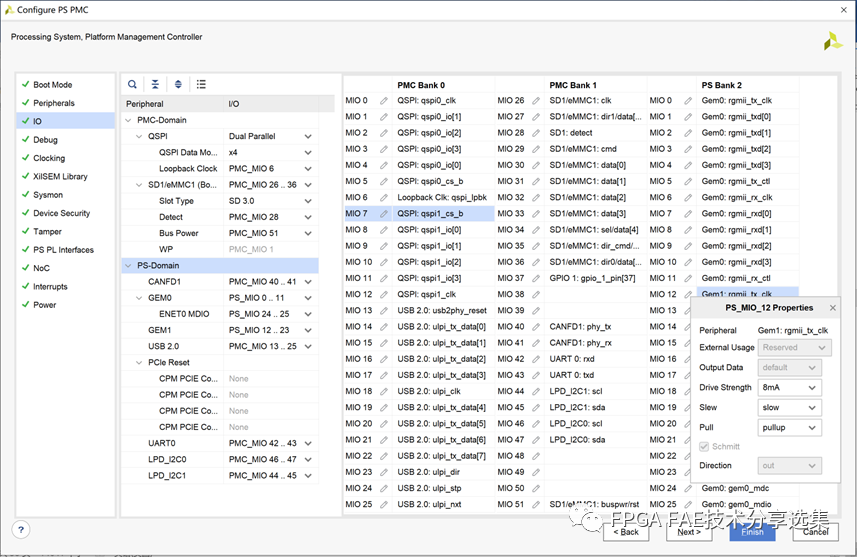

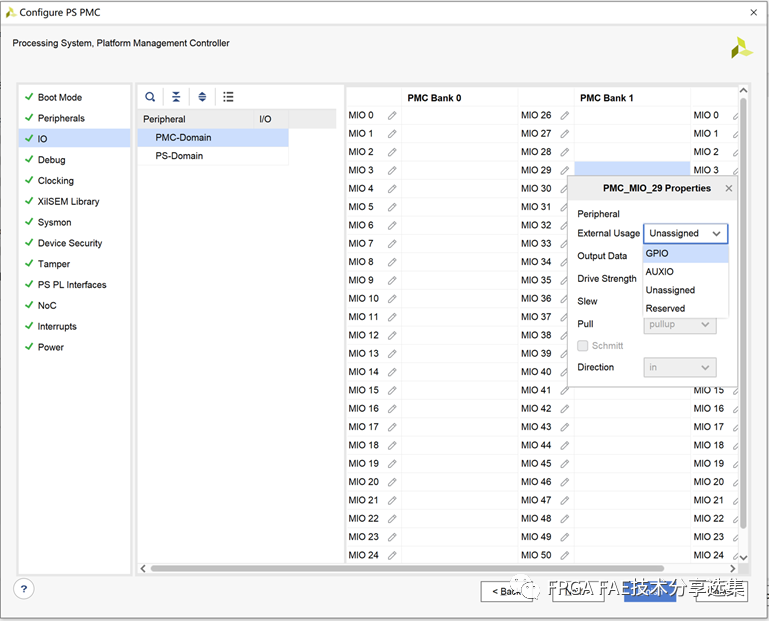

8、I/O配置

I/O Configuration頁面反映了外設及其I/O連接性。您可以為信號分配屬性。I/O外設分為PMC和PS兩個域,共有78個MIO, PMC區(qū)域有52個(PMCMIO Bank0和PMC MIO Bank1), PS區(qū)域有26個(LPD MIO Bank)。每個IO可以根據規(guī)則分配給任何外設。

或者,來自每個外設的相同引腳可以路由到EMIO信號,這將信號帶到設備的PL部分進行進一步處理。可用于外圍引腳的MIO分為三個Bank: PMC MIO Bank0 (MIO 0-25), PMC MIOBank1 (MIO 26-51)和LPD MIO Bank (MIO 52-77)。每個Bank的所有IO都有一個通用的I/O電壓標準,默認值是LVCMOS1.8,還有LVCMOS2.5和LVCMOS3.3兩個I/O電壓標準選項。

您可以選擇外設,GPIO和核篡改信號,以利用MIO。如果多個外設之間發(fā)生任何MIO沖突,將顯示DRC消息以發(fā)出警報。每個外設都有不同的支持MIO集,您可以在這些外設之間進行調配,以避免外設間MIO的DRC發(fā)生沖突。此外,每個外設都有EMIO選項,也可以選擇這個選項來解決MIO沖突。

在I/O配置頁面啟用外設后,您將能夠在時鐘配置中設置相應的外設頻率。

對于每個MIO,都有一組引腳屬性,用戶可以通過單擊各自的MIO在核心中設置這些屬性。

??????????

??????????

圖19 I/O配置

a、MIO IO接口

MIO保留功能允許您選擇未使用/未分配的MIO作為GPIO/AUX- IO。要選擇這些,您需要單擊工具欄上的MIO PIN view按鈕,然后在被認可的MIO的外部使用列中選擇GPIO/AUX-IO選項。如果有任何MIO被分配給外設,那么這個MIO不能被設置為GPIO/AUX-IO,所以它的外部用法下拉列表被禁用。

如果MIO使用率為GPIO,則可以將其輸出數據設置為active-High或active-Low,方向設置為In或Out。在啟動后,當設置為Out方向時,該值將在IO上驅動。只有MIO用做是AUX-IO,才能設置方向為In/Out。

圖20 MIO I/O保留設置

在“IO配置”界面中還可以選擇PMC域的64個GPIO-EMIO引腳,PS域的32個GPIO-EMIO引腳。啟用后,這些引腳將暴露到PL區(qū)域。

在通用設計工具中,CIPS IP核用于配置核多用途IO (MIO)端口。CIPS IP核有多達78個MIO端口可用。該核允許您選擇連接到MIO端口的不同外設端口。

b、EMIO接口

由于最多只有78個MIO端口可用,因此許多超出這些端口的外設I/O端口仍然可以通過擴展MIO (EMIO)接口路由到可編程邏輯。

通過可編程邏輯的IOP接口的替代路由使您能夠充分利用CIPS IP核中可用的IOP。通用CIPSIP核允許您選擇多達96個GPIO信號。通用CIPS IP核具有控制邏輯,可以調整流入CIPS IP核的用戶選擇寬度。用于I2C、SPI閃存、千兆以太網管理數據輸入/輸出(MDIO)、SD/eMMC、GPIO 3狀態(tài)使能的EMIO信號在通用CIPSIP核中會反轉。

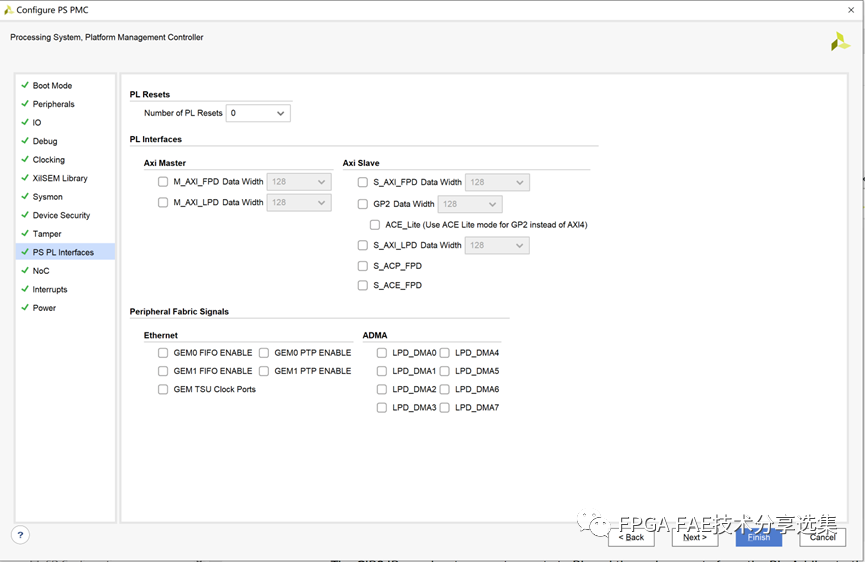

9、PL-PS配置

PL-PS配置頁面控制哪些接口暴露給PL。圖24PL- PS接口說明了控制,接口和處理系統(tǒng)IP核中的PL-PS接口,其中有兩個GP主端口到PL和三個GP從端口來自PL。此外,還有一個ACE和一個ACP端口來自PL。所有這些端口的最大數據寬度為128位。

圖21PL-PS接口

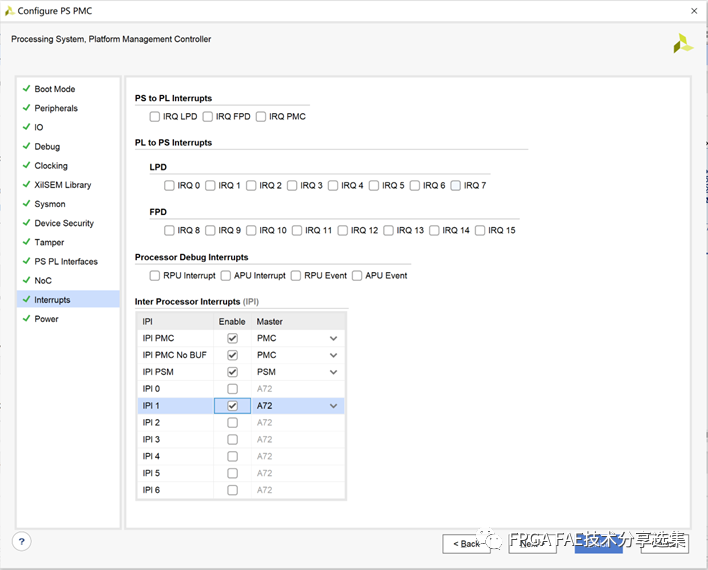

10、PL中斷

控制接口和處理系統(tǒng)IP核提供3個PS到PL中斷接口(依次為每個外設提供大量共享中斷)和16個PL到PS中斷。此外,CIPS IP核有一個處理器和調試中斷列表。“InterruptConfiguration”工具簽用于啟用/禁用CIPS核心與PL之間的中斷。

圖22 中斷配置

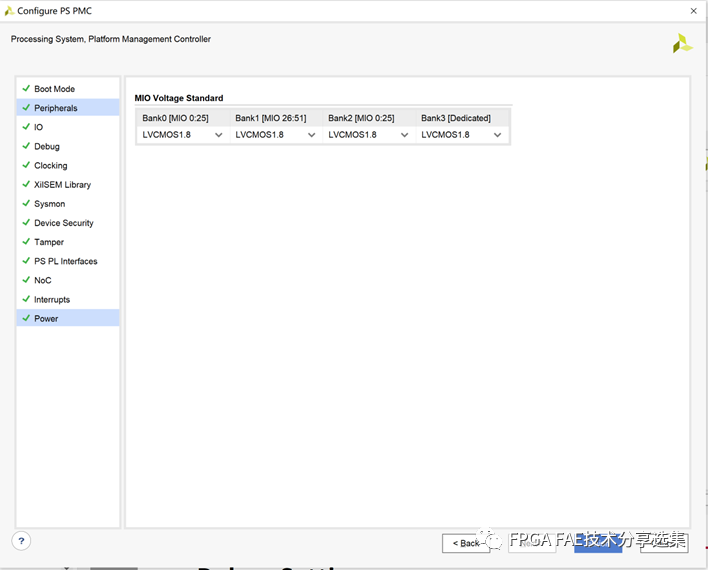

11、電氣特性配置

此頁面允許您為Bank選擇LVCMOS。對于所有相應的IO,每個Bank都有一個通用的I/O電壓標準。默認值是LVCMOS1.8,還有兩個選項LVCMOS2.5和LVCMOS3.3 I/O電壓標準。

此設置必須反映每個MIO Bank使用的板LVCMOS電壓。這些設置不用于設置任何寄存器或MIO電壓。Vivado report_power使用它們來估計功耗。

?????

?????

圖23 MIO電壓標準

12、Debug設置

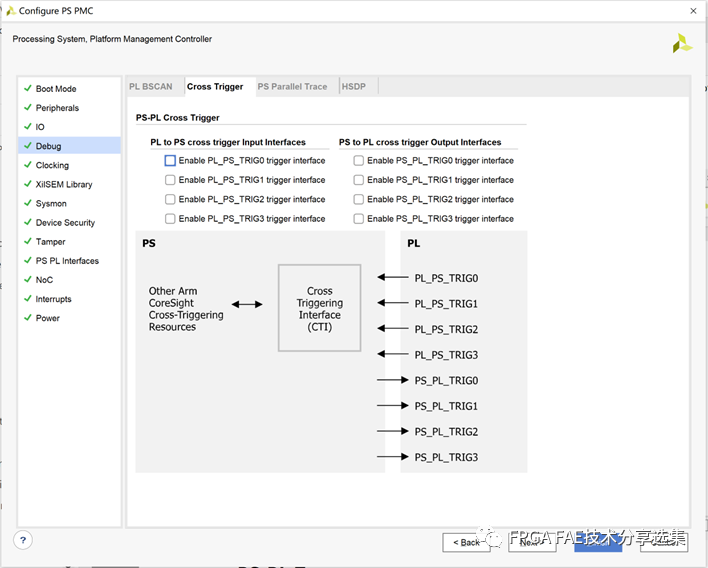

a、PS-PL交叉觸發(fā)

PL到PS的交叉觸發(fā)器輸入是來自PL的觸發(fā)器輸入。您可以啟用這些端口以從硬件獲取觸發(fā)器事件并將其提供給ILA以分析/調試硬件狀態(tài)。

PS到PL交叉觸發(fā)輸出可用于設置軟件中的調試斷點以停止硬件。一旦給硬件觸發(fā)事件,軟件就會訪問硬件狀態(tài)進行調試。

???

???

圖24 PS-PL交叉觸發(fā)器配置

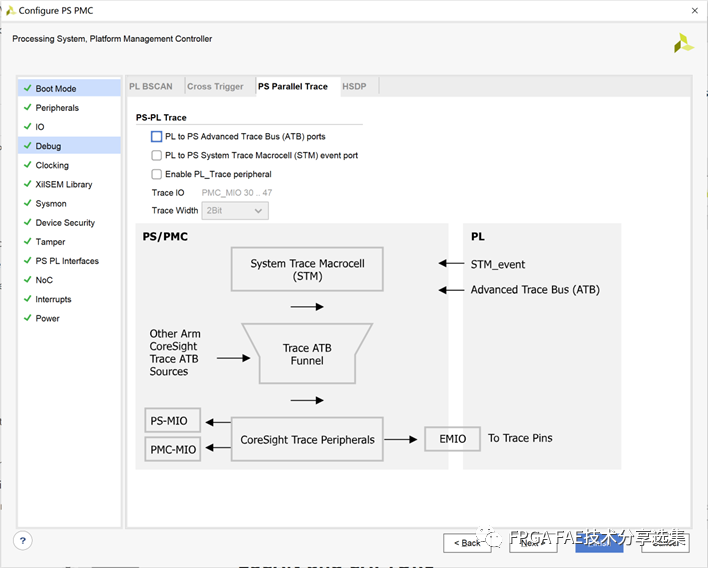

b、PS-PL跟蹤

啟用PL到PS高級跟蹤總線(ATB)端口將啟用CIPSIP上的ATB端口,允許PL訪問高級跟蹤總線。

PL 到 PS 的System Trace Macrocell (STM)事件端口將使能CIPS IP上的STM端口,允許PL訪問CoreSightSystem Trace Macrocell。

片外并行跟蹤允許通過MIO或EMIO從PS輸出跟蹤數據到PL。啟用PL_Trace外圍設備允許從IO面板視圖中選擇MIO或EMIO。

對于通過EMIO進行跟蹤,可以使用PL IP連接到PS-PL跟蹤接口,并根據Arm跟蹤標準向PL XIO輸出跟蹤數據。PL XIOs通常連接到Mictor連接器,其中跟蹤探針可以收集跟蹤數據,以便在調試IDE中進行分析。

圖25 PS-PL跟蹤配置

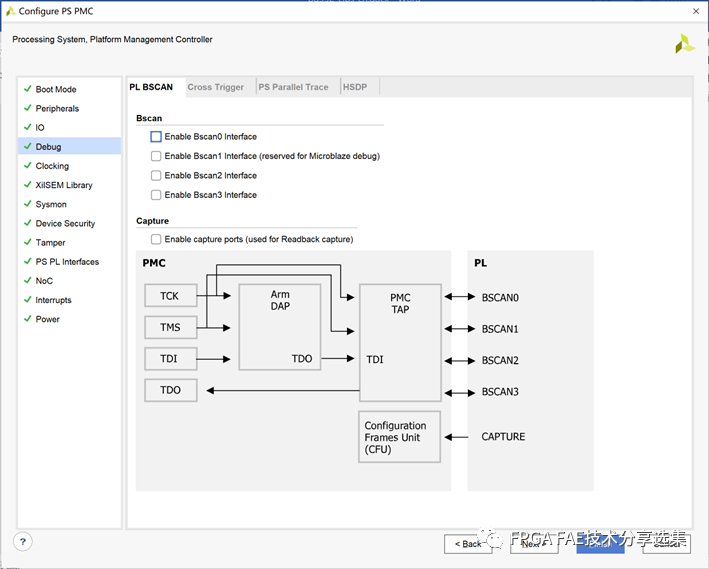

c、BSCAN和CAPTURE

有四個BSCAN接口可用于連接任何支持BSCAN的PL調試模塊。BSCAN接口連接到PMC測試接入點(TAP)控制器,用于調試/邊界掃描目的。CAPTURE端口提供用戶控制和同步,控制何時以及如何請求捕獲寄存器信息任務。只有寄存器觸發(fā)器和鎖存狀態(tài)可以被捕獲。

圖26 BSCAN和CAPTUREConfiguration

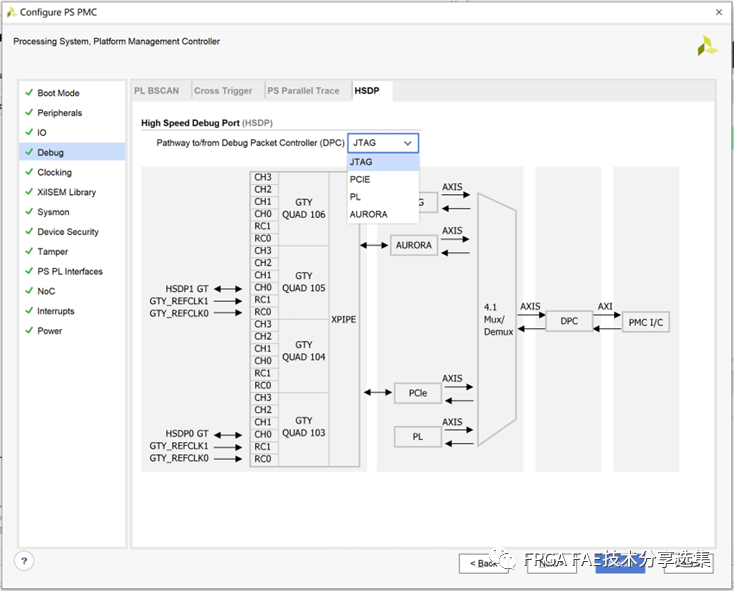

d、高速調試端口(HSDP)

高速調試端口是為可編程邏輯(PL)、處理系統(tǒng)(PS)和AI引擎提供調試和跟蹤的協議。HSDP可以在設備上使用千兆收發(fā)器,提供比JTAG接口更好的性能。

由于HSDP是一種協議,事務層由調試包控制器(DPC)處理,鏈路層可以是下面列出的四個接口之一:

?JTAG

?HSDPAurora(硬化的Aurora IP)

?CPMPCIe控制器

?PLAurora (Aurora軟IP)

?????

?????

圖27 高速調試端口

13、啟動模式

Versal設備啟動方式與傳統(tǒng)FPGA不同。不再有獨立的比特流,而是在通用設備中有一個可編程設備映像(PDI),其中包括一個PL配置幀數據。CFI (Configuration Frame Interface)是通過配置幀數據來配置配置幀的接口。CFI屬于PMC,PMC BootROM負責通過選定的引導介質從PDI讀取PLM。

PLM包括啟動設備配置。在“啟動方式”頁面中選擇啟動方式。根據單板支持的啟動方式,可以選擇多種啟動方式。時鐘設置,如啟動外設所需頻率和REF_CLK頻率可在此頁面設置。如果您只想使用PL部分,則應該使用此頁面來配置啟動外設。

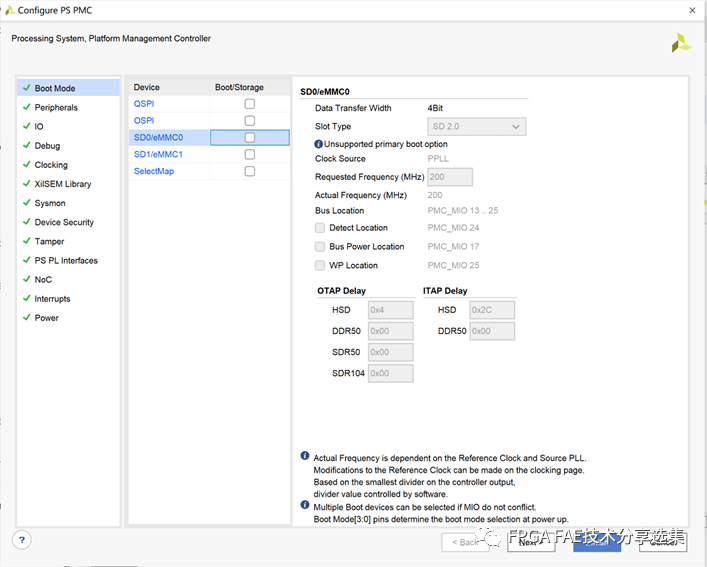

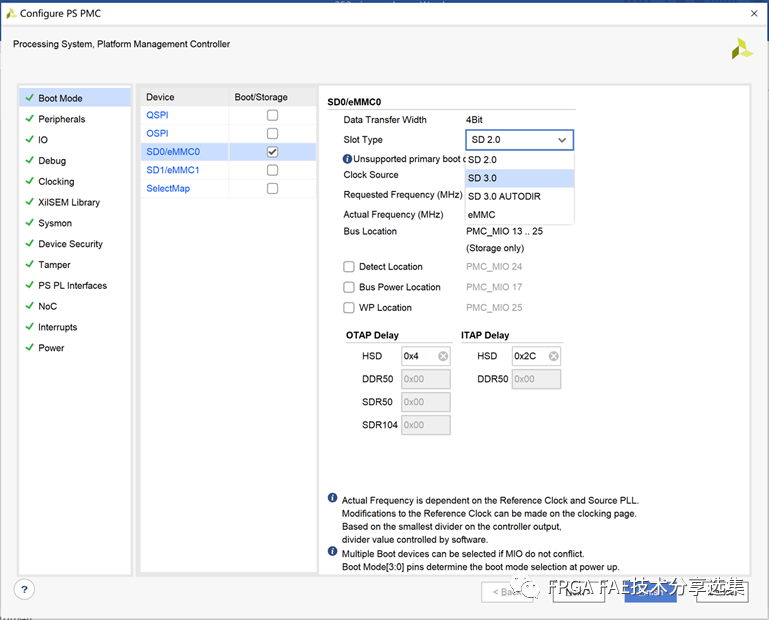

QSPI、OSPI、SD0、SD1、eMMC1和SelectMAP都是主要的啟動外設選項。如果選擇的MIO不支持主啟動,則SD0、SD1和eMMC1設置提供標志。

在VivadoGUI為SD0/1中顯示一條關于使用存儲或啟動(和/或)存儲的信息消息。

STARTUP選項可用于將設備引腳和邏輯接口到全局異步設置/復位信號,全局3態(tài)專用路由和啟動結束(EOS)。

在Tcl命令提示符中支持的STARTUP選項,您可以設置CONFIG.PS_PMC_CONFIG設置為1,以獲取CIPS上的基本端口。

圖28 啟動模式配置

在配置SD 0/eMMC0或SD 1/eMMC1控制器時,有多個選項可用。

圖29 SD /eMMC配置

審核編輯:劉清

-

收發(fā)器

+關注

關注

10文章

3551瀏覽量

107036 -

控制器

+關注

關注

114文章

16823瀏覽量

182166 -

片上系統(tǒng)

+關注

關注

0文章

187瀏覽量

27139 -

片上網絡

+關注

關注

0文章

33瀏覽量

11923 -

ACAP

+關注

關注

1文章

54瀏覽量

8313

原文標題:AMD Versal系列CIPS IP核介紹

文章出處:【微信號:Comtech FPGA,微信公眾號:Comtech FPGA】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

CIPS 3.0變更日志和移植信息解決方案

Versal CPM AXI Bridge模式的地址轉換

設置AMD以太網IP核的Pause幀處理

AMD發(fā)布第二代Versal自適應SoC,AI嵌入式領域再提速

ALINX VERSAL SOM產品介紹

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

AMD推出第二代Versal Premium系列

AMD Vivado Design Suite 2024.2全新推出

AMD Versal自適應SoC器件Advanced Flow概覽(下)

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

評論