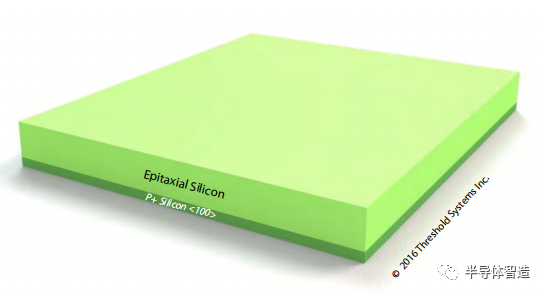

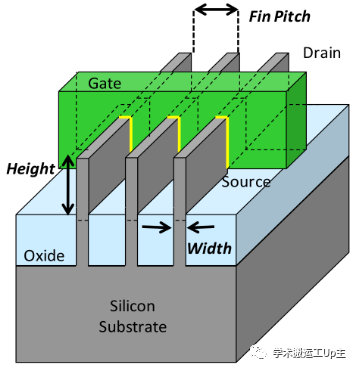

今天分享另一篇網(wǎng)上流傳很廣的22nm 平面 process flow. 有興趣的可以與上一篇22nm gate last FinFET process flow 進行對比學習。 言歸正傳,接下來介紹平面工藝最后一個節(jié)點22nm process flow。

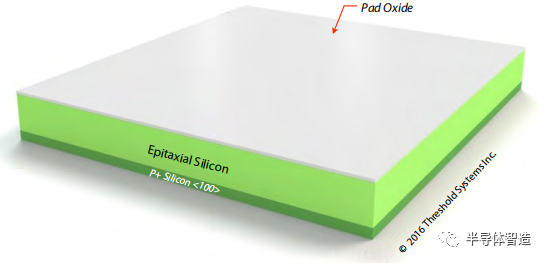

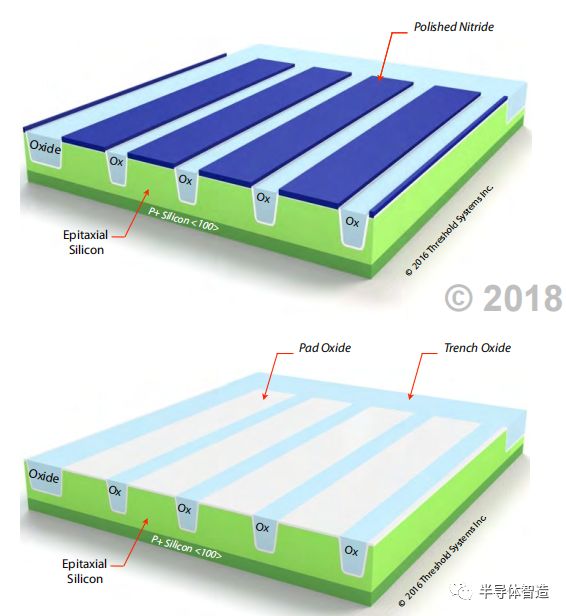

Pad Oxide Growth

首先是P型襯底上面有一層外延生長的Si,然后再生長一層Pad Oxide。此氧化層充當后面SiN和底層硅表面之間的應力緩沖層,并防止SiN對硅表面造成損傷。

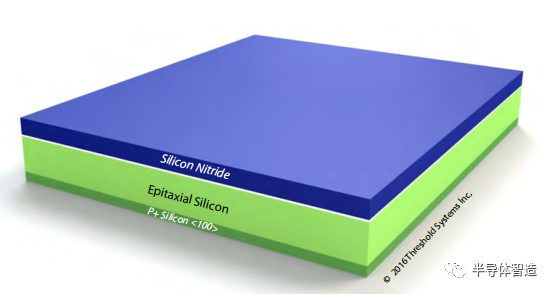

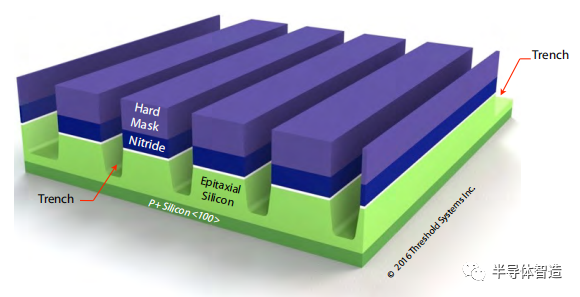

2.Nitride Barrier Deposition

接下來,通過化學氣相沉積(CVD)方法沉積一層厚度約1,200?左右的SiN。然后,將晶片在SC1溶液中清洗。

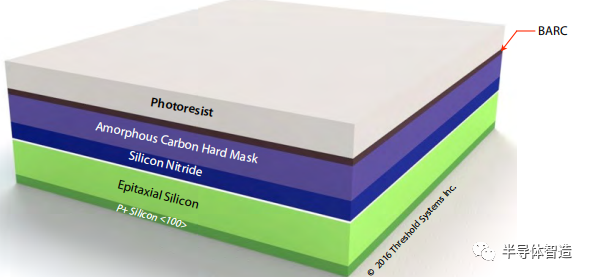

3.Hard Mask Deposition & Lithography

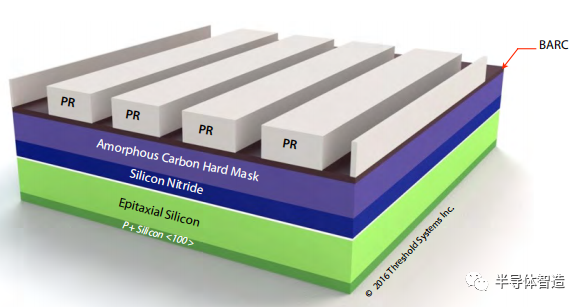

使用化學氣相沉積(CVD)方法,在晶片表面沉積一層厚度為2,000?的Amorphous Carbon(A-C)。然后在其上沉積一層厚度為500?的底部防反射涂層(Bottom Anti-Reflective Coating, BARC)。A-C將充當一種硬掩膜(hard mask)。接下來,將約3,000?的光刻膠涂敷在晶片上,并進行烘烤(soft baked)。

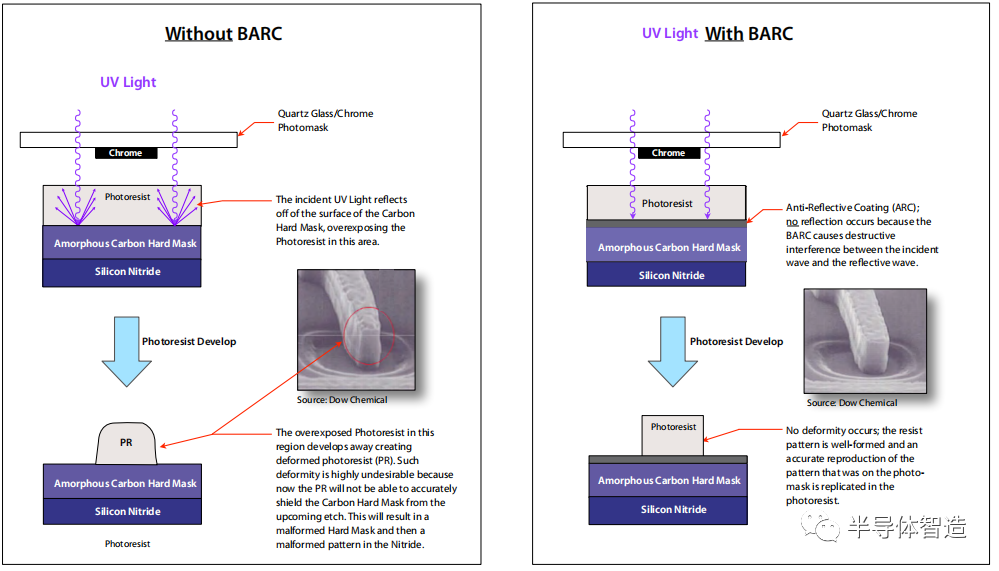

Bottom Anti-Reflflective Coatings (BARC )

4.Hard Mask Defifinition

然后對其進行曝光和顯影。將Mask上的pattern轉(zhuǎn)移到Hard mask上。

5.Photoresist Strip & Trench Etch

用SPM去除PR,并繼續(xù)往下刻蝕,形成STI的結構。

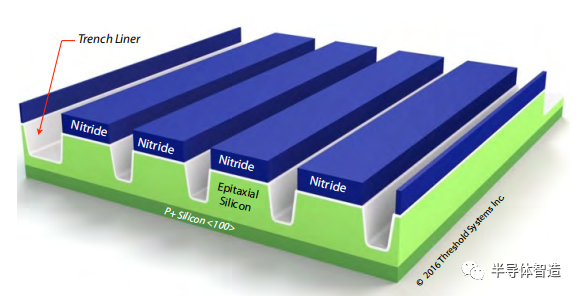

6.Trench Liner Growth

晶片再次經(jīng)過清洗(HF/SC1/SC2),然后在溝槽中生長出100?厚度的二氧化硅層。這個氧化層被稱為“溝槽襯墊”,有助于緩解溝槽上下角附近硅材料的應力。

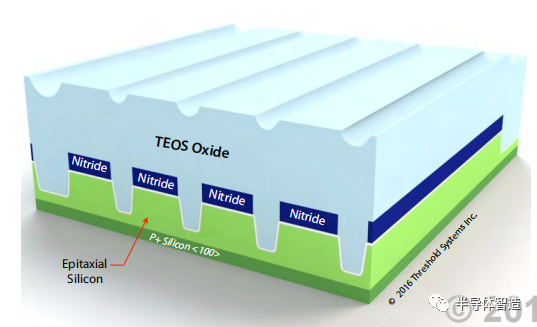

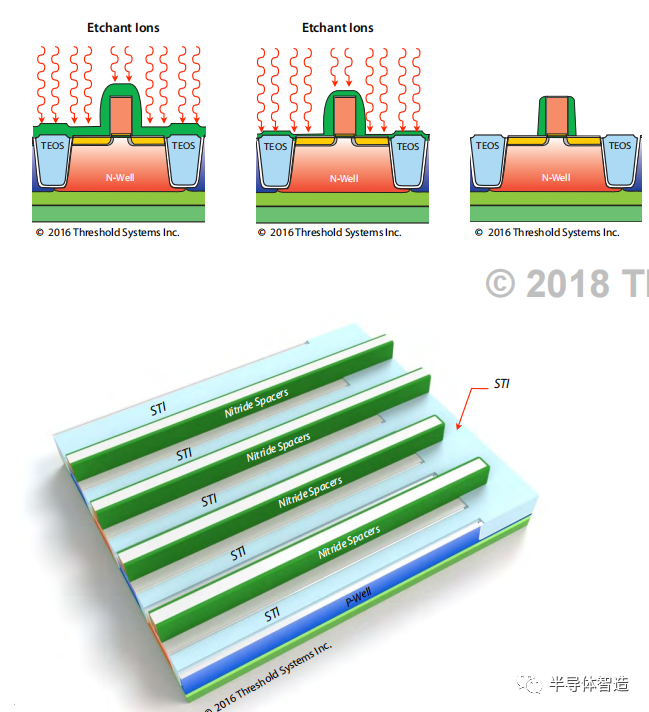

7.Trench Fill

然后沉積了4,000 ? 的TEOS(四乙基正硅酸酯)氧化物。TEOS是通過化學氣相沉積(CVD)沉積的氧化物,與生長(熱)氧化物相對。它的主要優(yōu)勢是可以快速沉積厚度較大的氧化物。它的主要缺點是沉積的TEOS氧化物不如生長的氧化物致密。接下來,晶片在1,000?C加熱20分鐘,使TEOS變得更加致密,更具抗?jié)穹ㄎg刻的能力。

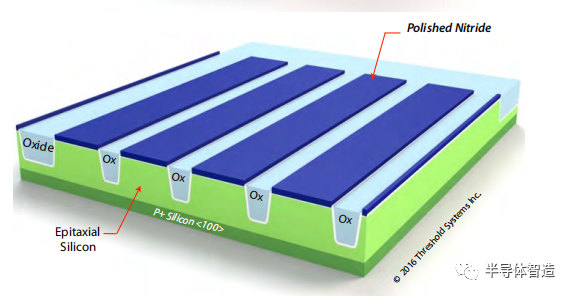

8.Oxide Polish

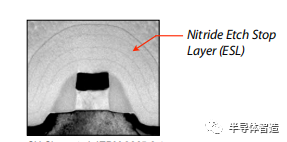

晶片經(jīng)過化學機械拋光(CMP)后。非常堅硬的氮化硅層起到了CMP停止作用。在氧化物被拋光后,表面上起CMP停止作用的薄層氮化物必須被去除。

9.Nitride Strip

在CMP后,表面的薄層氮化物必須被去除(通過將晶片浸入熱酸140oC的磷酸中20分鐘來去除殘留的氮化硅。磷酸對氮化硅具有較高的選擇性,而不會侵蝕氧化物)。

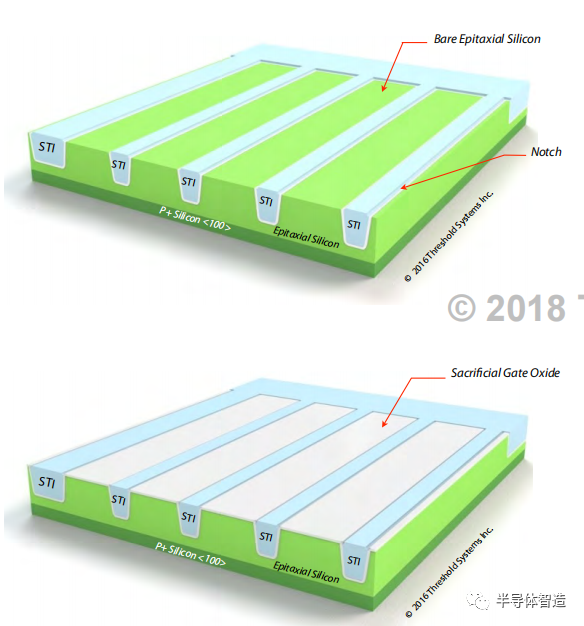

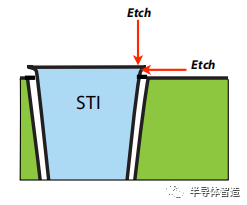

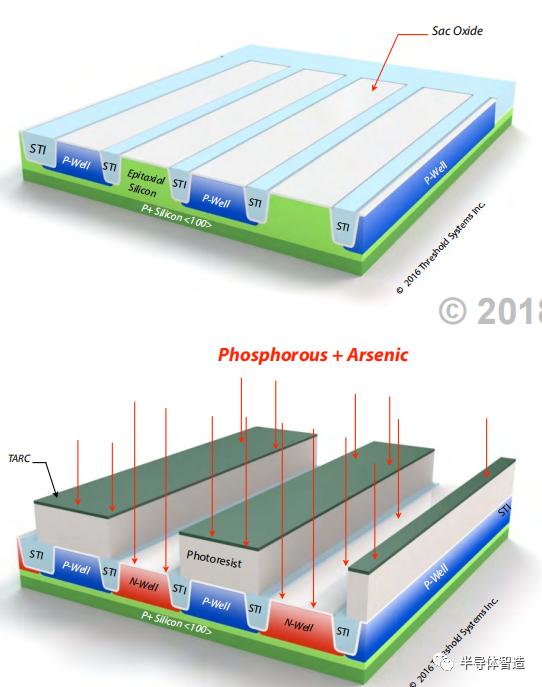

10.Pad Oxide Strip & Sacrifificial Gate Growth

接下來,將晶片浸泡在氫氟酸中,去除Pad Oxide。Pad Oxide去除過程中會優(yōu)先去除溝槽角落處的氧化物,因為這些區(qū)域受到應力并且蝕刻速度更快。這會導致溝槽的側面出現(xiàn)“凹槽”(Divot),可能在后續(xù)過程中引起問題。

然后晶片在SC1/SC2中進行清洗,并生長出50 ?的犧牲柵氧化物(Sac Ox)。犧牲柵氧化物也起到了屏蔽氧化物(Screen Oxide)的作用。

注:Pad Oxide的去除在溝槽的角落處優(yōu)先去除了氧化物,主要是因為STI(shallow trench isolation)氧化物是一種沉積氧化物,比Pad Oxide(生長熱氧化物)要軟得多。此外,STI 氧化物的角落區(qū)域受到機械應力影響,而受應力影響的微結構腐蝕速度更快。最后,在Pad Oxide蝕刻過程中,STI 氧化物的銳利角落受到兩側的攻擊,加速了這些角落的退讓。這種優(yōu)先腐蝕導致沿著溝槽側壁產(chǎn)生“凹槽”,可能在后續(xù)過程中引起問題。

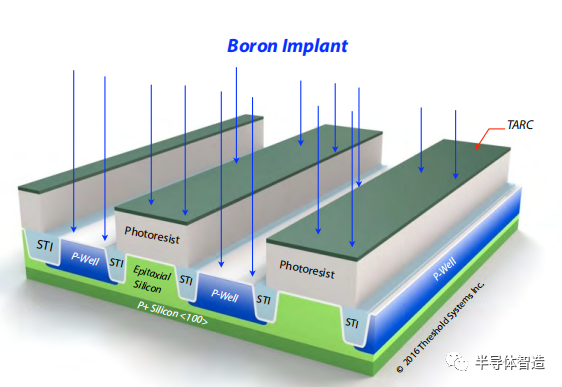

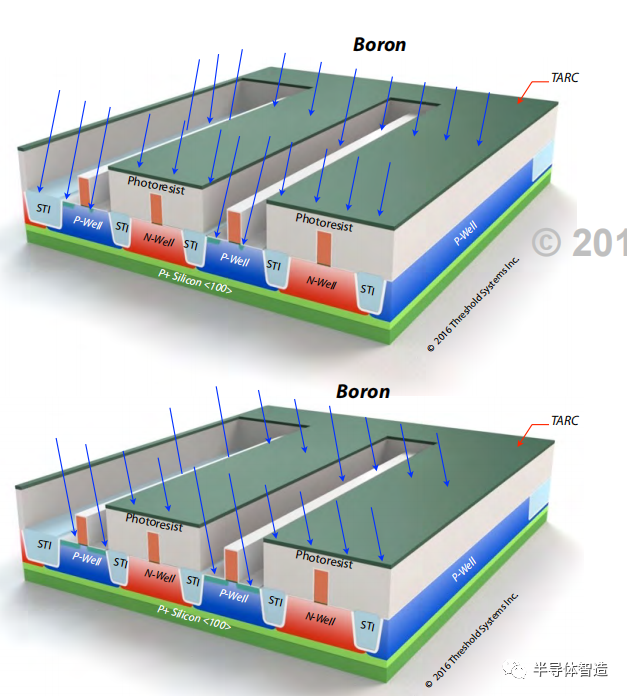

11.P-Well Implant

接下來,晶片被注入硼元素以建立反向摻入的P-Well。

12.Photoresist Strip and N-Well Implant

去完光阻,同理進行N-Well區(qū)的定義,主要進行磷和砷的注入。

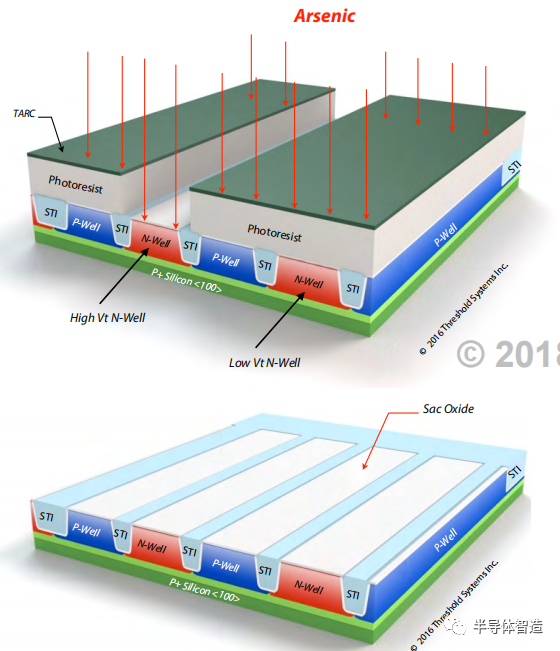

13.High Vt N-Well Vt Adjust

高壓N-Well接受As元素注入,使其具有比低壓N-Well更高的閾值電壓(Vt)。完成后并去膠。

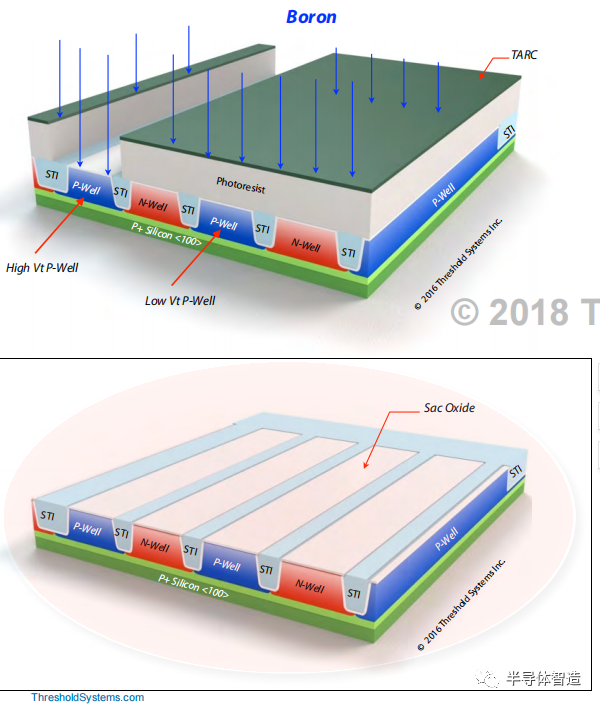

14.High Vt P-Well Vt Adjust & Well Anneal

同理,高壓P-Well接受B元素注入,使其具有比低壓P-Well更高的閾值電壓(Vt)

在完成井注入之后,晶片經(jīng)過快速熱退火(RTA),在1,000oC下加熱10秒鐘,以激活注入井中的雜質(zhì)元素。退火過程使摻雜原子電活性,并修復注入過程中對硅材料造成的損傷。

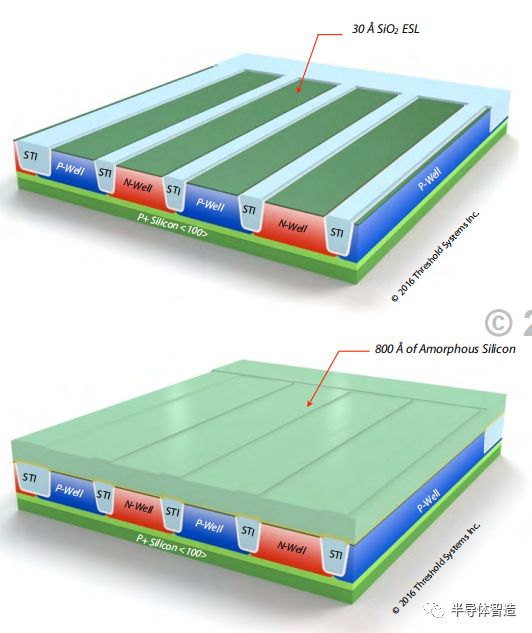

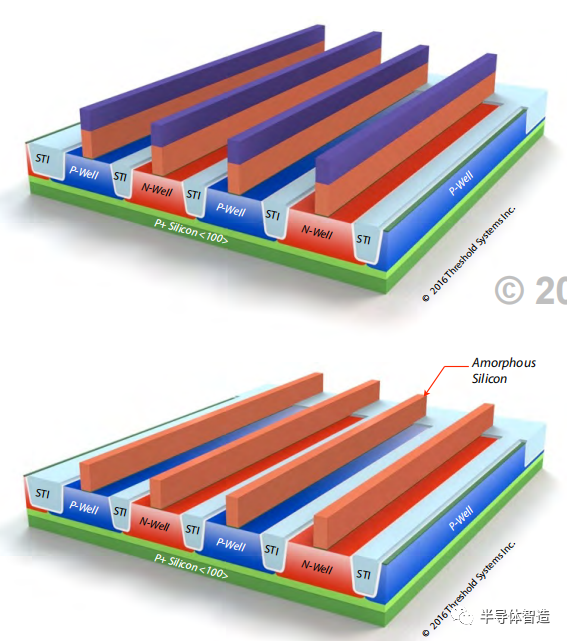

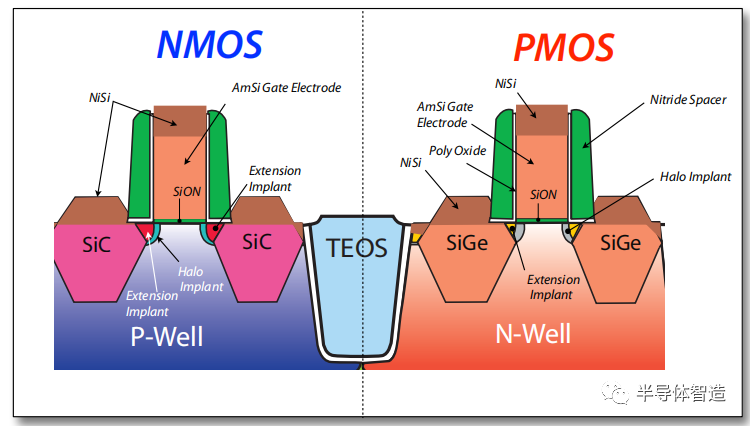

15.Oxide ESL Growth & AmSi Deposition

在晶片的表面上生長一個厚度為30?的SiON熱層氧化物,形成一個薄的刻蝕停止層(Etch Stop Layer,ESL)。當非晶硅柵極支撐柱(尚未沉積)被刻蝕掉時,這層氧化物將作為刻蝕停止層來保護晶體管通道。

請注意,在流程中的這個階段沒有進行Hi-k介電沉積。

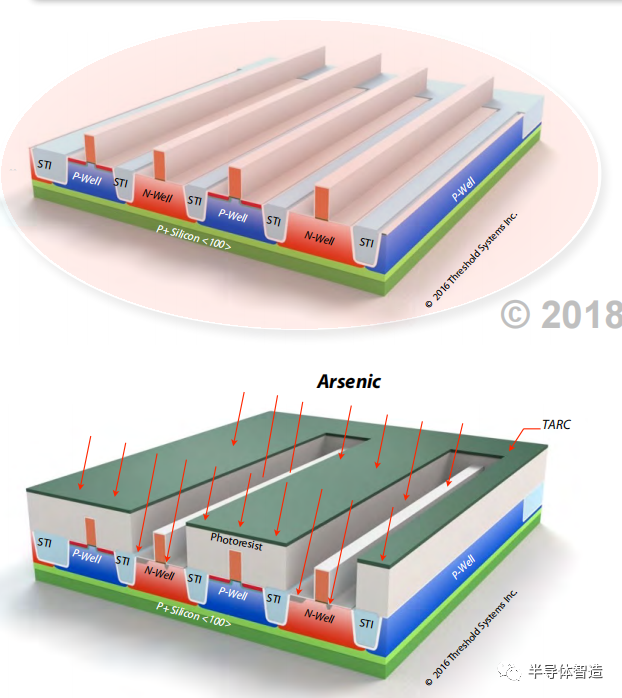

采用化學氣相沉積(CVD)技術沉積了厚度為800?的非晶硅(AmSi)。這里的非晶硅是未摻雜的。在進行圖案化和刻蝕后,非晶硅形成了犧牲性柵極支撐柱。

請注意,在非晶硅柵極電極下方?jīng)]有金屬柵極。

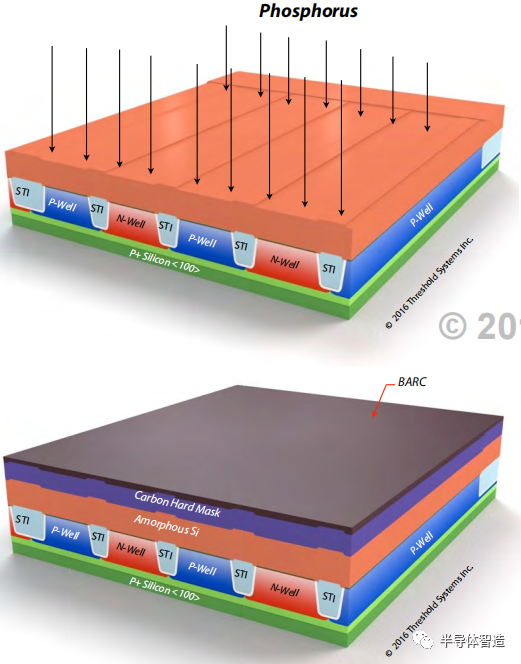

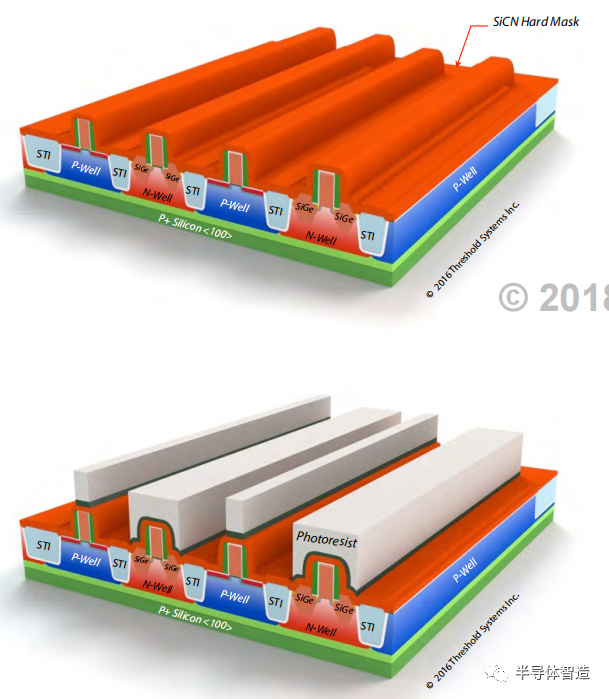

16.Amorphous Silicon Dope & Hard Mask Dep

非晶硅通過注入磷(Phosphorus)進行摻雜,以使其具有導電性。柵電極是犧牲性的,將在后續(xù)工藝中去除。摻雜柵電極有助于其去除,但并非必要。

接下來沉積了厚度為1,500?的非晶碳硬膜和厚度為300?的BARC層。

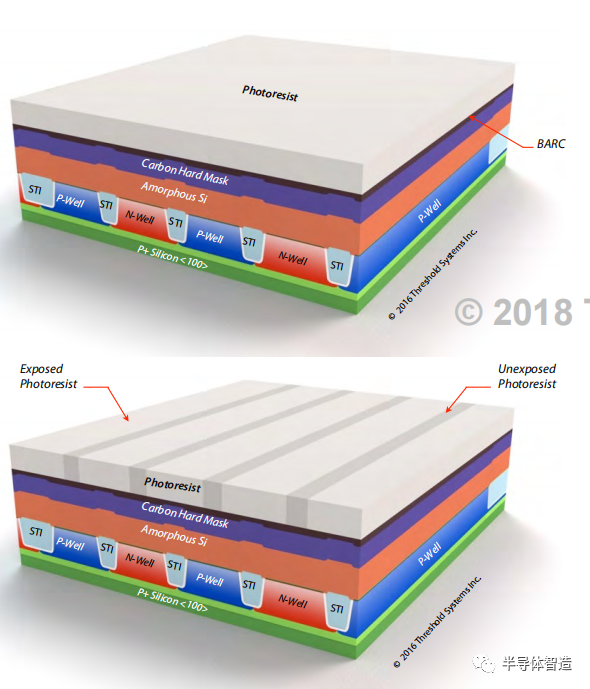

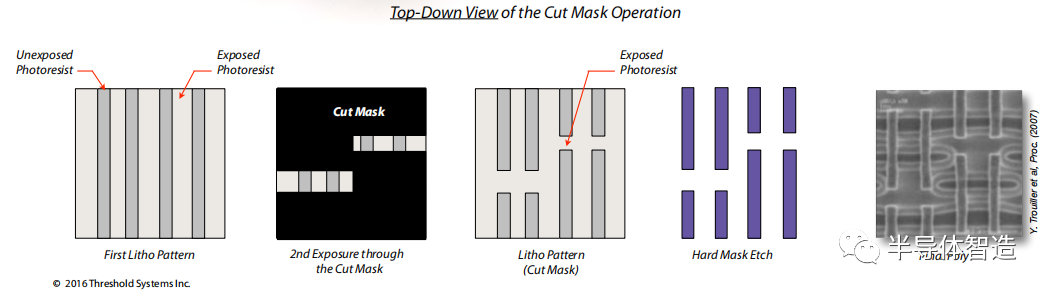

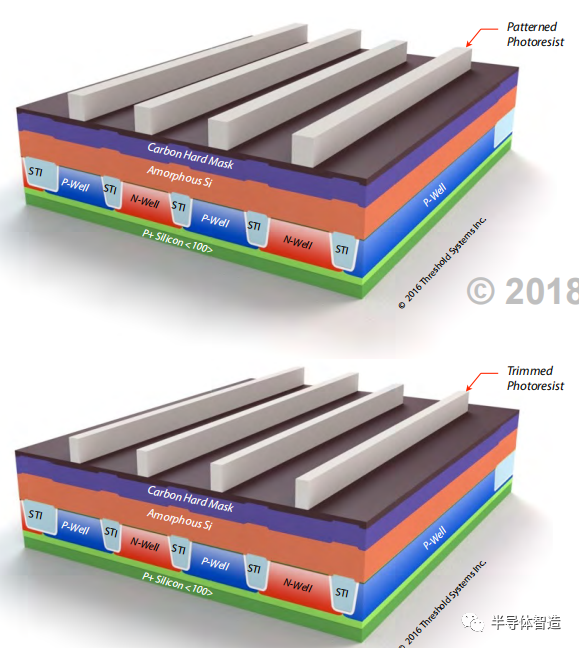

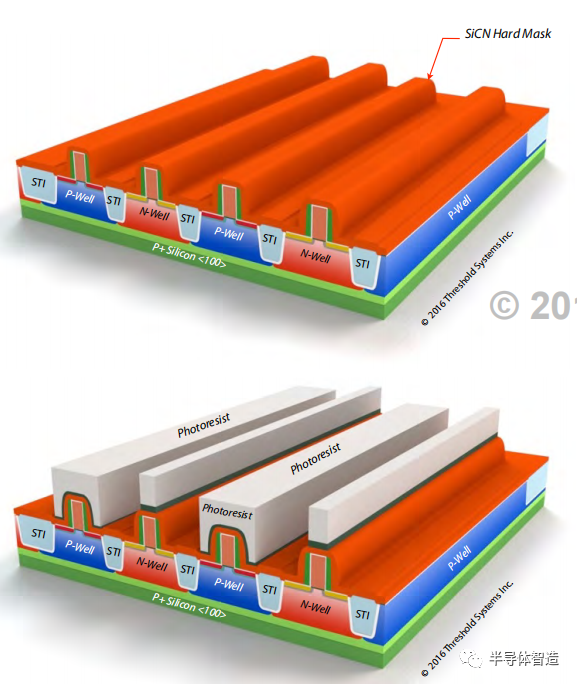

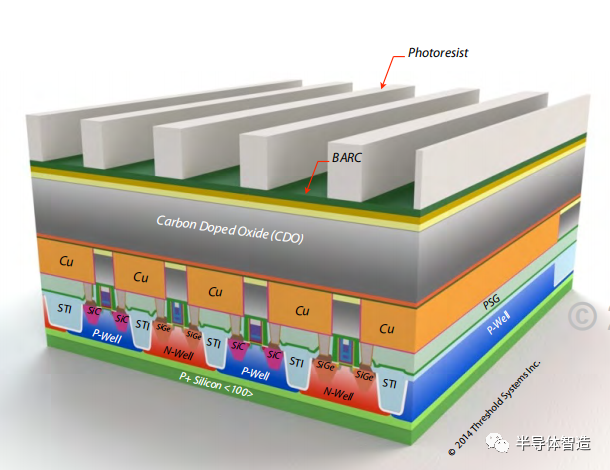

17.Photoresist Deposition & 1st Patterning

接下來,晶片會先在HMDS中進行預處理,然后涂覆BARC(底部抗反射涂層),光刻膠和光刻圖案。這是整個流程中最關鍵的光刻操作。它生成一系列平行線,接下來會通過隨后的光刻操作中的切割掩模來進一步定義這些線。

然后,使用一個光柵掩模對晶片進行曝光。該掩模只在一個方向上打印直線。光刻膠尚未進行顯影。

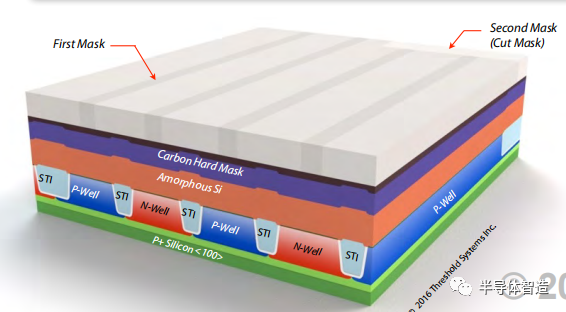

18.Cut Mask 2nd Patterning

接下來,通過一個“切割掩模”對光刻膠進行曝光,該掩模將未顯影的光刻膠暴露在與第一個掩模方向垂直的方向上。這樣可以沿著這個軸線暴露光刻膠,并允許將貫穿整個芯片的連續(xù)光柵線進行切割。

19.Photoresist Trim Process

在控制的氧等離子體下進行曝光,該氧等離子體會對圖案化的光刻膠進行各向異性刻蝕。這會導致光刻膠尺寸縮小到目標尺寸。這個過程被稱為“光刻膠修整,修整后的光刻膠線條現(xiàn)在更窄了,可以用來定義更窄的柵極電極。

光刻膠修整是一種技術,可以制造非常窄的光刻膠線條(因此也是窄的柵極電極線條),其尺寸比光學打印的光刻膠線條更小。

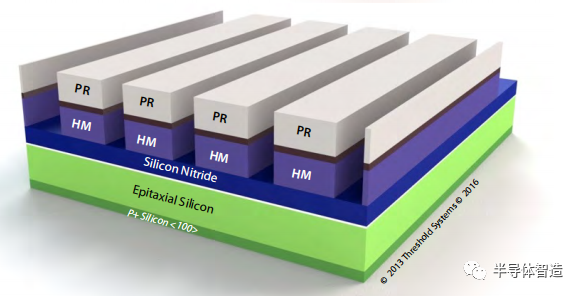

20.Hard Mask Etch & Photoresist Strip

通過高度各向異性的刻蝕過程,對非晶碳硬掩模進行刻蝕,刻蝕過程會停在非晶硅處,刻蝕完成后去掉PR。

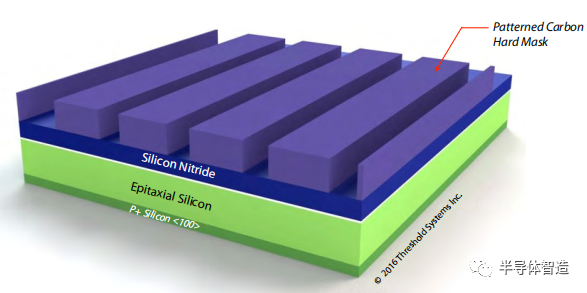

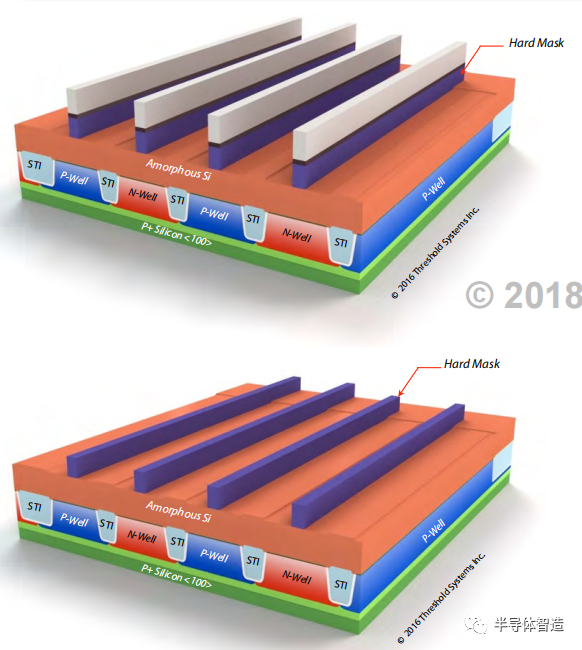

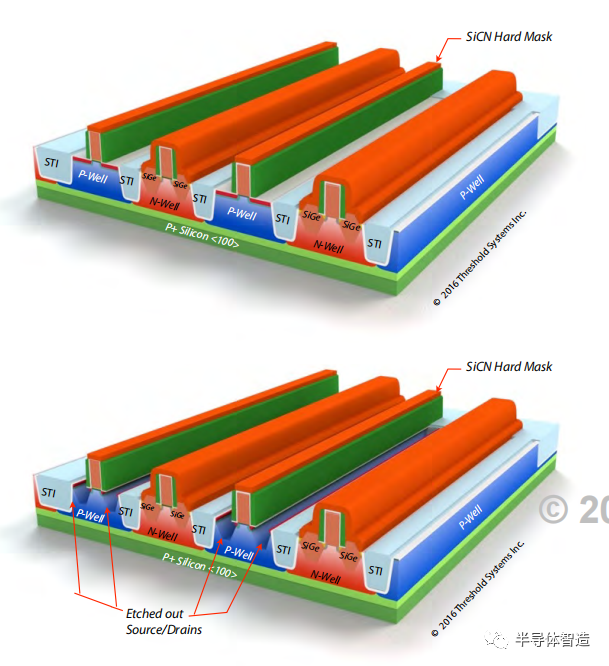

21.Amorphous Silicon Etch & Hard Mask Strip

然后使用高度各向異性的刻蝕recipe,將圖案從硬掩模轉(zhuǎn)移到非晶硅中。

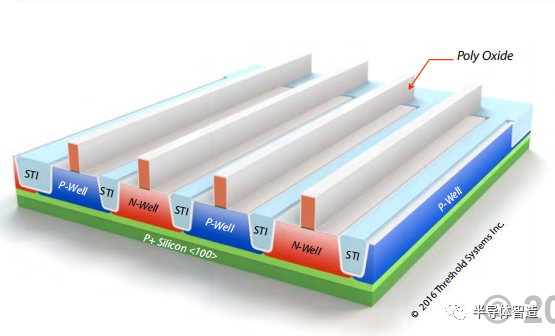

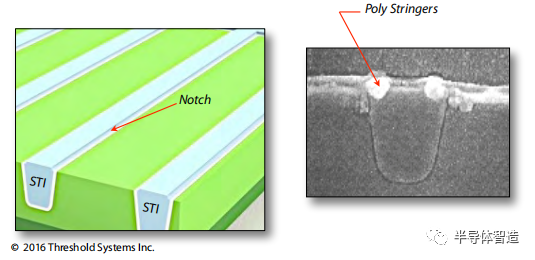

22.Poly Oxidation & Poly Stringers

首先生長出15 ? thermal poly oxide。隨后會沉積15 ?的CVD oxide)。這兩層氧化硅構成了所謂的“偏移間隔層”(Offset Spacer)(有時也稱為“Spacer0或Spacer1)。

最初的Pad氧化物去除(在填充溝槽和去除氮化物之后進行了幾個操作)優(yōu)先從溝槽角落處去除氧化物,從而在溝槽的兩側形成了沿著全程都存在的“凹槽”,有利于多晶硅線的形成。

多晶硅線在多晶硅刻蝕操作的最后階段形成。這個刻蝕過程的最后階段是高度選擇性的過刻,旨在去除源/漏區(qū)域和凹槽中剩余的少量多晶硅。如果這個刻蝕階段沒有經(jīng)過精心設計,厚的多晶硅線將留在溝槽凹槽中,并形成意外的導電通路,導致相鄰晶體管短路。

因此,盡量減小凹槽的尺寸以便于輕松去除多晶硅線非常重要。

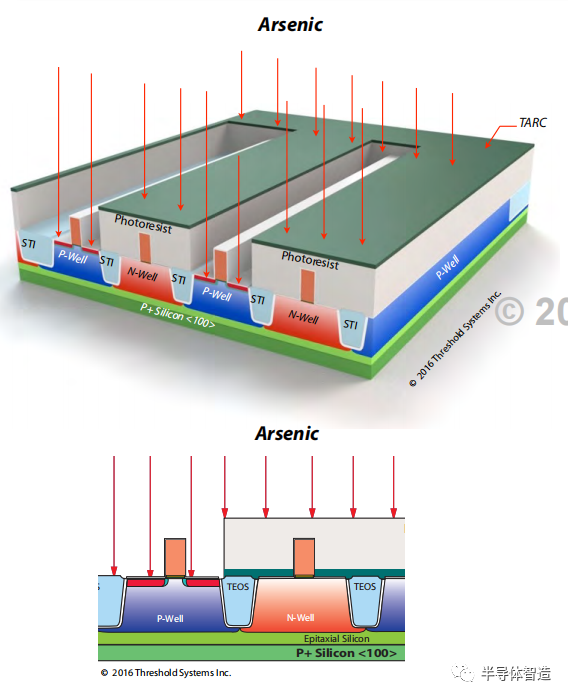

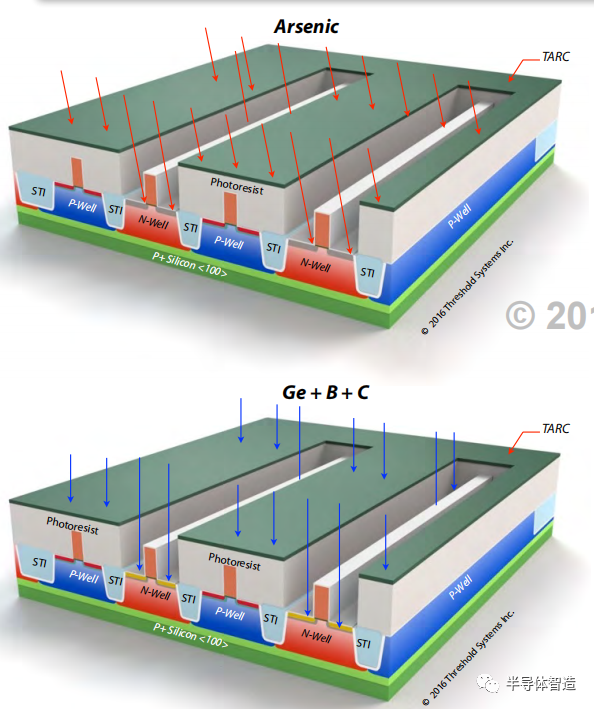

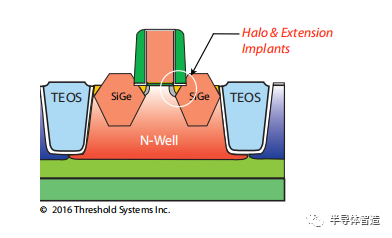

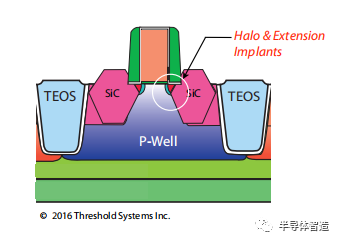

23.NMOS Halo Implant

對高閾值P-Well施加硼離子注入Halo注入的深度約為150-200 ?。

24.NMOS Extension Implant

將砷(Arsenic)延伸注入到P-Well區(qū)域。這個注入確定了NMOS晶體管的延伸注入。

延伸注入的深度與Halo注入大致相同(對于20納米器件大約為150-200 ?)。

25.NMOS Anneal & PMOS Halo

接下來,晶圓經(jīng)歷快速熱處理(約950攝氏度的瞬時峰值加熱1秒,然后以約1,350攝氏度的閃光退火1-3毫秒),以激活NMOS的延伸和Halo注入。在某些工藝流程中,閃光退火會被一個相同溫度(約1,350攝氏度)的部分熔融激光退火所取代。延伸注入的位置決定了NMOS晶體管的最終等效長度(Leff)。

退火過程使摻雜原子電活化,并退火修復了硅中在注入過程中產(chǎn)生的損傷。

26.PMOS Halo & Extension

同理,進行PMOS Halo處延伸注入,

對N-Well區(qū)域進行了鍺(Germanium)的預非晶華離子注入,然后施加低能量的Boron的延伸注入然后進行碳(Carbon)注入,以獲得更好的延伸注入剖面。

預非晶華離子注入限制了硼原子的通道化現(xiàn)象,而硼注入則確定了PMOS晶體管的延伸注入部分。

27.PMOS Anneal

先前工序中的光阻已經(jīng)被脫除。然后晶圓進入快速熱處理(約950攝氏度的瞬時溫度升高,持續(xù)約1秒,隨后進行約1,350攝氏度的快速退火處理,持續(xù)1-3毫秒),以激活PMOS擴散和外圍注入。在某些工藝流程中,閃光退火被以同樣溫度(約1,350攝氏度)的次熔激光退火所替代。擴散注入的位置決定了PMOS晶體管的最終有效通道長度(Leff)。退火過程使摻雜原子電性活化,并消除硅材料在注入過程中的損傷,對Idsat(飽和漏電流)有巨大影響。

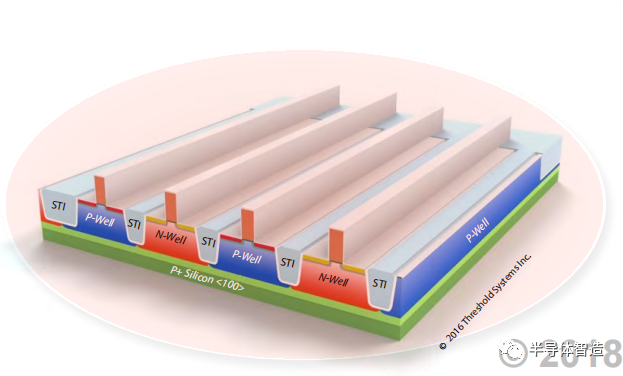

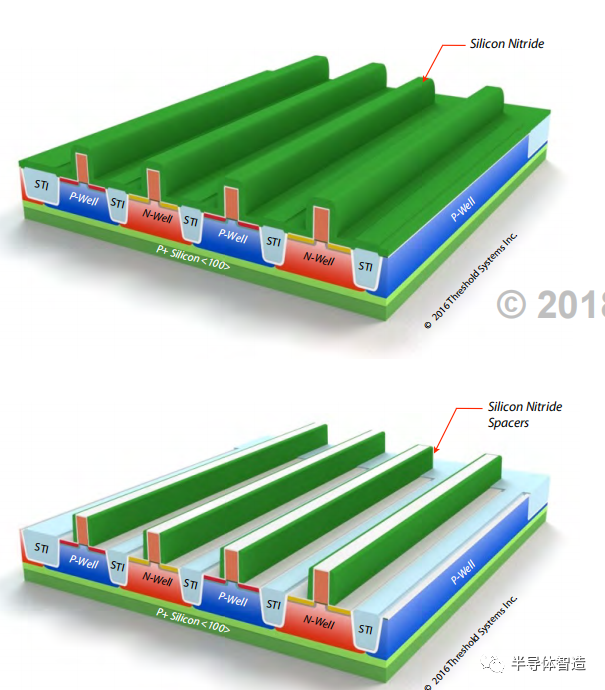

28.Nitride Spacer Deposition and Etch

在晶圓的表面上沉積了一個厚度為150 ?的均勻?qū)庸璧铩S捎诠璧锞哂辛己玫膹秃闲裕跂艠O的側壁處最厚。

經(jīng)過高度各向異性的腐蝕,所有水平表面上的硅氮化物被去除,但在柵極側面保留了硅氮化物側壁間隔物,因為這里的硅氮化物最厚。硅氮化物側壁間隔物在后續(xù)的接觸注入過程中起到微型注入掩膜的作用。

29.Nitride Spacer Etch

由于腐蝕過程高度各向異性(只朝一個方向進行腐蝕,即向下),所以除了柵極側壁上的硅氮化物之外,硅氮化物在其他地方都被清除掉了,因為柵極側壁上的硅氮化物是最厚的部分。

高度各向異性的腐蝕過程從所有水平表面去除了硅氮化物,但在柵極側面保留了硅氮化物側壁間隔物。這些硅氮化物側壁間隔物在后續(xù)的接觸注入過程中充當微小的注入屏蔽層。

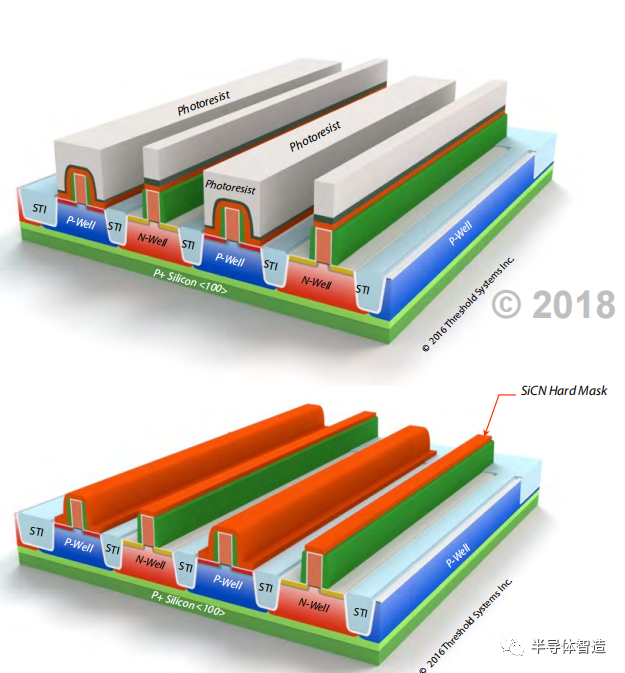

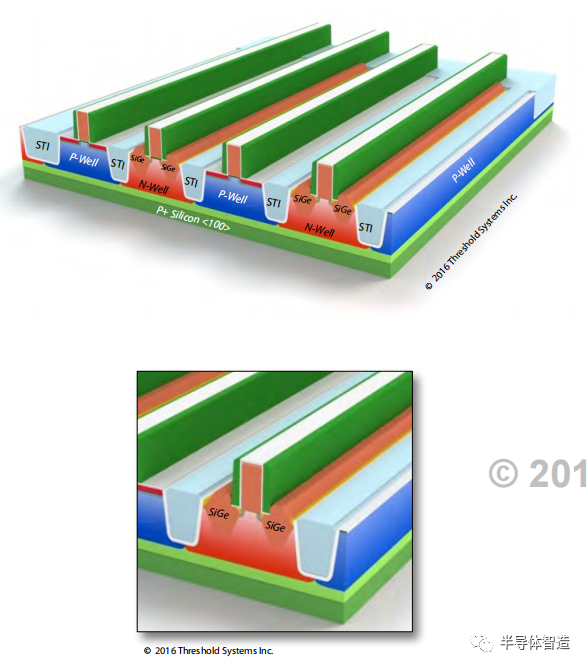

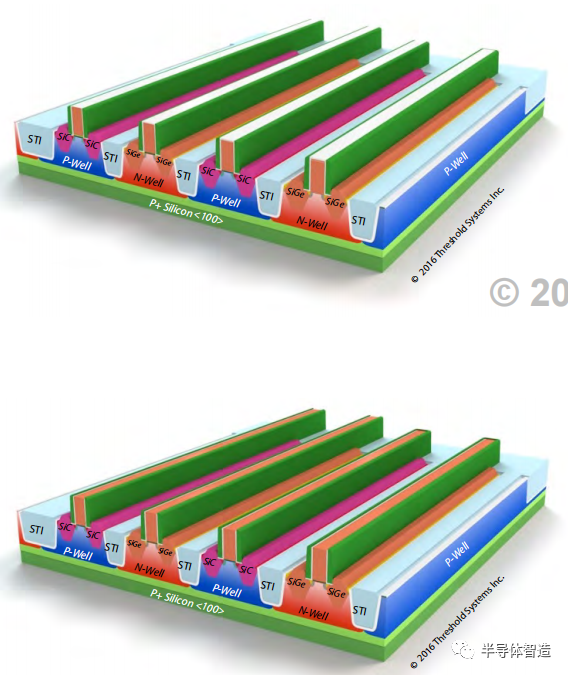

30.PMOS Hard Mask Deposition & Patterning

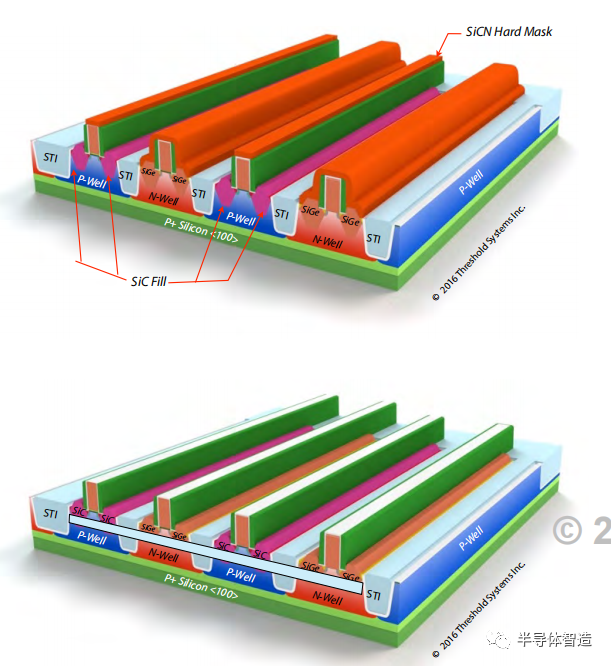

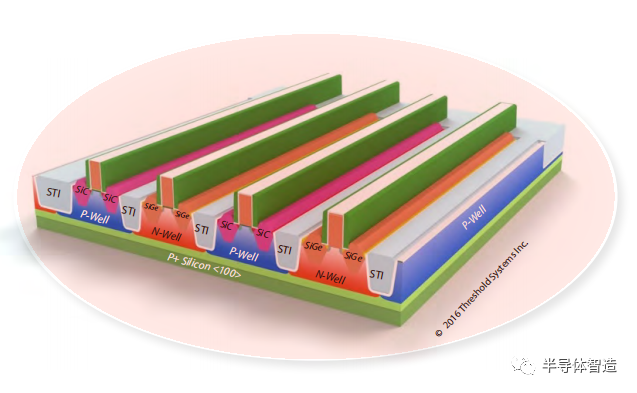

接下來,在晶圓的表面上沉積300?的SiCN。

31.PMOS Hard Mask Etch & Photoresist Strip

32.PMOS Source/Drain Etch & SiGe Fill

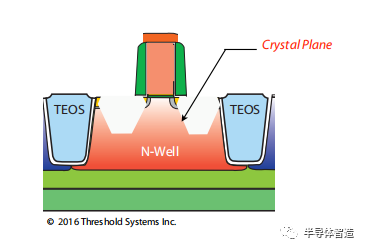

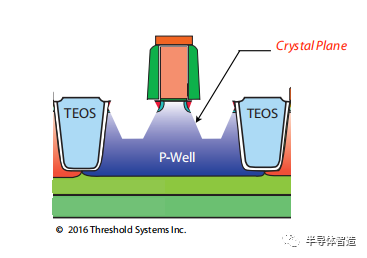

使用NH4OH溶液對PMOS晶體管的暴露源/漏區(qū)進行濕腐蝕,該溶液能夠沿著晶體學平面進行腐蝕。P-襯底和柵極由SiCN保護。腐蝕過程不會影響STI溝槽中的暴露氧化物。

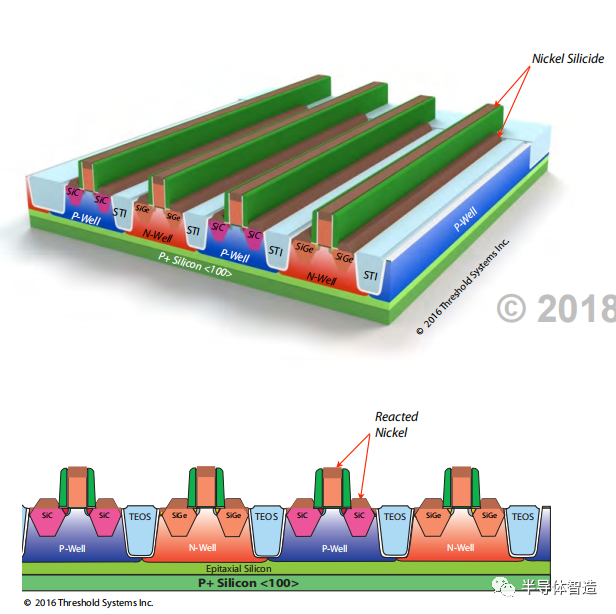

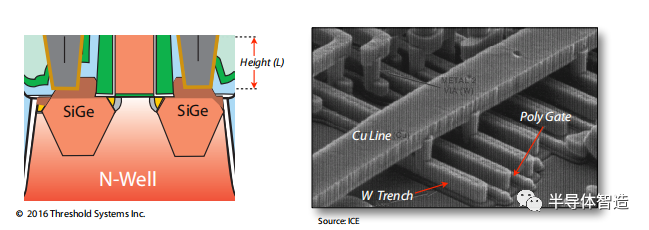

然后,晶圓會經(jīng)過選擇性外延沉積SiGe。SiGe只能在暴露的硅表面上成核,這意味著它只會形成在PMOS的源/漏區(qū)域(晶圓的其他部分由氮化物或氧化物構成,或者覆蓋有SiCN)。SiGe的Ge含量約為40%,它會對PMOS通道施加高度壓縮應變,極大地提高通道內(nèi)電洞的遷移率,從而增加Idsat。

隨著外延SiGe的沉積,它會摻雜大量的硼,使其成為P型硅。

33.Hard Mask Strip

剩余的SiCN硬膜會在各向同性腐蝕中被去除。下圖顯示了PMOS器件的SiGe替代源/漏區(qū)的近距離視圖。請注意,盡管源/漏區(qū)已被替換,但擴展和晶團注入仍然存在。

34.NMOS Hard Mask Deposition & Patterning

接下來,將在晶圓表面上沉積300?的SiCN薄膜。

35.NMOS Hard Mask Etch + Source/Drain Etch

使用HF濕腐蝕劑去除源/漏區(qū)上的氧化物。然后,使用NH4OH溶液進行濕腐蝕,該溶液會沿著晶體學面去除PMOS晶體管的暴露的源/漏區(qū)。

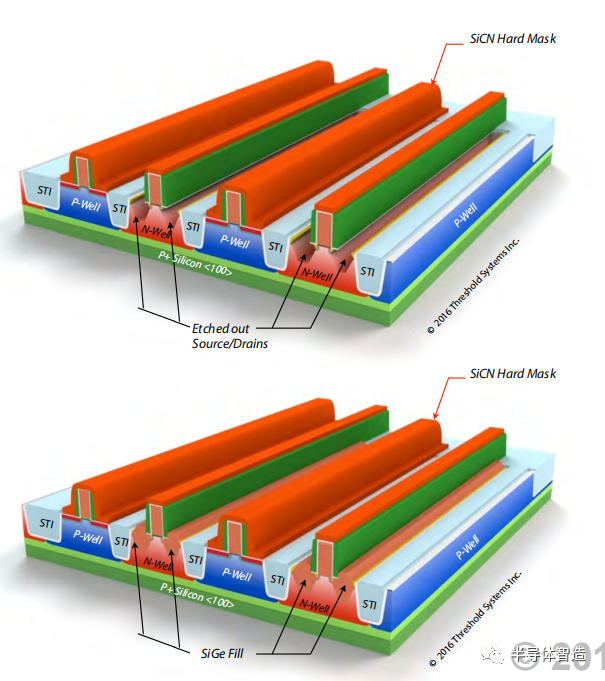

36.NMOS Source/Drain Selective SiC Dep

然后,晶圓會經(jīng)過選擇性外延沉積SiC的過程。SiC只會在暴露的硅表面上形成晶核,這意味著它只會在PMOS源/漏區(qū)域形成(晶圓的其他部分由氮化物或氧化物組成,或者覆蓋有SiCN)。SiC對NMOS溝道施加非常強的拉應力,并增加電子的遷移率。這增加了NMOS器件的Idsat。隨著SiC的沉積,它會被磷摻雜以使其成為N型材料。

適當施加應變到晶體管通道,可以顯著增加晶體管的驅(qū)動電流,從而提高晶體管的速度。為了實現(xiàn)這一效果,PMOS晶體管通道必須處于壓應變狀態(tài),而NMOS晶體管的通道則處于拉應變狀態(tài)。有多種方法可以在晶體管通道中引入壓應變或拉應變,但最有效的方法是用摻有具有較大或較小晶格常數(shù)的原子的硅外延替換晶體管的源/漏區(qū)。這分別引入了壓應變或拉應變。如先前提到的,在每個新節(jié)點中,PMOS SiGe源/漏區(qū)的Ge含量增加,以保持對晶體管通道的壓應力(目前在20nm節(jié)點上為55%的Ge含量)。另一種技術是將SiGe晶體的尖銳邊緣靠近通道,以引發(fā)更多應力。這在32nm節(jié)點上已經(jīng)實施。

適當施加應變到晶體管通道,可以顯著增加晶體管的驅(qū)動電流,從而提高晶體管的速度。為了實現(xiàn)這一效果,PMOS晶體管通道必須處于壓應變狀態(tài),而NMOS晶體管的通道則處于拉應變狀態(tài)。有多種方法可以在晶體管通道中引入壓應變或拉應變,但最有效的方法是用摻有具有較大或較小晶格常數(shù)的原子的硅外延替換晶體管的源/漏區(qū)。這分別引入了壓應變或拉應變。如先前提到的,在每個新節(jié)點中,PMOS SiGe源/漏區(qū)的Ge含量增加,以保持對晶體管通道的壓應力(目前在20nm節(jié)點上為55%的Ge含量)。另一種技術是將SiGe晶體的尖銳邊緣靠近通道,以引發(fā)更多應力。這在32nm節(jié)點上已經(jīng)實施。

替代柵極還提供了另一種增加PMOS應變的方法。當多晶硅柵極電極被去除時,腔隙層和相關結構向內(nèi)移動,壓縮晶體管通道并引發(fā)壓應力。

使用替代源/漏區(qū)方法給NMOS晶體管施加應變是相當棘手的,因為很難找到一個比硅具有更小晶格常數(shù)同時又具有高度穩(wěn)定性的材料。因此,通常會采用其他技術來實現(xiàn)NMOS的拉應變,而不是替代源/漏區(qū)。然而,最近已經(jīng)完善了一種技術,將磷或碳和磷摻入到硅外延中。由于碳比硅小38%,用這種外延替換源/漏區(qū)會在通道兩側產(chǎn)生拉應變,并在通道上形成拉應力。這正是增強晶體管性能所需的(驅(qū)動電流增加高達20%)。為了達到這個目的,可以使用磷或碳/磷外延。

NMOS器件上應力記憶技術(SMT)的一個更具體的名稱是“邊緣位錯應力”。這是一種通過SMT技術在NMOS通道中產(chǎn)生邊緣位錯并引發(fā)劇烈拉應力的技術。在P或P&C替代源/漏外延技術出現(xiàn)之前,這項技術首先應用于45/32納米節(jié)點的NMOS晶體管。該過程涉及進行深度非晶化注入,然后沉積一層氮化物應力覆蓋層。在進行快速熱退火以誘導SMT后,應力覆蓋層被去除,形成了邊緣位錯。SMT的初始預非晶化注入(PAI)在源/漏區(qū)域下形成多個邊緣位錯,增強了短通道遷移率。整體上,可實現(xiàn)10%的Idsat增加。需要注意的是,通常會同時使用不同的應變技術,因為它們對性能增強的貢獻是累加的。

37.Source /Drain Anneal

然后,晶圓將經(jīng)歷快速熱處理(約950攝氏度處理約持續(xù)1秒,隨后進行約1,350攝氏度的閃光退火處理持續(xù)1-3毫秒),以激活PMOS和NMOS的摻雜原子。

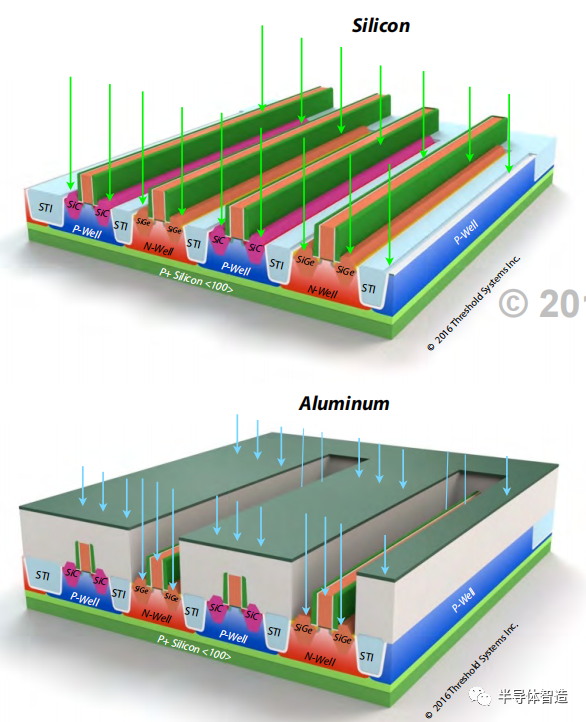

38.Nickel Salicidation Oxide Strip

退火后,晶圓上的柵極頂部仍然有一層氧化物。在SiGe和SiC源/漏區(qū)域上可能還存在著天然氧化物。這兩種氧化物必須被去除,以便為硅化處理暴露出裸露的硅表面。

然后,晶圓被浸泡在HF中,去除柵極頂部以及源/漏區(qū)域表面的所有二氧化硅。這個步驟準備晶圓進行接下來的硅化處理。

39.Salicidation Implants

晶圓接受了硅預非晶化注入(PAI)。這使得硅表面非晶化,并有助于形成更加均勻、電阻較低的硅化物(在接下來的操作中形成)

晶圓使用光刻膠進行圖案定義,僅暴露出P井。然后,使用鋁進行注入(。鋁的位置安排使其位于SiGe與尚未沉積的Ni/Pt之間的界面上。這種注入能夠降低PMOS器件的接觸電阻,因為鋁會分離到SiGe的頂部,并且由于是P型摻雜,它會將電子空穴的肖特基勢壘高度從約0.4電子伏降低到約0.12電子伏,同時提高驅(qū)動電流達19%。

40.Nickel/Platinum/TiN Deposition

晶圓經(jīng)過P/SC1清洗后,采用物理氣相沉積法在上面均勻涂覆約125 ?的鎳/鉑和約150 ?的鈦氮化物。鎳上覆蓋的鈦氮化物帽層有助于防止在高溫硅化過程中鎳的擴散,并促進更均勻的NiSi形成。5-10%的鉑有助于降低Ni-Si界面的勢壘并建立更低的接觸電阻。它還延遲了低電阻NiSi向較高電阻NiSi2的轉(zhuǎn)變。

2D圖像展示了在初始沉積之后及在退火之前的鎳/鉑/鈦氮化物層堆疊。

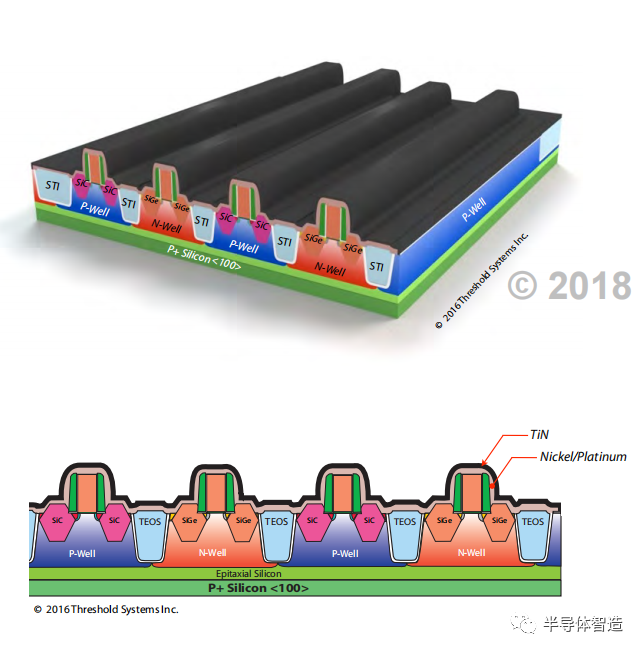

41.Salicidation Anneal

晶圓經(jīng)歷了大約250℃、30秒的快速熱退火(RTA),將鎳鉑轉(zhuǎn)變?yōu)楦唠娮璧腃49相。接著,進行了第二次約390℃、30秒的RTA,將晶圓表面的鎳轉(zhuǎn)變?yōu)榈碗娮瑁?5 μΩ-cm)的C54 NiSi相。

采用NiSi是因為它比相同厚度的CoSi2消耗至少30%的硅。這一點非常重要,因為20納米節(jié)點結深度非常淺。此外,NiSi具有非常光滑的表面,可以最小化結漏電。

2D圖像展示了器件上反應和未反應的鎳/鉑。為了形成鎳硅化物,鎳/鉑層必須與裸露的硅表面接觸。唯一有裸露硅的位置是在柵極的頂部或源/漏區(qū)域。位于STI(shallow trench isolation,淺溝槽隔離)和氮化物間隔層上的鎳/鉑將保持未反應狀態(tài)。

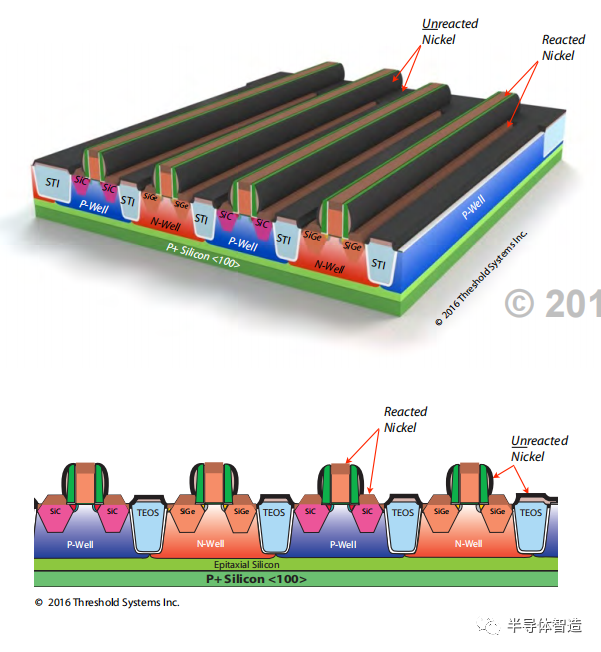

42.Unreacted Nickel Strip

位于間隔層側壁和STI上的未反應鎳會被SC1溶液刻蝕掉。這種刻蝕具有高選擇性,只保留在柵極頂部和源/漏區(qū)域上的已反應硅化物。這種刻蝕還會從晶片的所有表面上去除鈦氮化物覆蓋層。

2D圖像闡明了蝕刻溶劑能夠迅速攻擊并去除氮化物間隔層側壁和STI頂部上的未反應鎳/鉑。然而,蝕刻溶劑不會攻擊源/漏區(qū)域上的已反應鎳硅化物,也不會攻擊柵極頂部的已反應鎳硅化物。

Transistor Nomenclature

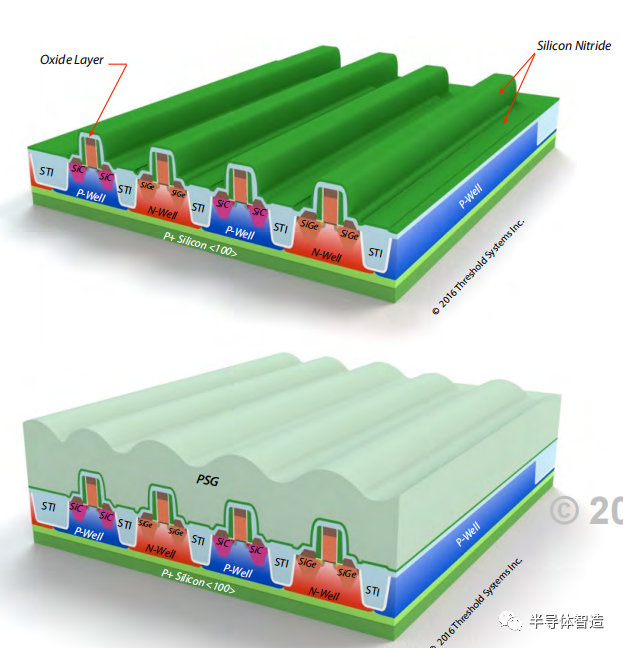

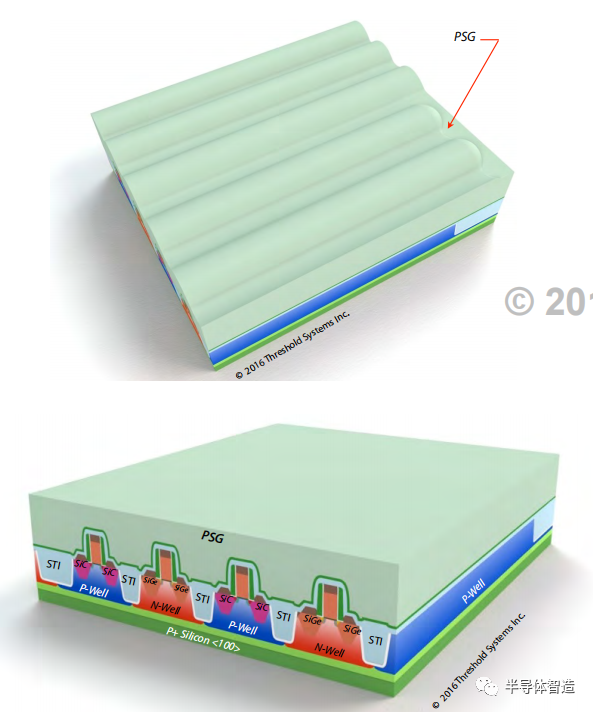

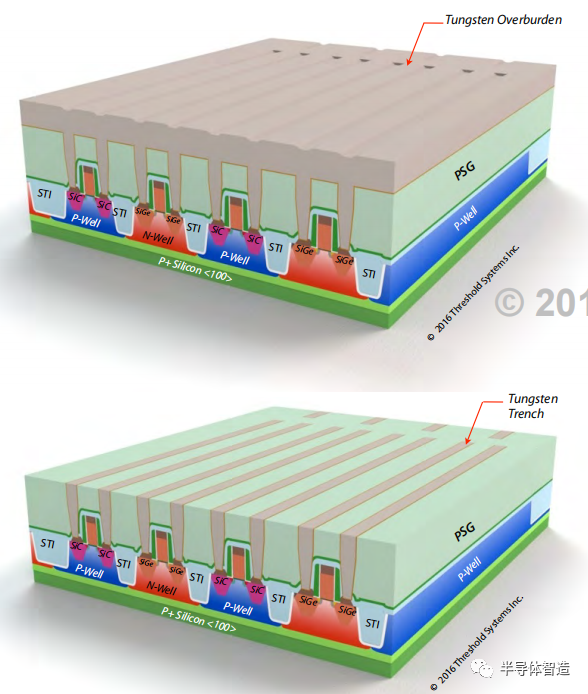

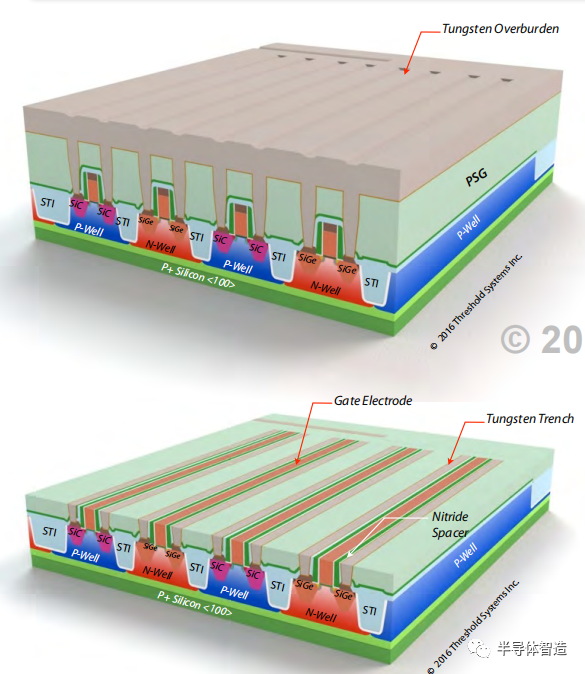

43.Pre-Metal Dielectric (PMD)

晶圓首先在P/SC1(一種清洗溶液)中進行清洗,然后沉積薄約75?的二氧化硅層,接著沉積約75?的氮化物層。氧化物作為擴散屏障,防止外部雜質(zhì)摻入器件層(即“活性”層)。

硅氮化物將作為蝕刻停止層,用于連接晶體管的源/漏區(qū)和柵極電極到尚未形成的鎢溝槽中的接觸刻蝕。

接下來,使用高密度化學氣相沉積(CVD)技術,在晶圓上沉積2,000 ?的磷摻雜玻璃,也稱為PSG(磷硅酸鹽玻璃)。這一層形成了前金屬介電層(Pre-Metal-Dielectric,PMD)。

44.Pre-Metal Dielectric Polish-Back

在拋光之前,觀察 PSG 層的自上而下視圖。請注意 PSG 中的凸起,這是由于柵極電極高度引起的底層地形。

使用CMP(化學機械拋光)將晶圓拋光至約1,200?的厚度。

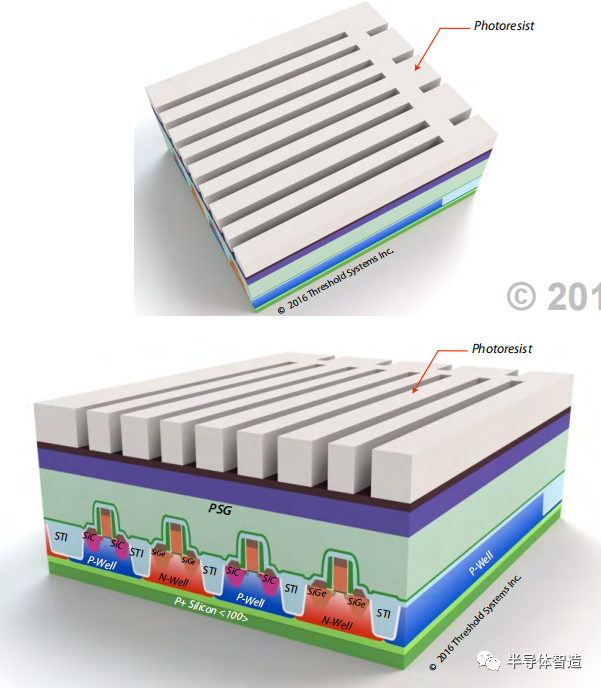

45.Hard Mask Patterning

接下來,晶圓涂覆光刻膠并進行圖案化處理。下面插圖是溝槽接觸光刻膠圖案的自上而下視圖。請注意圖像右側的柵極電極接觸溝槽。

這將是一個雙重圖案化操作過程。

46.Hard Mask Etch & Photoresist Strip

光刻膠被氧化灰化以去除,留下圖案化的非晶碳硬膜。然后,晶圓在蝕刻溶液中進行清洗,以去除任何殘留的光刻膠

利用非晶碳硬膜作為模板,進行高度各向異性刻蝕,穿過PSG層形成接觸孔。刻蝕在源/漏區(qū)域上方的硅氮化物和柵極頂部停止。然后改變刻蝕化學組分,對硅氮化物和底層氧化物進行蝕刻。刻蝕在源/漏區(qū)域上方的鎳硅化物和柵極頂部停止。

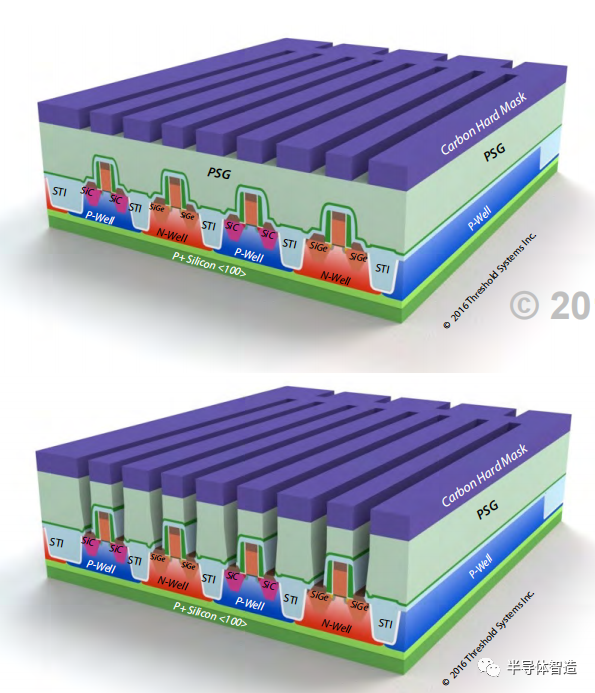

47.Hard Mask Strip & TiN Deposition

接下來,通過離子金屬等離子體物理氣相沉積(IMP PVD)沉積約60?的鈦(一層膠黏層)。隨后通過IMP PVD沉積約30?的鈦氮化物(一層屏蔽層)。在沉積后,鈦氮化物進行重新濺射,以增強接觸孔內(nèi)的側壁覆蓋。

晶圓隨后在RTA中加熱,使鈦/鈦氮化物發(fā)生反應并設置膠黏層的電阻。

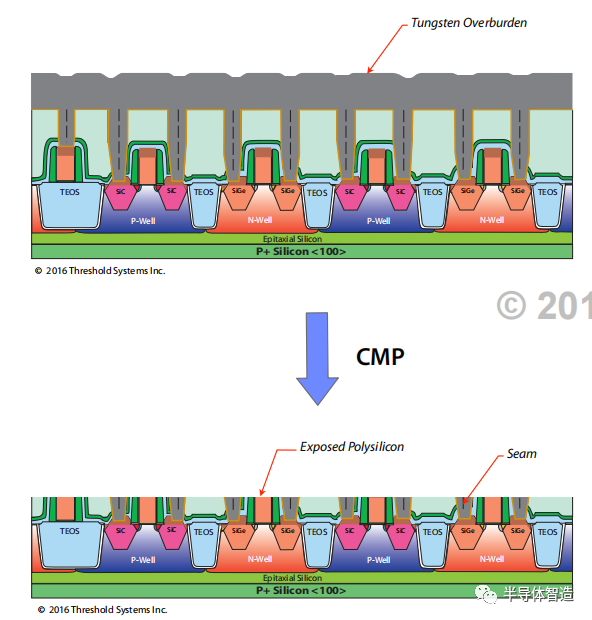

48.Tungsten Deposition & Polish-Back

接下來,沉積一層鎢種子層,襯里接觸孔的內(nèi)壁,并確保對整個鎢沉積層進行均勻覆蓋。

最后,通過化學氣相沉積(CVD)沉積約2,500?的鎢。

晶圓再次通過CMP工藝進行拋光。在這個過程中,去除多余的鎢層,并將鎢溝槽拋光至PSG層的頂部。

接下來,進行氧化緩沖處理,以使PSG氧化物表面光滑,并確保PSG表面與鎢溝槽頂部共面。

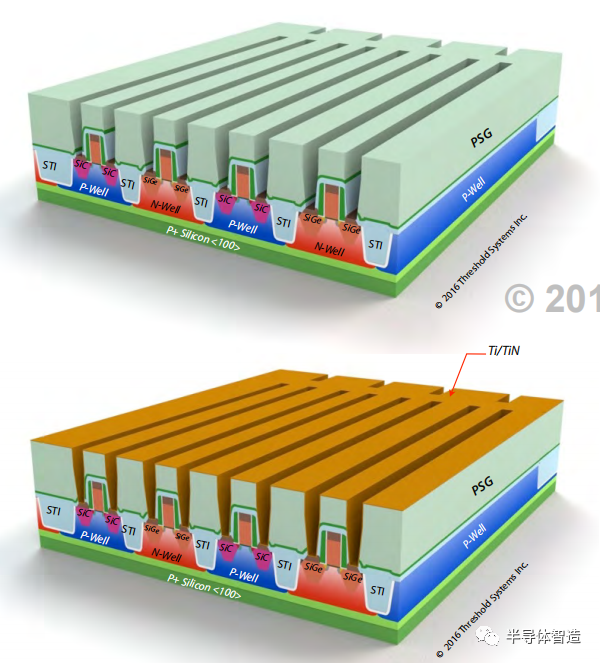

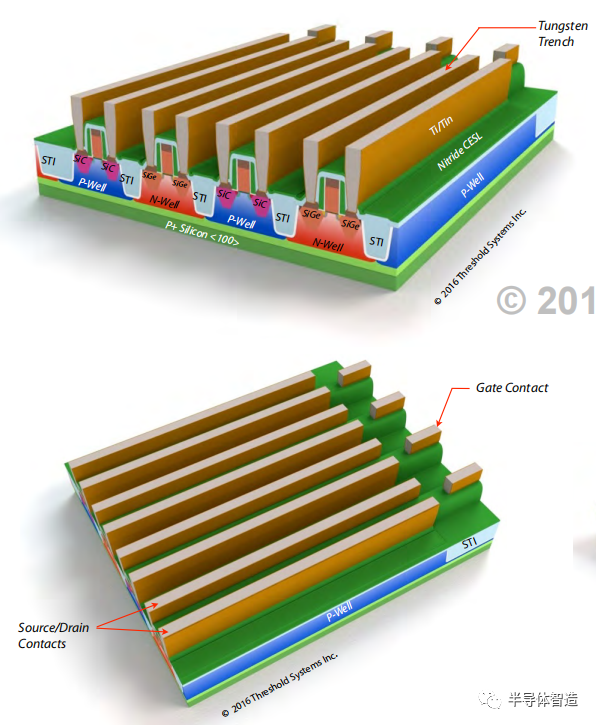

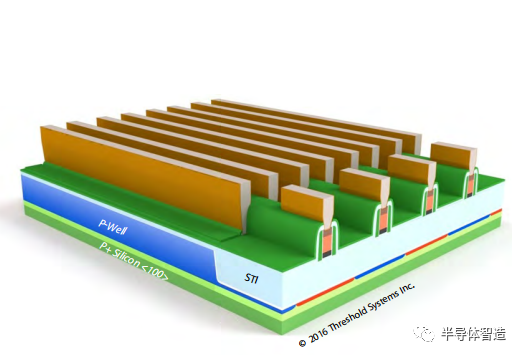

49.Trench Contacts (Alternate Scheme)

圖示展示了如果去除PSG氧化物,鎢溝槽將會呈現(xiàn)的樣子。清晰可見的是鎢溝槽,上覆有Ti/TiN,與源漏區(qū)域和柵極電極進行電接觸。

當然,這些視圖在實際生產(chǎn)設備中是不可見的。

Plug Polish Back/Tungsten Trenches

將鎢填充物拋光至與柵極頂部共面的操作是一項新的技術,首次在32納米工藝節(jié)點引入。較短的鎢填充物具有較低的接觸電阻。這一特性與NMOS和PMOS晶體管的抬高源漏區(qū)域結合,確保接觸電阻保持在可接受的范圍內(nèi)。

完全消除鎢填充物并采用銅填充物是困難的,因為將銅帶入源漏區(qū)域會帶來極高的風險。

50.Plug Polish Back

拋光回退的填充物最初的形成方式與標準填充物相同。在沉積Ti/TiN屏障金屬后,再沉積一層鎢種子層,然后進行2,500?的鎢的CVD沉積。

隨后,將過剩的鎢層拋光回退,直到填充物變得非常短,與柵極頂部共面。

51.Polished Back Trench Contacts

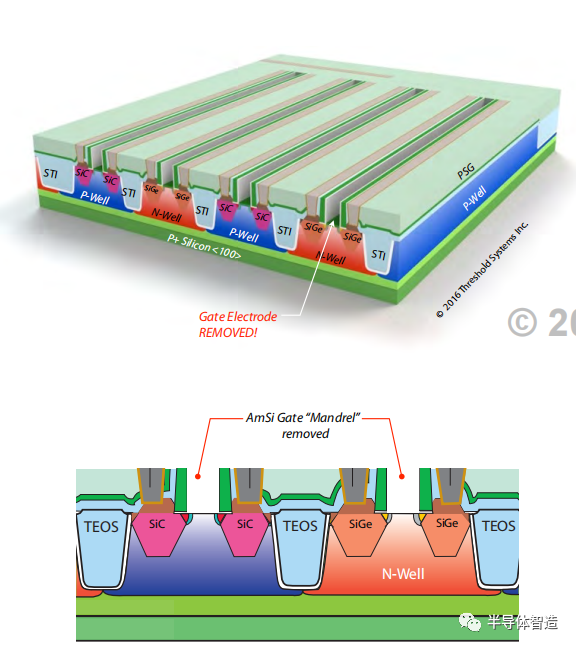

52.Gate Electrode Removal

柵極電極的去除:

一旦柵極頂部被打開,摻雜的非晶硅柵骨架將被刻蝕去除。因此,柵極電極被稱為"犧牲電極"。它的唯一目的是作為一個占位符,通常被稱為"骨架"。

這次刻蝕還會去除在柵腔壁上生長的氧化物偏移間隔層,以及柵腔底部的氧化物刻蝕停止層。

柵極骨架的去除:

下圖顯示了在CMP拋光打開柵極頂部和刻蝕掉犧牲性非晶硅柵骨架后的CMOS結構的橫截面圖。

這次刻蝕還會去除在柵腔壁上生長的氧化物偏移間隔層,以及柵腔底部的氧化物刻蝕停止層。

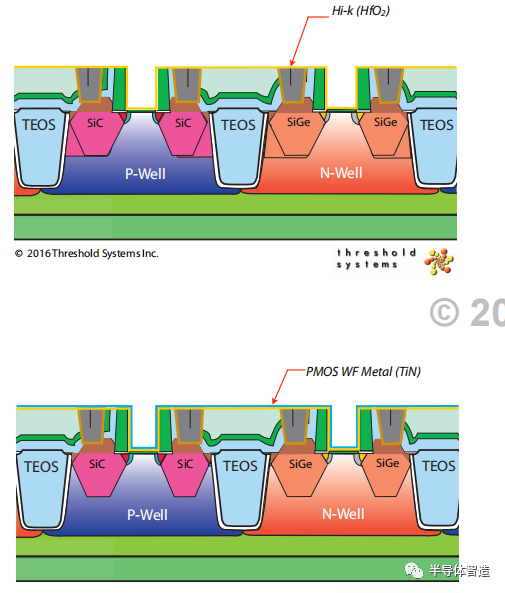

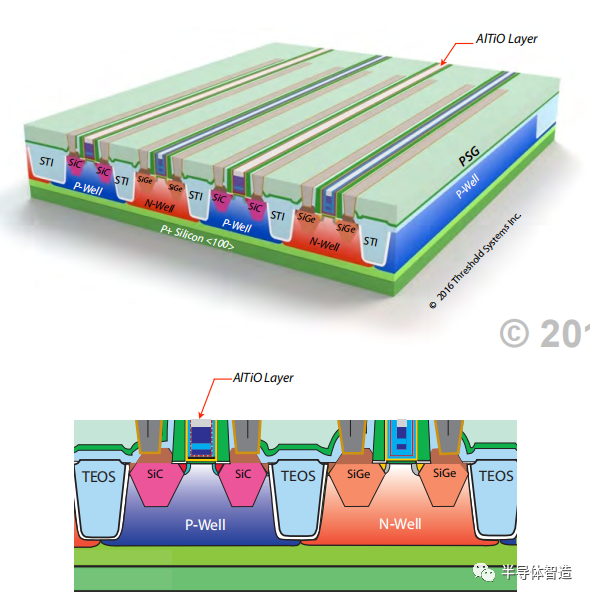

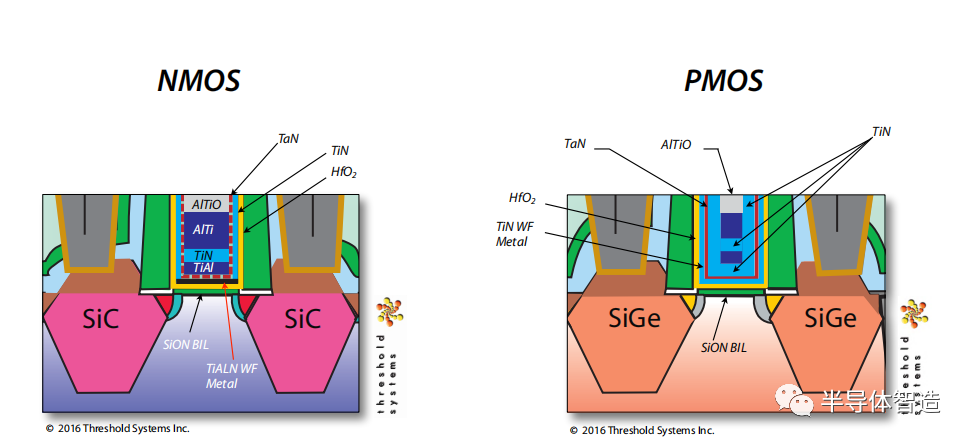

53.Hi-K Dielectric & PMOS WF Metal Deposition

高介電常數(shù)材料的沉積:

接下來,使用原子層沉積(ALD)技術沉積一層約18埃厚的氧化鉿(HfO2)薄膜。

PMOS WF金屬沉積:

接下來,使用物理氣相沉積(PVD)技術沉積薄的PMOS金屬柵電極。

它由薄的2.0納米鈦氮化物(TiN)層通過PVD沉積而成。這是PMOS工作函數(shù)(WF)金屬。它是一層填充PMOS和NMOS腔隙并包覆在晶圓表面的鈦氮化物。

在沉積后,再次進行噴濺,以確保柵腔內(nèi)側壁獲得良好的覆蓋。

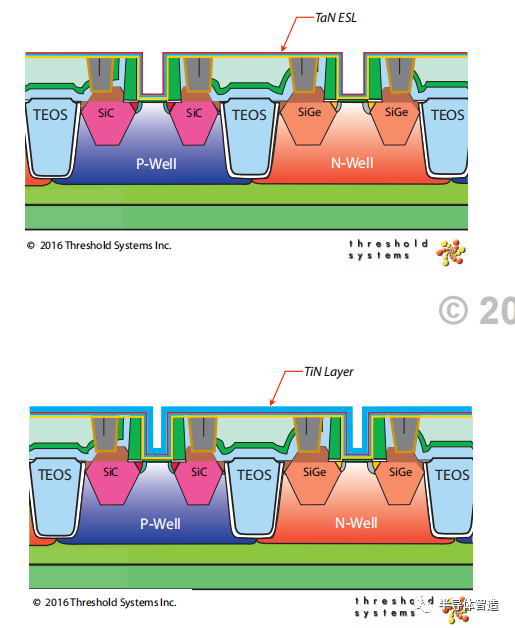

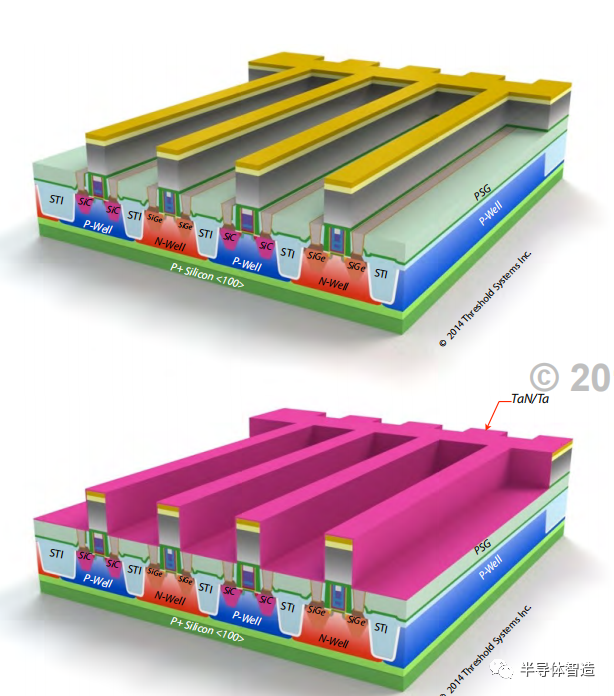

54.TaN & TiN Metal Deposition

TaN刻蝕停止層的沉積:

使用物理氣相沉積(PVD)技術沉積約1.0納米厚的TaN層。這層將作為刻蝕停止層(ESL)使用。

TiN層的沉積:

使用物理氣相沉積(PVD)技術沉積約5.0納米厚的TiN層。這是柵極堆棧中的第一層補充金屬,為柵極堆棧底部提供應變和電接觸。

對TiN進行再濺射以確保柵腔內(nèi)側壁得到良好的覆蓋。

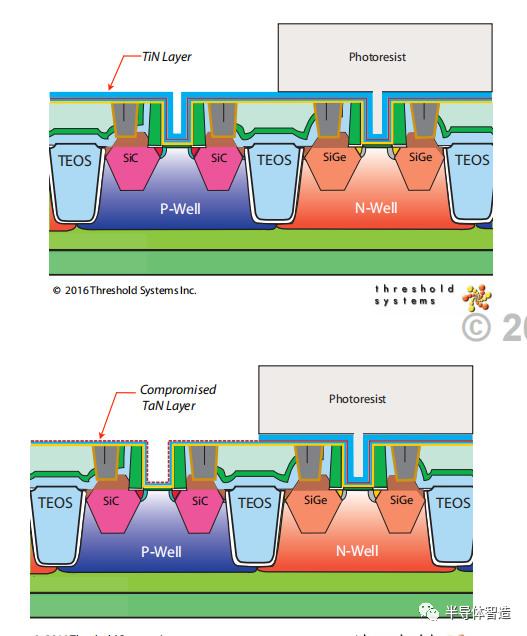

55.PMOS Metal Patterning & Etch

TiN層的光刻膠圖案形成:

先進行光刻膠的涂布和圖案形成。它僅保護PMOS區(qū)域,并暴露出NMOS區(qū)域上的TiN層。

TiN層的刻蝕:

暴露的TiN層被刻蝕去除。TaN層作為刻蝕停止層,阻止了該刻蝕過程。如上所示,非常薄的(<10?)TaN層的完整性會受到刻蝕過程的損害。

TaN層的完整性被損害是有益的,因為在后續(xù)的過程中,在NMOS晶體管的底層TiN層中擴散鋁,以形成NMOS TiAlN工作函數(shù)金屬。

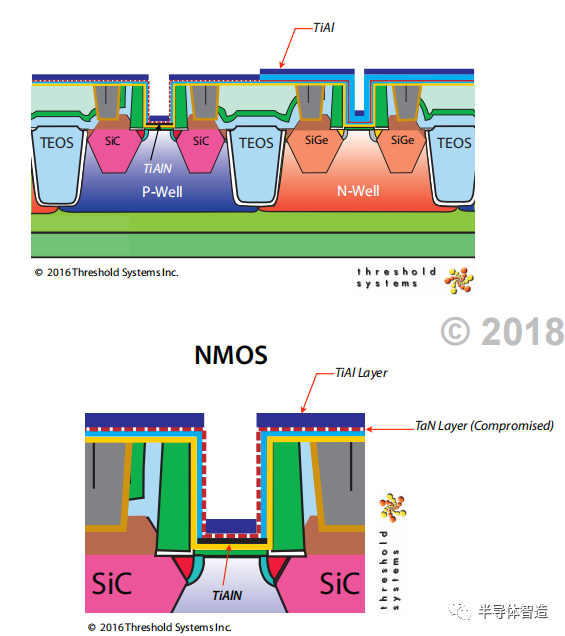

56.Photoresist Strip & TiAl Deposition

去除光刻膠并清潔晶圓。

TiAl層的沉積:

使用物理氣相沉積(PVD)技術沉積4.8納米薄的鈦鋁層。PVD過程被調(diào)整為僅在水平表面沉積(這很容易實現(xiàn),因為必須對PVD過程進行微調(diào)才能在垂直表面沉積)。

57.TiAl Anneal & NMOS WF Metal Formation

退火處理:

隨后進行退火處理,使得僅在NMOS區(qū)域中的TiAl中的鋁元素通過TaN屏障進行擴散。這將在Hi-k介質(zhì)上形成位于頂部的TiAlN NMOS工作函數(shù)金屬。

退火處理:

引發(fā)TiAlN工作函數(shù)金屬形成的退火處理在400oC以下的溫度下進行。在這個溫度下,鋁的擴散性很強,并且由于在NMOS器件中將其與底層TiN隔離的TaN之前受到損害(它被用作蝕刻停止層),鋁自由地擴散到TiN并形成所需的TiAlN,即NMOS工作函數(shù)金屬。

58.TiAl Backfifill Deposition

退火處理:

在形成NMOS工作函數(shù)金屬的退火處理過程中,厚的覆蓋層TiN層(在NMOS晶體管中不存在)和未經(jīng)損害的TaN層阻止鋁元素擴散到TiN PMOS工作函數(shù)金屬中。因此,TiN PMOS工作函數(shù)金屬不會變成TiAlN,而是保持為所需的TiN。

AlTi層的沉積:

通過物理氣相沉積(PVD)沉積兩層較厚的鋁鈦層(11.0納米+7.0納米)。PVD過程被調(diào)整為只在水平表面上進行沉積。

這種金屬層作為從柵極頂部到底部的電接觸。

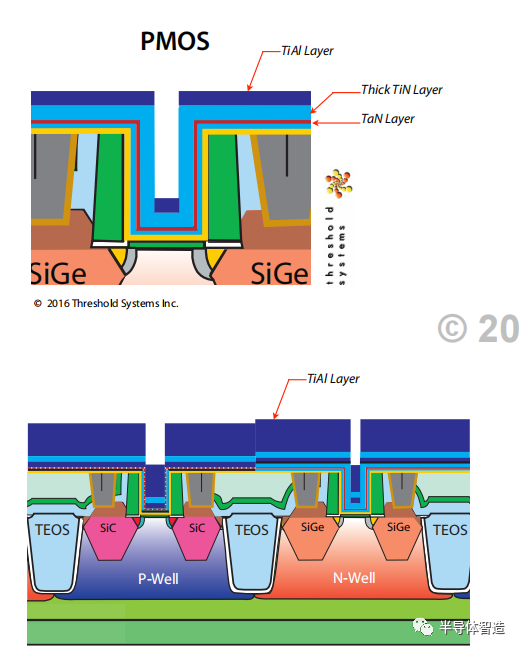

59.Metal Polish-Back

CMP拋光:

通過化學機械拋光(CMP),對金屬層進行拋光,使其與晶體管柵極的頂部平齊。

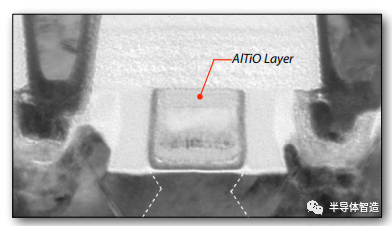

在CMP過程中,AlTi的最上層被氧化形成AlTiO。

Replacement Gate Anatomy

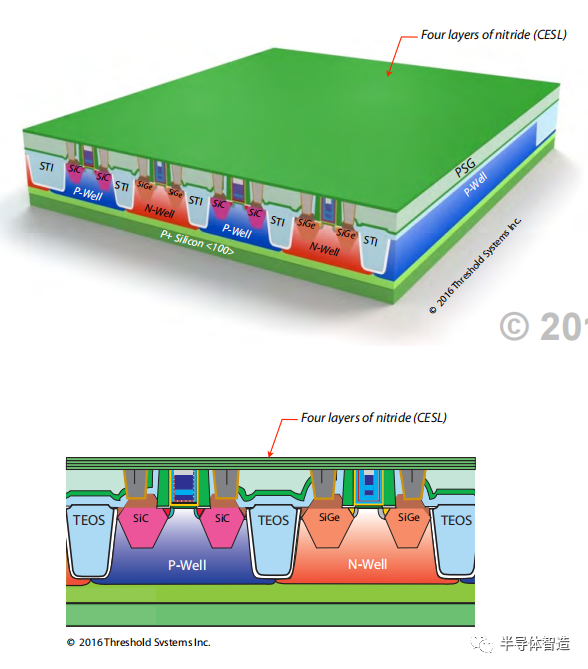

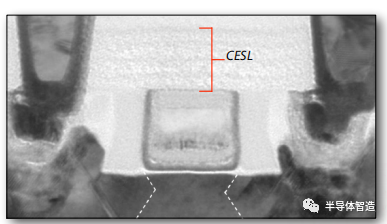

60.Nitride CESL Deposition

接觸刻蝕停止層(CESL):

接下來,在晶圓表面沉積幾層硅氮化物。這將密封晶體管的頂部,并作為接下來制造的接觸溝槽的刻蝕停止層。

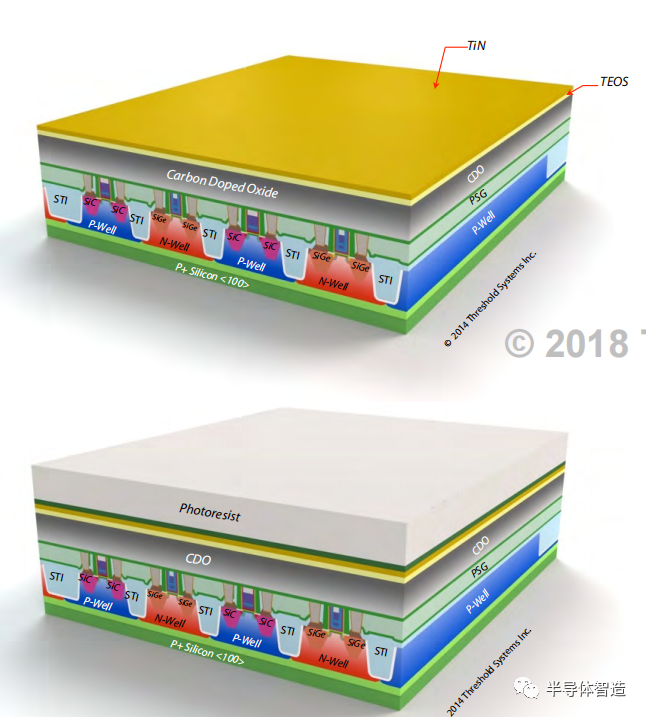

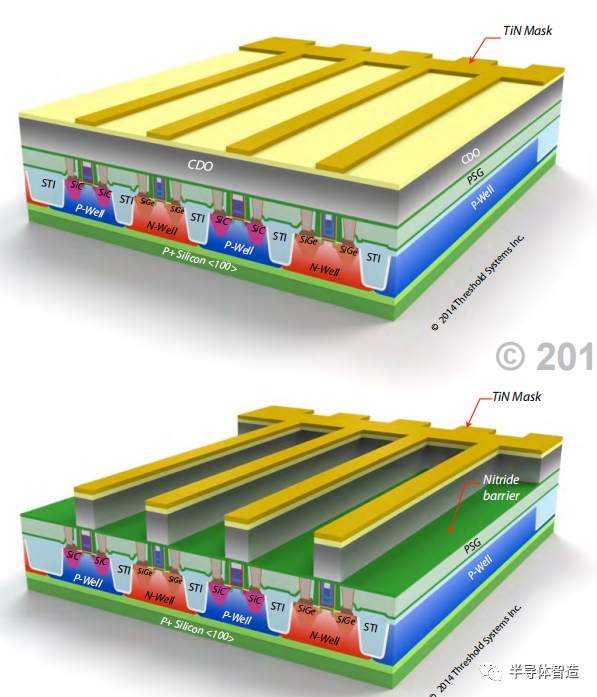

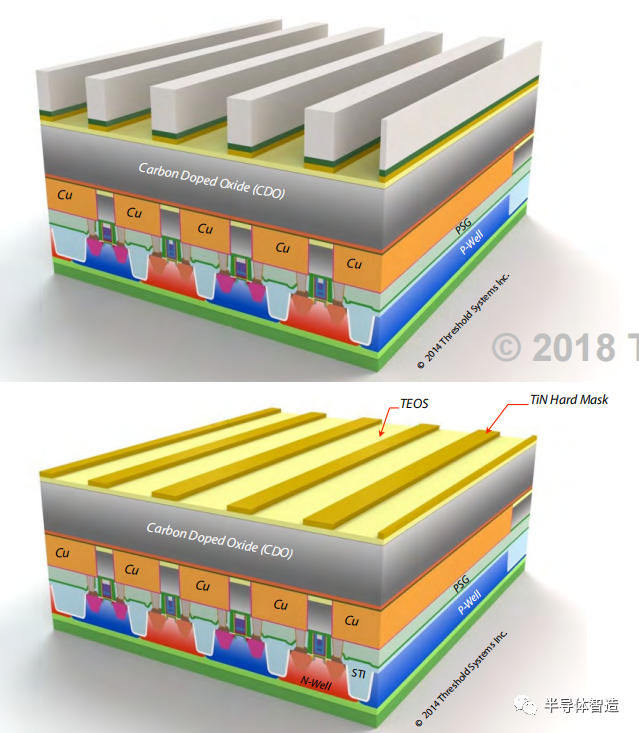

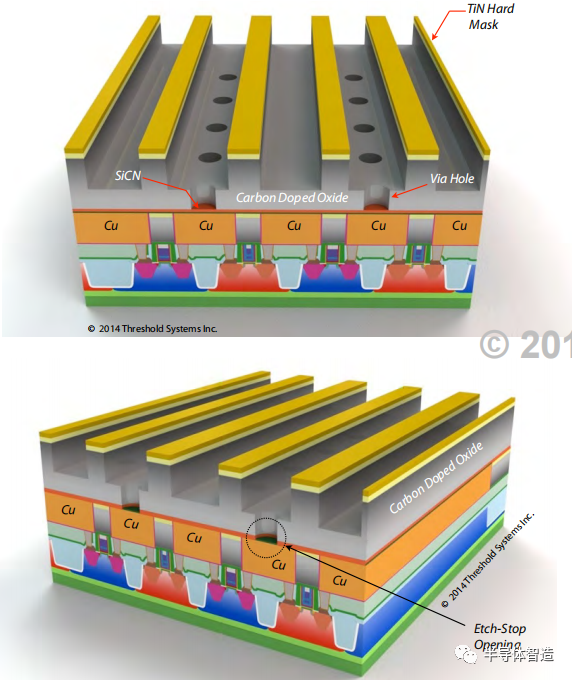

61.CDO/TEOS/ TiN Deposition

第一層互連電介質(zhì)(ILD)被沉積。它由約1,000?的摻碳氧化物(CDO)層組成,在沉積后進行紫外固化以去除多孔劑并降低其介電常數(shù)。

接著沉積一個400?的TEOS CMP停止層,然后是一個300?的鈦氮(TiN)硬面模,接下來進行曝光顯影。

62.TiN Hard Mask Patterning & Etch

然后對TiN硬掩模部分進行刻蝕。刻蝕停止在TEOS層上。

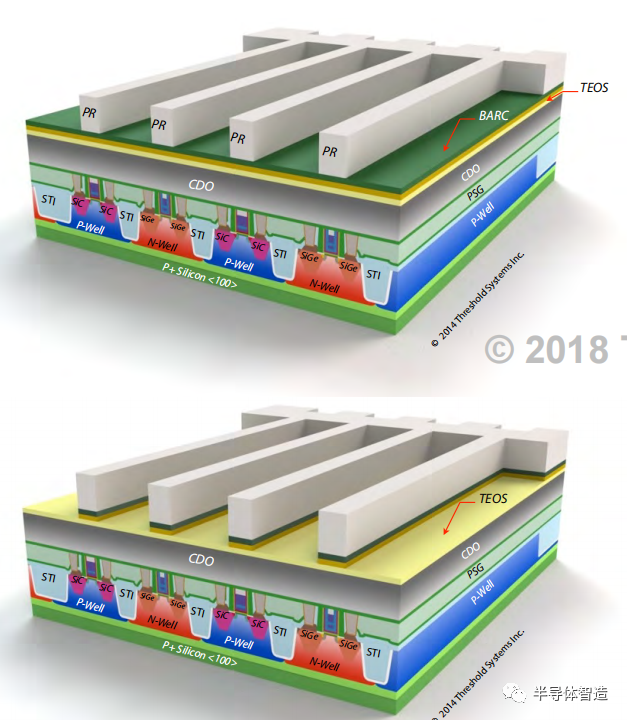

63.Photoresist Strip & Metal-1 Trench Etch

利用TiN作為模板,進行高度各向異性刻蝕,穿過TEOS和CDO層,定義金屬1(Metal-1)的溝槽。刻蝕停止在硅氮(SiN)蝕刻阻擋層上。

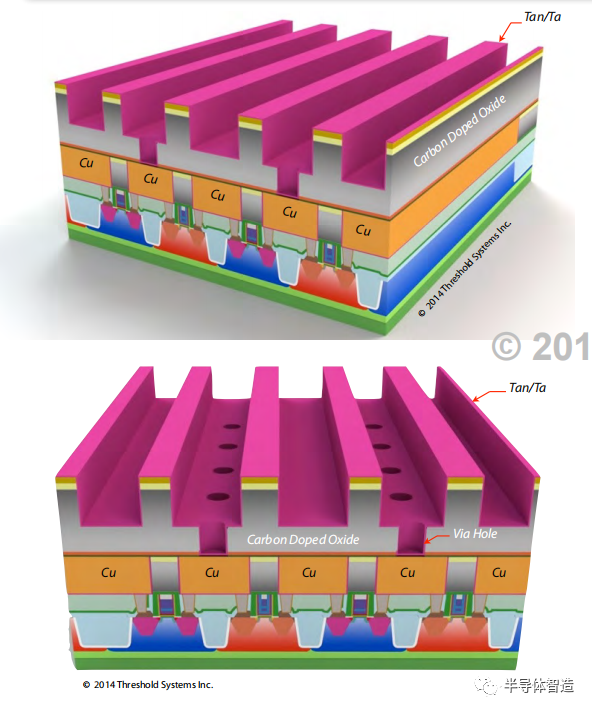

64.Nitride Barrier Opening TaN/Ta Deposition

然后繼續(xù)刻蝕打開溝槽底部的SiN刻蝕阻擋層。接下來,采用IMP PVD工藝沉積80 ?的鉭氮(TaN)層,然后是30 ?的鉭(Ta)層。這兩種金屬作為屏障,將尚未沉積的銅限制在溝槽內(nèi)。在鉭和鉭氮操作之后,進行重新濺射步驟,以確保良好的側壁覆蓋。

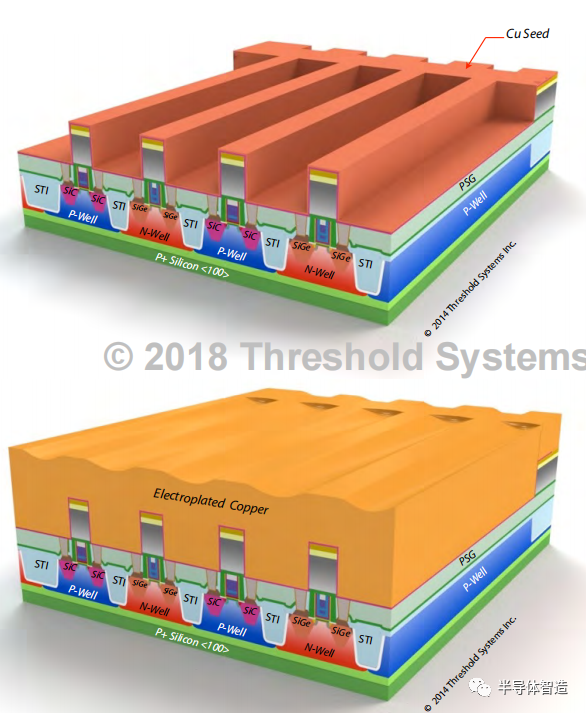

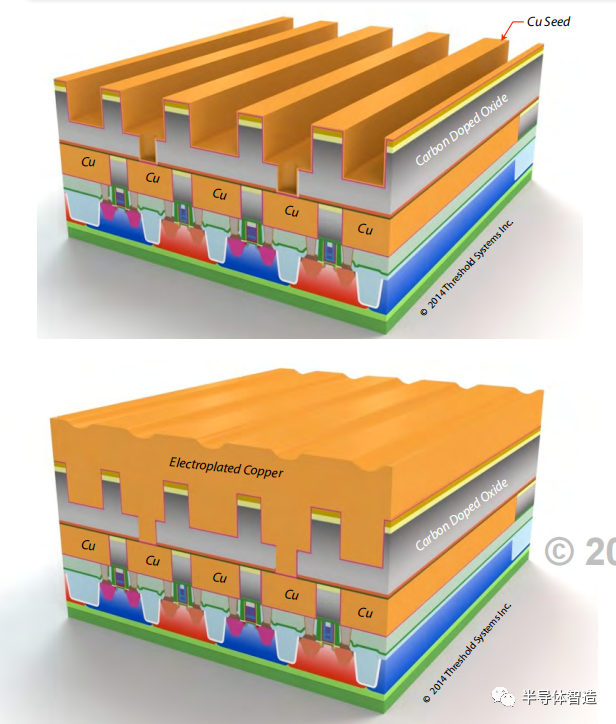

65.Copper Seed & Copper Bulk Deposition

在不破壞真空狀態(tài)下,沉積了300?的銅種子層,覆蓋了晶圓的整個表面,包括溝槽的內(nèi)部。

銅種子層的存在是為了確保均勻、無空洞的大面積銅沉積,并且是電鍍過程的必要前提條件。

接下來,采用電化學沉積方法,在其上沉積了6,000 ?的大量銅。

在沉積完成后,使用形成氣體(forming gas)將銅退火,在300oC的溫度下保持90秒,以定型其晶粒結構并降低其電阻。

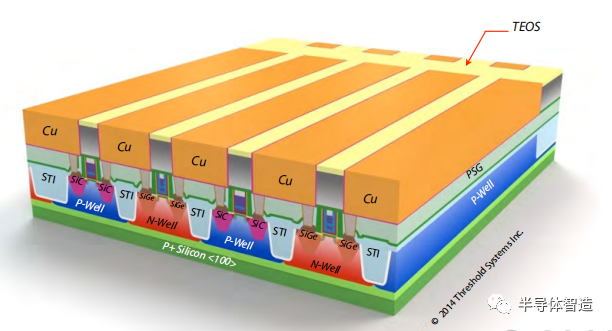

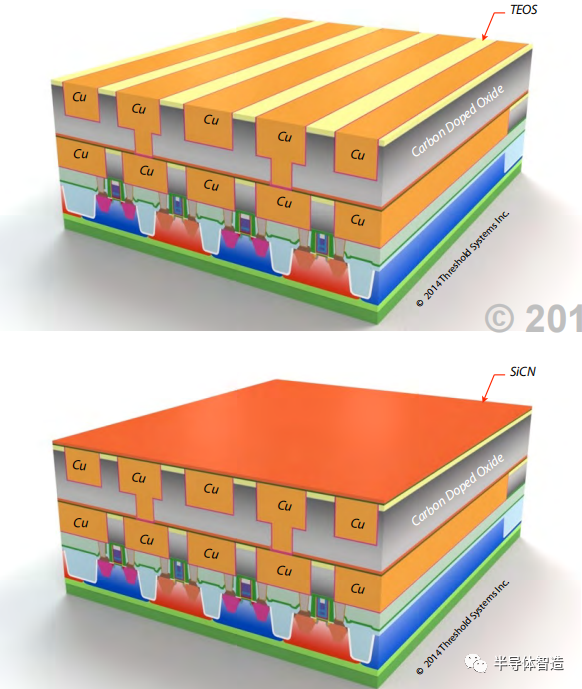

66.Copper-Ta/TaN-TEOS CMP

使用CMP(化學機械拋光)將銅拋光回去。這個拋光過程也會去除TEOS表面上的鉭。較軟的TEOS作為CMP過程的拋光停止層。

接下來,進行氧化物拋光操作,以平滑TEOS氧化物的表面,并確保TEOS表面與銅線頂部在同一平面上。

在每次CMP操作之后,對晶圓進行清潔處理。

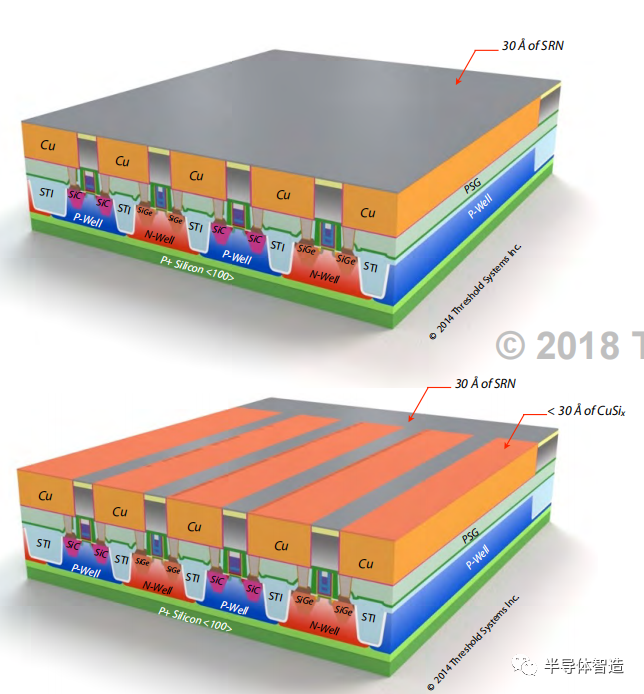

67.Copper Sealing

在晶圓上沉積了一個薄的30?的富硅氮化物(SRN)層。富硅氮化物(SRN)層與銅金屬反應,形成了銅硅化物(CuSix)。

68.Copper Sealing & Barrier Deposition

然后,對CuSix進行氮化處理,將其轉(zhuǎn)化為SiN膜,沉積了一個300?的SiCN刻蝕停止層,以密封第一層金屬的頂部。現(xiàn)在,第一層金屬中的銅被Ta/TaN包圍在五個側面,并由SiCN封頂。

69.ILD-2 Deposition

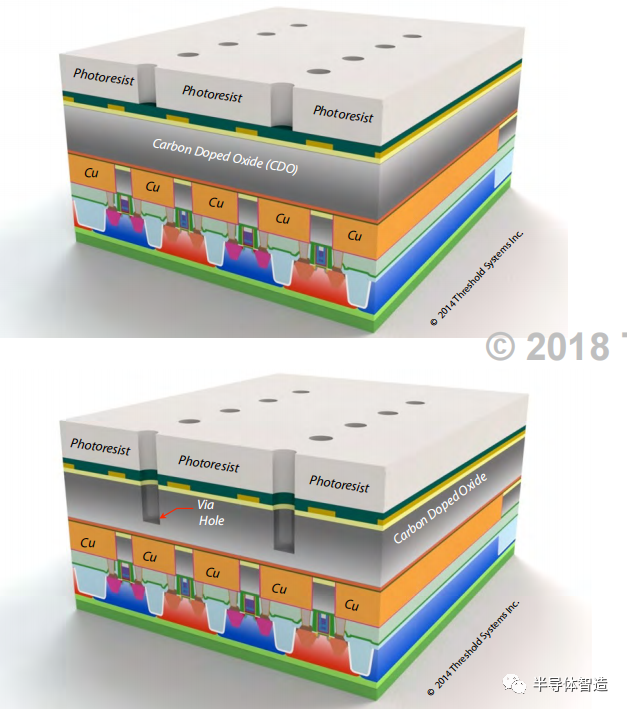

接下來,沉積了7,000 ?的低介電常數(shù)SiCOH,并進行紫外烘烤以去除孔原和降低介電材料的介電常數(shù)。然后,沉積了400 ?的TEOS(拋光停止層),接著是300?的TiN硬掩膜和300?的BARC層以及一層光刻膠。然后對光刻膠進行圖案化處理。

70.TiN Hard Mask Etch & PR Strip

71.Via Photo & Via Partial Etch

通過高度各向異性刻蝕工藝,對通孔進行部分刻蝕。但未完全刻蝕至SiCN刻蝕停止層。

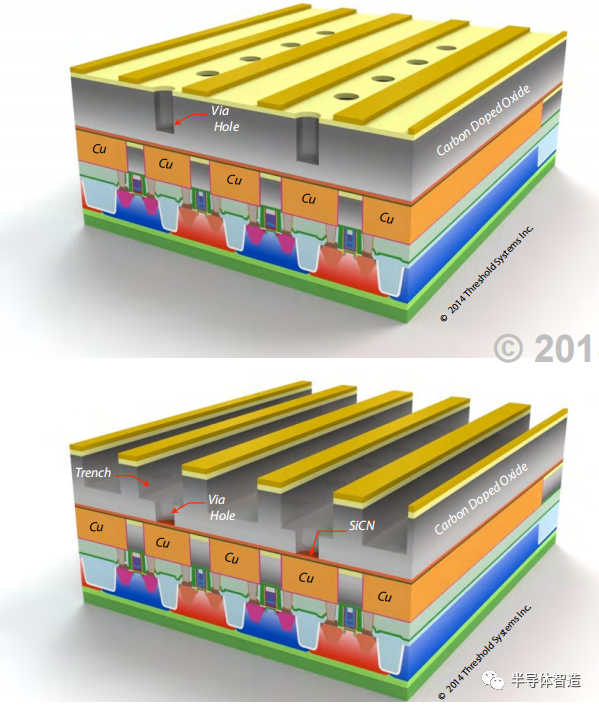

72.Photoresist Strip & Trench Etch

73.SiCN Barrier Opening

Dual Damascene結構的正視圖顯示了溝槽和眾多的通孔。請注意,通孔底部的SiCN屏障尚未穿孔。使用刻蝕工藝,打開通孔底部的SiCN屏蔽層,并暴露出底部的銅線。這是一個非常關鍵的步驟。如果刻蝕過于激烈,銅將噴射到未受保護的Dual Damascene結構中。如果刻蝕過輕,SiCN屏障將無法完全去除,導致通孔電阻增加。

74.TaN/Ta Barrier

接下來,使用IMP PVD方法沉積大約80 ?的TaN層,然后沉積大約30 ?的Ta層。這兩種金屬作為屏障,將尚未沉積的銅限制在溝槽中。在TaN和Ta操作之后進行再濺射處理。

Dual Damascene結構的正視圖顯示了覆蓋著TaN/Ta的溝槽和眾多的通孔。

與接觸孔類似,通孔非常微小且難以填充屏障金屬。然而,對于通孔來說,這個問題尤為重要,因為它們必須持續(xù)襯覆TaN/Ta,以便將稍后填充的銅封裝其中。任何TaN/Ta屏障金屬中的不連續(xù)性都會導致銅原子泄漏出通孔,造成晶體管污染。

專用的TaN/TaN離子化PVD工具結合濺射操作,確保實現(xiàn)適當?shù)钠琳细采w。

75.Cu Seed Deposition & Electroplated Copper

在晶圓上沉積約300?的銅種子層,覆蓋溝槽的內(nèi)部。

銅種子層的作用是確保完全貼合且無空隙的銅塊沉積(后續(xù)操作),同時也是電鍍過程的必要前提條件。接下來,使用電化學沉積法沉積大約6,000 ?的銅塊。

沉積完成后,將銅在300℃的成形氣體中退火90秒,以確定晶粒尺寸。

76.Copper CMP Polish & Final Seal

使用CMP技術對銅進行拋光,在沉積相同的SRN層后,將其轉(zhuǎn)化為CuSi,然后轉(zhuǎn)化為SiN,接著在第二層金屬的頂部沉積一個300?的SiCN層來封閉。第二層金屬(及其通孔)現(xiàn)在被TaN/Ta圍繞在五個側面,并在頂部被SiCN封裝。

需要注意的是,在這種Dual Damascene中,光刻膠從未接觸過低介電常數(shù)介質(zhì)。類似地定義了另外七個層的金屬溝槽和通孔。

-

半導體

+關注

關注

334文章

27363瀏覽量

218707 -

晶片

+關注

關注

1文章

403瀏覽量

31472 -

22nm

+關注

關注

0文章

51瀏覽量

18007 -

工藝流程

+關注

關注

7文章

106瀏覽量

16284 -

FinFET

+關注

關注

12文章

248瀏覽量

90230

原文標題:22nm Planar Process Flow介紹

文章出處:【微信號:光刻人的世界,微信公眾號:光刻人的世界】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

聯(lián)電宣布22nm技術就緒

透視IVB核芯 22nm工藝3D技術終極揭秘

22nm技術節(jié)點的FinFET制造工藝流程

銳成芯微宣布在22nm工藝上推出雙模藍牙射頻IP

Intel 22nm光刻工藝背后的故事

臺積電又跳過22nm工藝 改而直上20nm

平面VDMOS器件工藝流程和基本電參數(shù)的詳細資料說明

Arasan宣布用于臺積公司22nm工藝技術的eMMC PHY IP立即可用

北斗22nm芯片用途是什么?

22nm和28nm芯片性能差異

22nm芯片是什么年代的技術?

Trench工藝和平面工藝MOSFET的區(qū)別在哪呢?

Trench工藝和平面工藝MOS的區(qū)別

22nm平面工藝流程介紹

22nm平面工藝流程介紹

評論