1、引言

上一篇文章我們介紹了Arm的Cortex-X1至Cortex-X3系列處理器,2023年的5月底,Arm如期發(fā)布了新一年的處理器架構(gòu),分別為超級大核心Cortex-X4,大核心A720和小核心A520。在智能手機行業(yè),Arm始終保持每年一迭代的處理器架構(gòu)升級節(jié)奏,讓用戶可以不斷體驗到最先進的產(chǎn)品設(shè)計。本文主要介紹了2023年的新處理器架構(gòu)的變化,重點分析變化較大的Cortex-X4核心,并探討今年核心處理器架構(gòu)有哪些值得關(guān)注的改變。

2、整體介紹

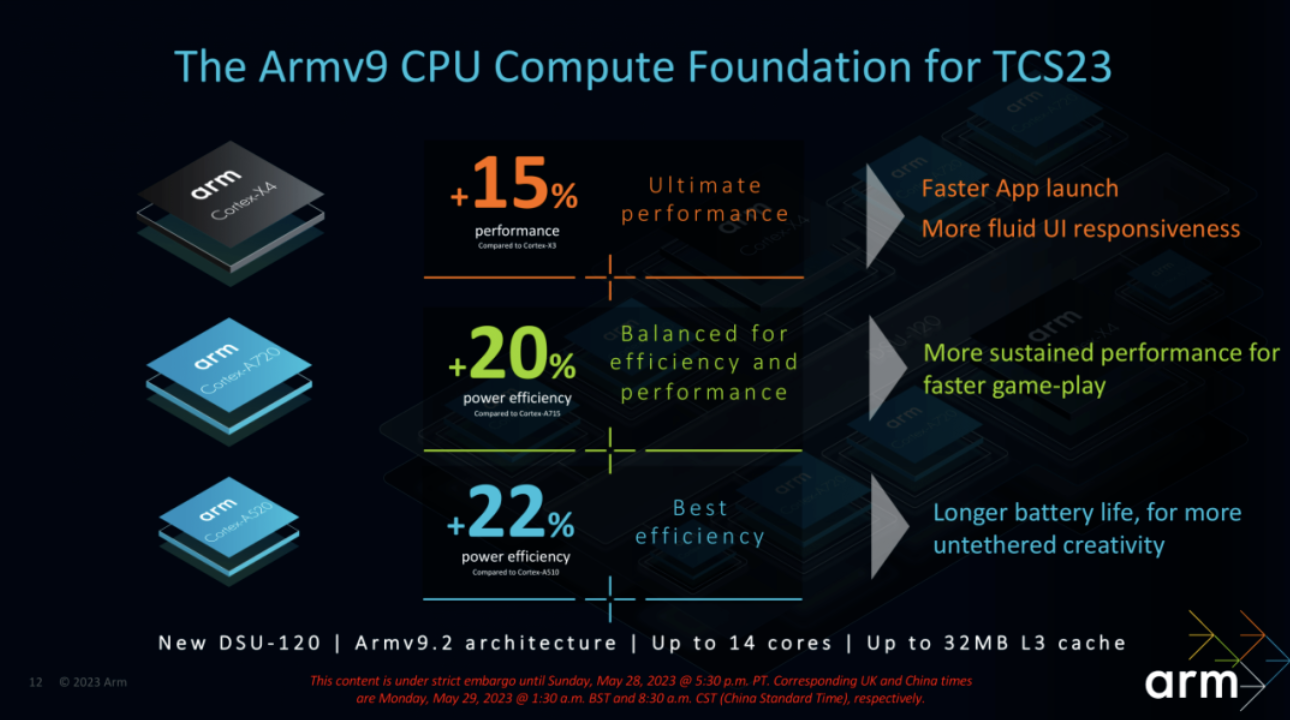

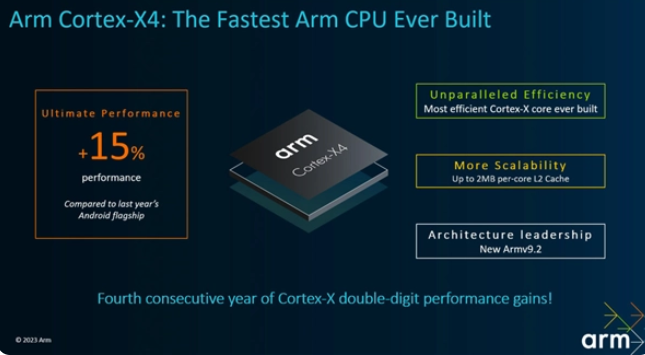

從Arm的宣傳數(shù)據(jù)可以看出,今年的三款處理機架構(gòu)側(cè)重點有所不同,Cortex-X4主打性能提升,相比上一代Cortex-X3提升15%的性能,A720和A520則偏重能效改善,相比上一代A715和A520分別改善20%和22%的能效。值得注意的是今年的處理器沒有升級工藝,這些數(shù)據(jù)應(yīng)該是基于相同工藝計算而來的(例如TSMC 4nm)。

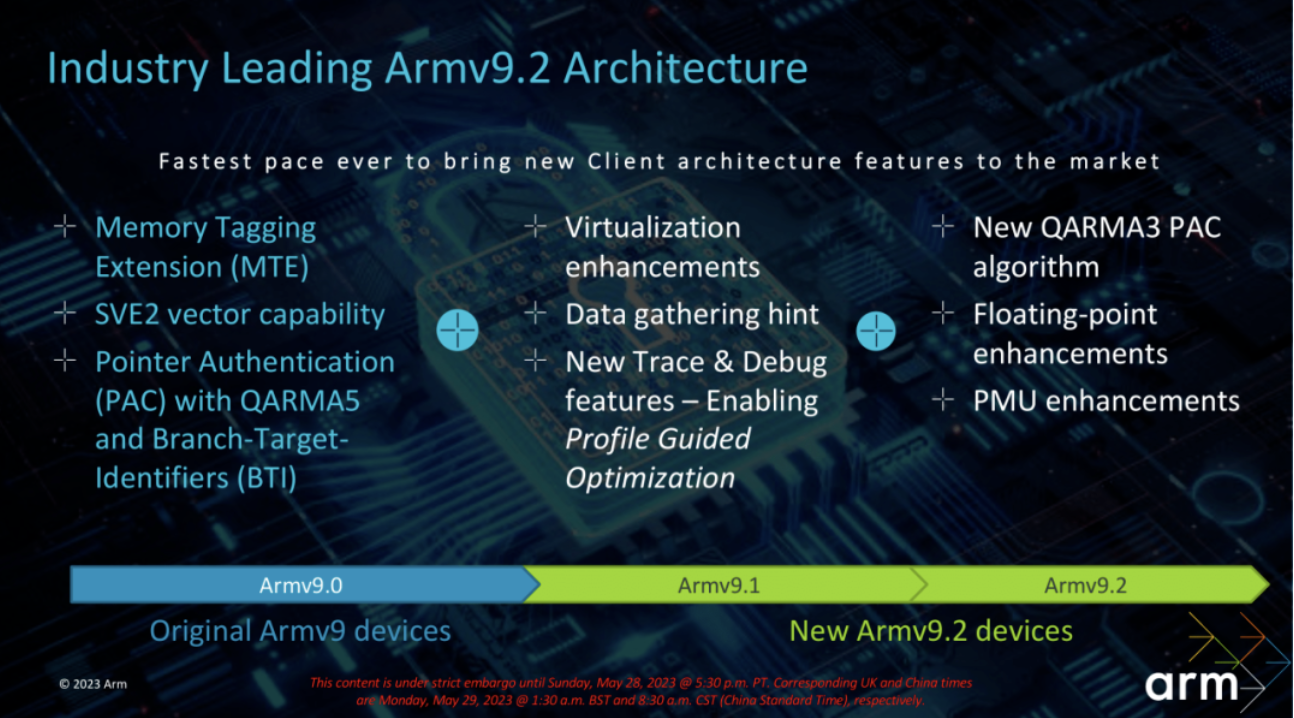

除了新的處理機架構(gòu),Arm在今年還帶來了全新的Armv9.2指令集,包括新的QARMA3 PAC算法、浮點能力增加和PMU增強等,最關(guān)鍵的變化是今年Arm計劃完全拋棄32bit應(yīng)用的支持,三個新的核心均不兼容32bit應(yīng)用。

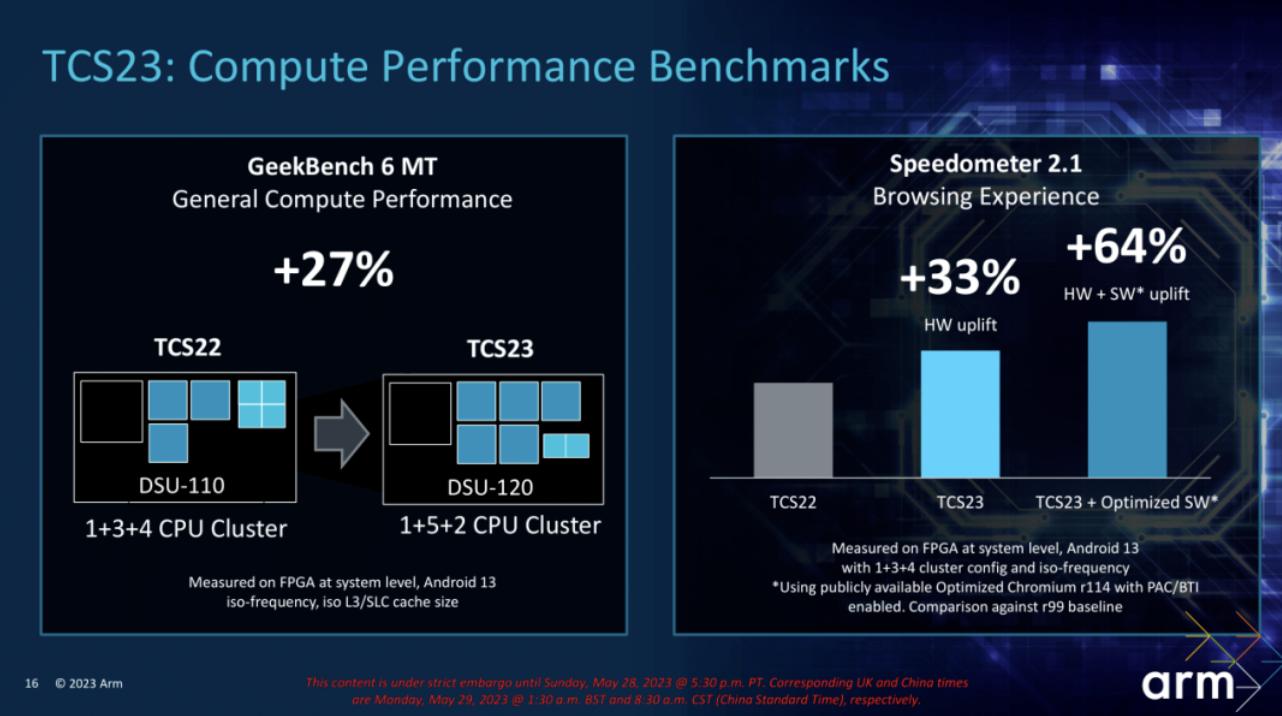

今年Arm還更新了DSU120模塊,用來更好管理處理器核心之間的數(shù)據(jù),并支持最多達14核心和最多32MB的L3緩存設(shè)計。從下面這張圖可以看出來,今年的處理器設(shè)計也有明顯變化,去年高通8Gen2處理器采用了1+4+3架構(gòu),今年我們會看到更少小核心的1+5+2架構(gòu)(參考鏈接3,高通8Gen3處理器),多核心性能有大幅度提升。

3、Cortex-X4微架構(gòu)分析

Cortex-X4的代號是Hunter-ELP,下圖是X4的微架構(gòu)圖,第一感覺是變“大”了,X4的核心變得越來越大,如果大家看過前幾篇文章,應(yīng)該可以感覺到這個微架構(gòu)設(shè)計越來越像另外一款行業(yè)領(lǐng)先處理器,殊途同歸,最優(yōu)秀的設(shè)計往往只有一個選擇,下面我們會詳分析今年的核心改變。

在前端設(shè)計上,X4取消了L0級別的MOP Cache,注意這個變化從大核心A715就開始了,這是一個大的改變,也側(cè)面說明MOP Cache的成本可能真的很高,在先進工藝中不經(jīng)濟。為了彌補取消MOP Cache的影響,X4這次將Decoder的數(shù)量從6個增加到了10個。上一代X3,如果從MOP Cache取數(shù)據(jù)是8-wide,從L1取數(shù)據(jù)是6-wide,這次的X4則統(tǒng)一是10-wide。在流水線長度上,X3如果從L1取數(shù)據(jù)是11級,從MOP取數(shù)據(jù)是9級,這次由于取消了MOP,X4特意優(yōu)化了流水線,從L1取數(shù)據(jù)從11級降到了10級。

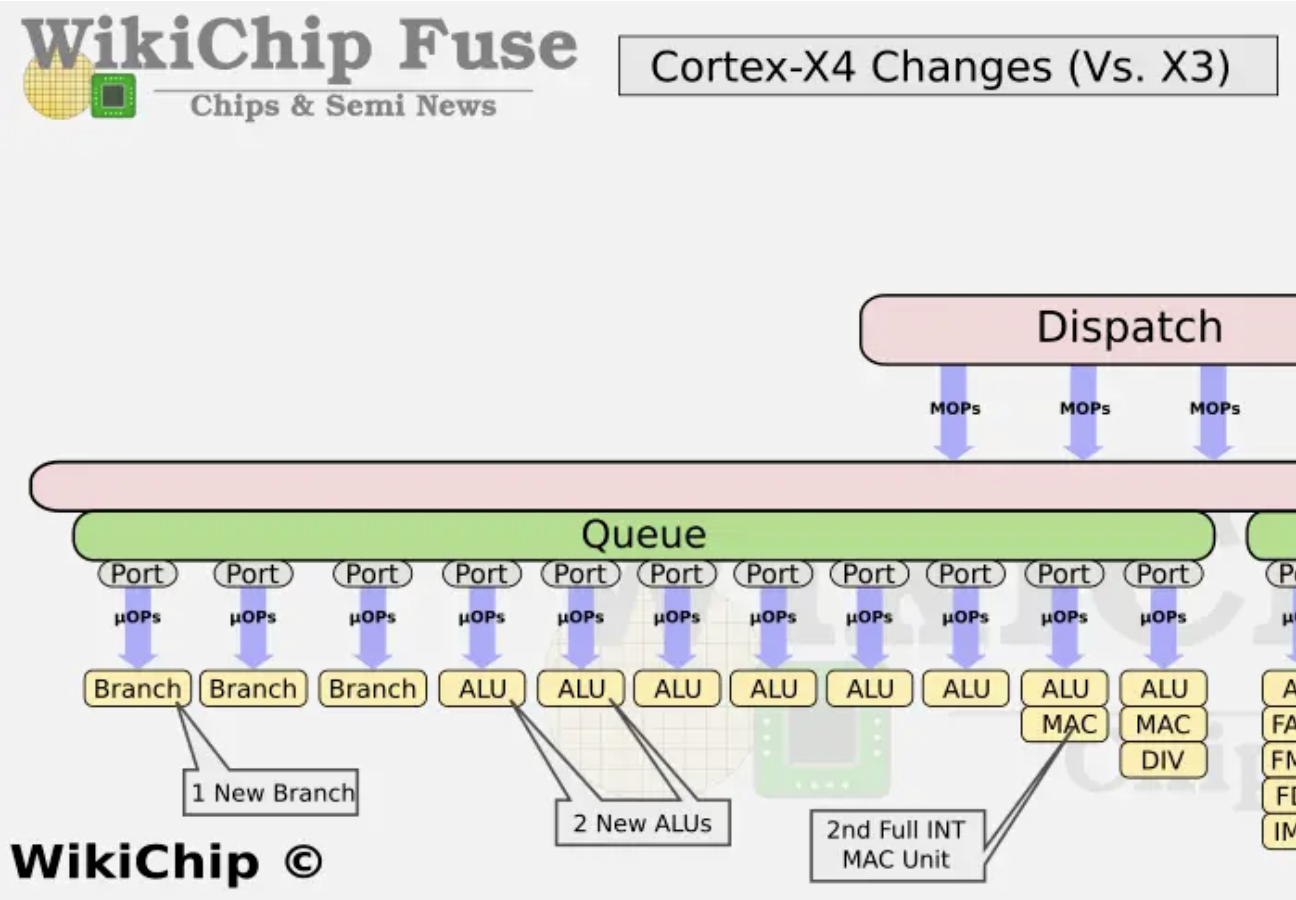

在后端設(shè)計上這次X4同樣變化不少,特別是運算單元,增加了1個新的Branch單元,2個新的ALU單元,并且提供了第二個完整的 MAC ALU單元,這些對于整體性能的提升都有顯著幫助。

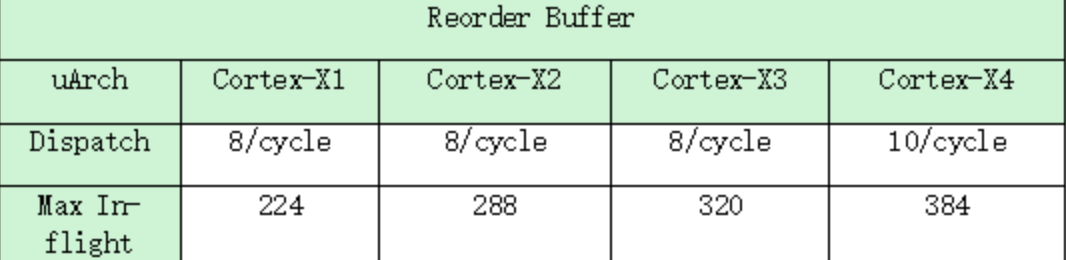

為了支撐新增的10個decoder和運算單元,X4的重排序緩沖(ROB)的尺寸也從320提升到384,提升了20%。

在存儲模塊方面,Arm重新調(diào)整了Load和Store單元的數(shù)量,X3有個LS AGU和1個LD AGU,X4則調(diào)整為1個 LS AGU,2個LD AGU和1個ST AGU。從3個AGU提升到4個AGU,但是功能稍有差異。此外,像L1的d-TLB,也從48提升到了96,增強了數(shù)據(jù)的處理能力。

這次X4核心還有一個特點是支持更大的L2緩存,從X3的最大支持1MB提升到X4最大支持2MB,根據(jù)Arm給出的數(shù)據(jù)顯示,2MB的L2緩存可以有效降低每千條指令的重填充和寫回率,不過由于增加緩存會增加成本,不一定所有廠商都愿意增加到最大的緩存尺寸。

從X4的整體性能數(shù)據(jù)看,Sepcint2K7提升達到了2位數(shù),Geekbench系列的提升在6-8%之間,只有個位數(shù)的提升,推測Geekbench對于L2不是很敏感,而對于L2緩存依賴的Sppdometer2這個benchmark提升比較明顯,注意這里面的測試數(shù)據(jù)使用2MB的L2測試得出的。

此外Arm資料顯示X4的典型CPU頻率可以跑到3.4G左右,雖然廠商實際處理器頻率還沒有確認,但是從上一代天璣9200+運行在3.35G推測,3.4G應(yīng)該是4nm能達到的一個比較高的頻率水平。

總結(jié)下Cortex-X4的關(guān)鍵改變:

1、取消了MOP Cache;

2、Decoder數(shù)量從6個提升到10個;

3、流水線統(tǒng)一為10級;

4、Branch單元從2個提升到3個;

5、ALU單元從6個提升到8個;

6、AGU單元增加了一個且功能有調(diào)整;

7、ROB尺寸從320提升到384;

8、L1的d-TLB從48提升到96;

9、最大支持的L2緩存從1MB提升到2MB;

10、不支持32bit。

整體性能上Sepcint2K7參數(shù)有13%-14%的提升。

4、A720微架構(gòu)分析

上一節(jié)我們列舉了10條X4內(nèi)核的微架構(gòu)變化,相比X4的大動作,A720和A520的變化則沒有那么大,但也有些值得我們研究和探討。

首先我們來看下A720,A720的代號叫做Hunter,A720的設(shè)計目標(biāo)是比A715提升20%的能效,在同樣的功耗下,A720可以提供更強的性能。

A720的的微架構(gòu)整體和A715差異不大,Arm并沒有增加fetch-decode寬度,也沒有增加諸如ROB尺寸之類的優(yōu)化,而是進一步深入到微架構(gòu)的細節(jié)調(diào)整以優(yōu)化能效。

在前端設(shè)計上,A720持續(xù)優(yōu)化分支預(yù)測能力,通俗的說就是走一步看兩步的能力。A720的分支預(yù)測錯誤的恢復(fù)周期從12降低到11周期,這個優(yōu)化對于實際用戶場景中無法準(zhǔn)確預(yù)測的案例很有幫助。在分支預(yù)測能力上,A710的大核心每周期可以預(yù)測2個unconditional分支,A715額外支持了conditional分支,A720則進一步進行了優(yōu)化了功耗,Arm宣稱可以在不影響性能的情況下降低功耗。

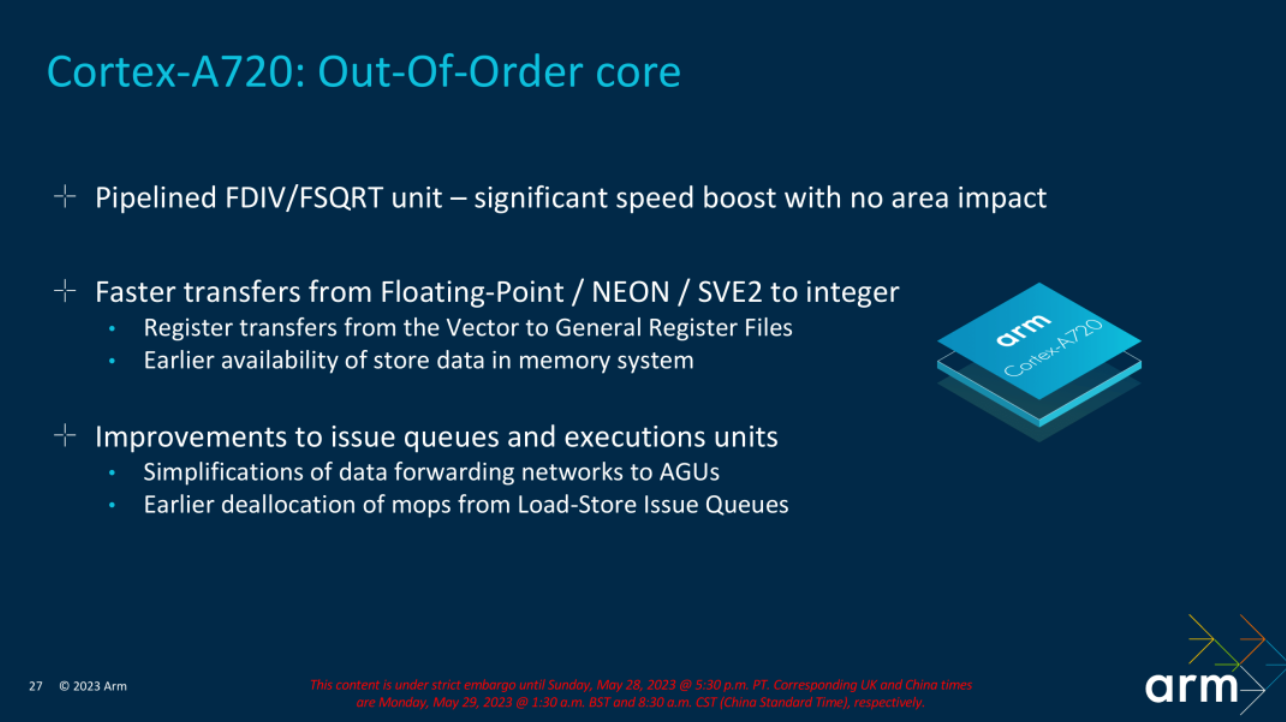

在后端設(shè)計上,A720通過管線化排序FDIVFSQRT單元(除法和開方),提升指令執(zhí)行能效。同時,A720優(yōu)化了數(shù)據(jù)在整型和浮點單元的傳輸效率,降低數(shù)據(jù)傳輸?shù)难舆t和存儲數(shù)據(jù)的延遲。A720還改進了發(fā)射隊列和執(zhí)行單元,簡化網(wǎng)點到AGU的數(shù)據(jù)傳輸?shù)取?/p>

A720在存儲模塊上有一個較為明顯的優(yōu)化是降低了L2訪問的延遲,從10個周期降低為9個周期,對于訪存多的場景會比較有幫助。另外A720支持的最大L2緩存數(shù)量還是512KB。

最后介紹一個A720在今年最大的變化,今年Arm的A720不是一個人,是一對雙胞胎,Arm提供了另外一個A720min(暫時這樣叫)的核心。這個核心和A720不同,在面積上做了一定的削減,整體核心面積大小和A78接近,性能上也弱于A720,但是比A78強10%左右。總結(jié),A720min的面積和A78接近(耗電也應(yīng)該接近),性能比A78強10%,屬于A720的一個分支。

最后簡單總結(jié)下A720的關(guān)鍵改變:

1、分支預(yù)測錯誤的恢復(fù)周期從12降低到11周期;

2、L2訪問延遲從10個周期降低為9個周期;

3、提供了一個A720min的選擇,面積和A78接近,性能比A78強10%。

5、A520微架構(gòu)分析

我們來看一下小核心A520,A520小核心的代號叫做Hayes,依然不支持亂序執(zhí)行,設(shè)計相對簡單,主打能效改善。A520依然繼承了A510的2個小核心拼接在一起共享SIMD單元的設(shè)計,這次的A520也是僅支持64bit,不再支持32bit。A520提供了新的QARMA3 PAC算法,旨在將PAC的影響降低到1%以內(nèi)。

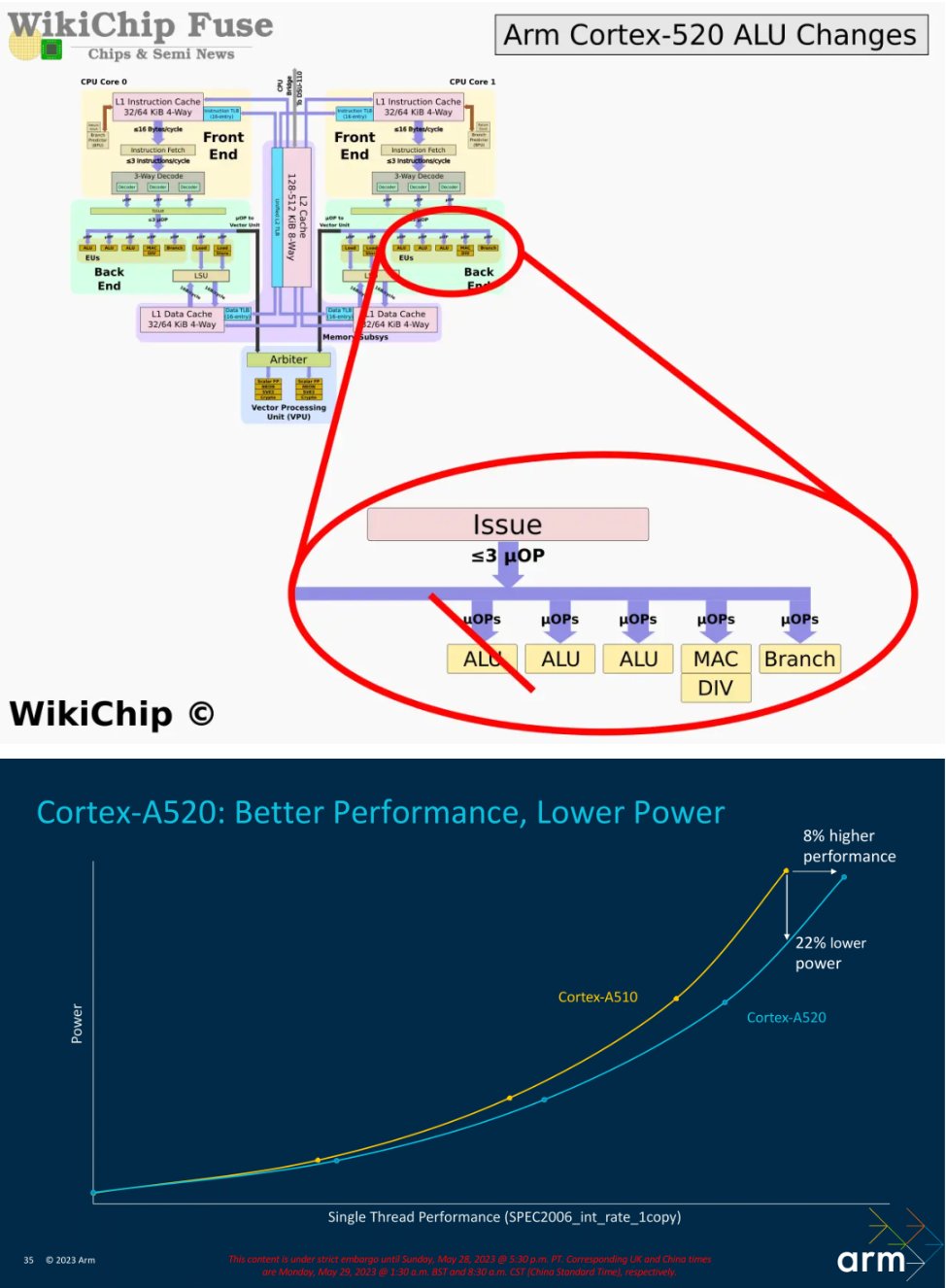

相比A510,A520為了提升能效還做了減法,主要的變化是減少了一個執(zhí)行單元的ALU。A510有3個ALU,A520只有2個。當(dāng)然,Arm說通過全局的優(yōu)化有將性能的損失彌補回來,從Arm提供的數(shù)據(jù)上看,A520在相同的性能下,功耗可以降低22%;在相同的功耗下,性能可以提升約8%,我們也會實際測試看看。

可惜,8%的性能提升相比旗艦處理器的需求還是有一定差距,我們看到在今年的旗艦處理器設(shè)計上,芯片廠商在繼續(xù)減少使用A520小核心,甚至有的廠商完全沒有使用A520小核心。

6、DSU120分析

最后我們來看一下用于協(xié)調(diào)處理器核心和緩存的DSU模塊,Arm升級了最新的DSU120模塊,可以在一個Cluster內(nèi)支持最多14個核心,并且支持最多32MB的L3緩存管理。

DSU120提供了一個有價值的功能,隨著L3緩存越來越大,靜態(tài)漏電也成為一個需要考慮的影響因素,會影響手機的待機耗電場景。DSU120提供了一個L3部分關(guān)閉的功能,在一些不需要使用那么大緩存的場景,關(guān)閉部分L3緩存,可以減少靜態(tài)漏電。

7、總結(jié)

本文主要分析了Arm公司于2023年最新發(fā)布的Cortex-X4、A720和A520等處理器架構(gòu)。今年是Arm公司發(fā)布的第四代X系列處理器,通過前面的分析,我們可以看到Arm在不斷提升其核心處理器的計算性能,挑戰(zhàn)業(yè)內(nèi)最先進的架構(gòu)設(shè)計。同時,Arm也通過優(yōu)化A720、A520的能效,給用戶提供在芯片能效上更有競爭力的產(chǎn)品組合。

2023年,芯片廠商也不滿足傳統(tǒng)的核心搭配,開始了減少小核心,增加大核心的架構(gòu)升級。我們今年可以看到更多的多大核心SOC設(shè)計,在多核心性能上有了進一步的提升。無疑,2023年的處理器競爭會更加激烈,多大核心的引入也需要警惕功耗和發(fā)熱增加的風(fēng)險,作為芯片和智能設(shè)備終端的開發(fā)者,需要充分了解處理器架構(gòu),通過合理的軟硬件調(diào)度設(shè)計,將芯片的能效優(yōu)化到最佳,給用戶提供最佳且可持續(xù)的性能表現(xiàn)。

-

TSMC

+關(guān)注

關(guān)注

3文章

177瀏覽量

84501 -

ARM處理器

+關(guān)注

關(guān)注

6文章

360瀏覽量

41741 -

Cache

+關(guān)注

關(guān)注

0文章

129瀏覽量

28343 -

PAC

+關(guān)注

關(guān)注

0文章

72瀏覽量

27912 -

PMU

+關(guān)注

關(guān)注

1文章

108瀏覽量

21600

發(fā)布評論請先 登錄

相關(guān)推薦

Canon(佳能) PowerShot A720數(shù)碼相機中文

Canon(佳能) PowerShot A510/A520數(shù)

AMD推出入門級A520 A520相關(guān)參數(shù)分析

AMD Zen3全新架構(gòu)的銳龍5000系列處理器已經(jīng)正式上市

Arm發(fā)布全新一代Cortex移動CPU架構(gòu)

Arm發(fā)布Cortex X4,功耗可降低40%!

Arm發(fā)布Corte-X4/A720/520 CPU新架構(gòu)

消息稱聯(lián)發(fā)科天璣 9300 處理器采用 4+4 全大核架構(gòu);恒馳汽車稱天津工廠已全面復(fù)產(chǎn)

Armv9.2家族添新成員,全新Cortex-X4、A720和A520CPU內(nèi)核:性能再創(chuàng)新!

vivo X100首發(fā)搭載聯(lián)發(fā)科天璣9300芯片即將發(fā)布

Arm最新處理器架構(gòu)分析—X4、A720和A520

Arm最新處理器架構(gòu)分析—X4、A720和A520

評論