1 簡介

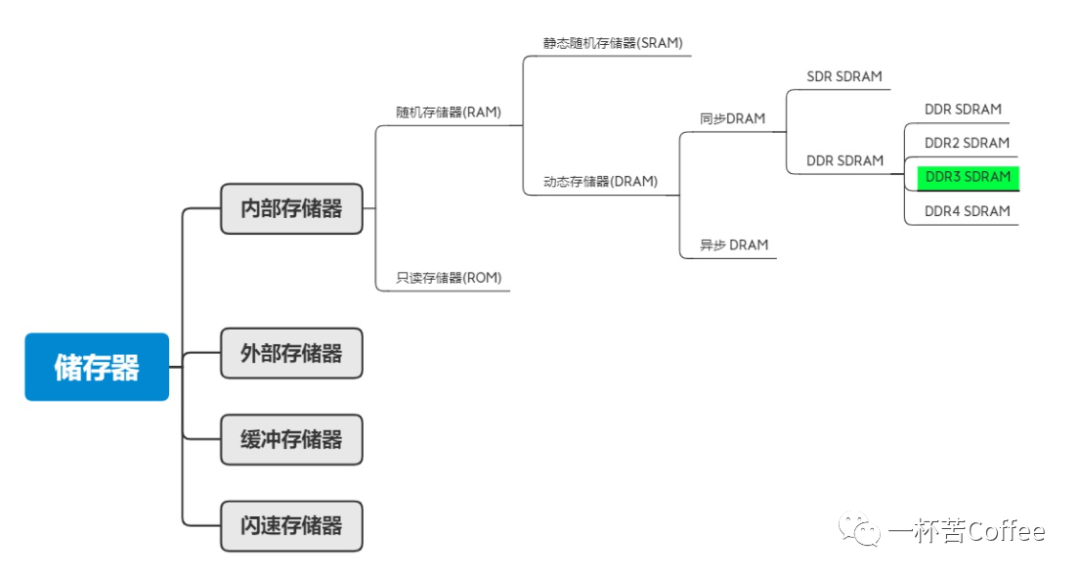

DDR4(第四代雙倍數據速率同步動態隨機存取存儲器)是一種高帶寬的存儲器,今天主要講述一下DDR4在Layout過程中的一些細節。在DDR的設計過程中,DDR的Layout是十分重要的環節。

2 DDR4的拓撲結構

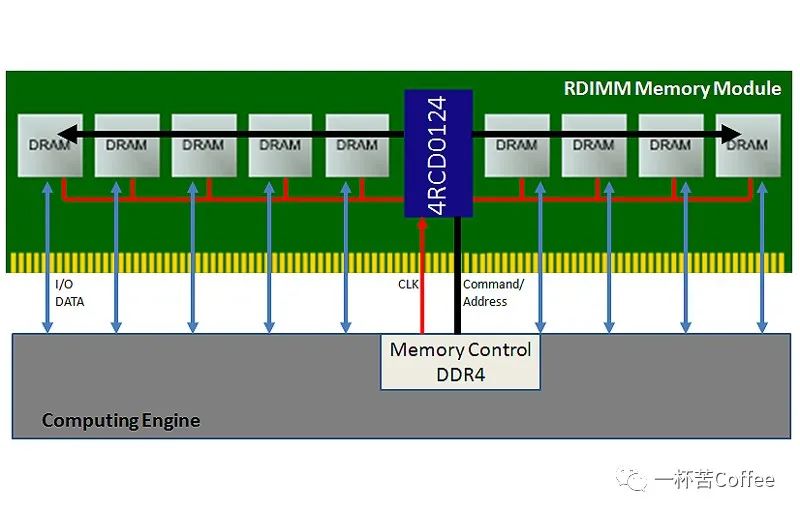

DDR4 SDRAM支持兩種拓撲類型:FLY-BY和Clamshell。

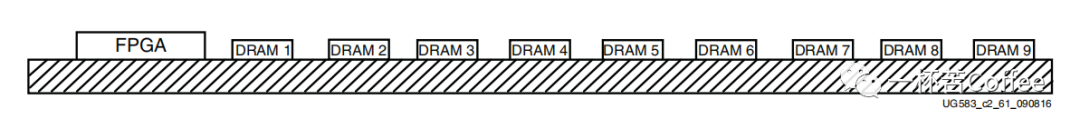

FLY-BY拓撲結構

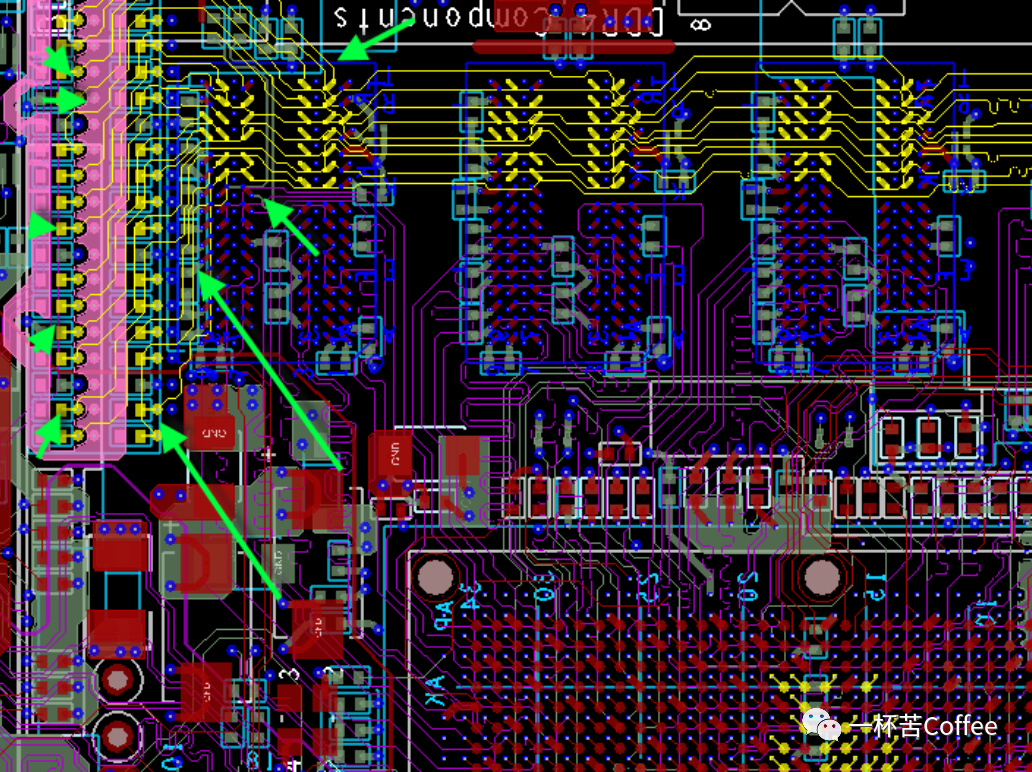

FLY-BY拓撲結構將所有存儲設備放置在同一層(詳見下圖),這種拓撲結構更有利于數據通信,并且可以提供最佳的信號完整性,但是會占用寶貴的電路板空間。

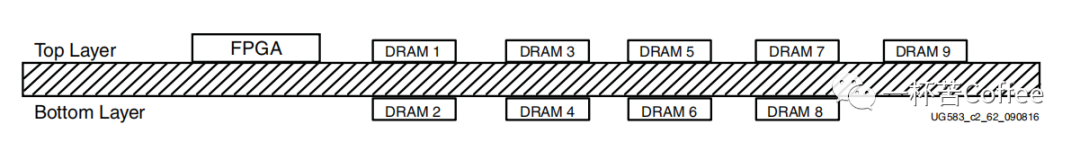

Clamshell拓撲結構

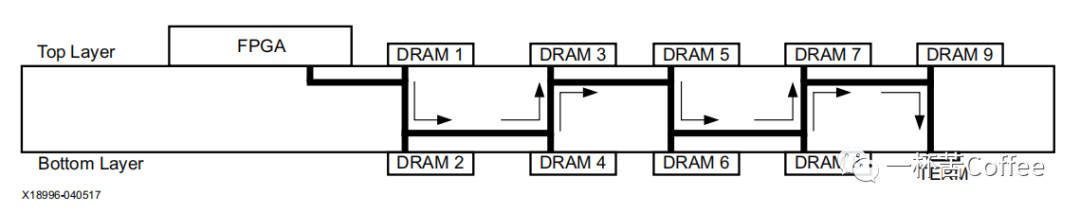

Clamshell拓撲結構將存儲設備可以同時放置在TOP層和BUTTON層(詳見下圖),相對于FLY-BY拓撲結構,這種拓撲結構不利于數據通信,但是能節省大量的電路板空間。

3 Layout要求

信號分組:

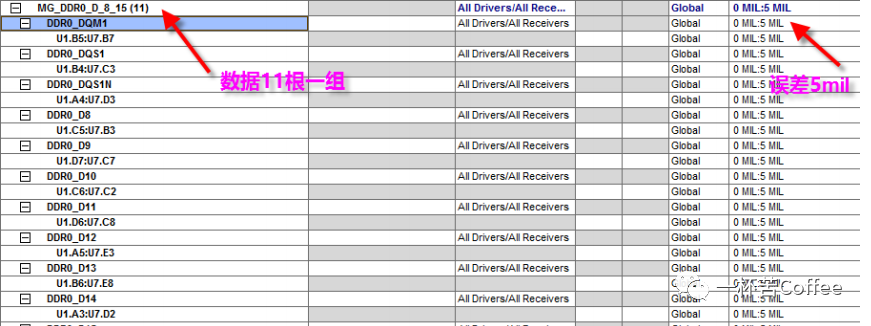

- DQ[7:0]、DQM0、DQS0(Diff)為一組(共是11根信號線);

- DQ[15:8]、DQM1、DQS1(Diff)為一組(共是11根信號線);

- 所有的地址線、時鐘線以及控制線為一組。

阻抗控制:

- 單端信號的阻抗控制在50歐姆;

- 差分信號的阻抗控制在100Ω。

3.1布局要求

地址線布局布線要求優先選擇Fly-BY拓撲結構,鑒于地址線一般不會走在表層,所以出線后打過孔。過孔到引腳的長度盡可能短,長度在150mil(3.81mm)左右。

地址線和控制線的上拉匹配電阻放置在最后一個顆粒的末端,與顆粒的走線長度不要超過500mil(12.7mm),并且每個上拉電阻都要放置一個對應的VTT濾波電容(0.1uF),最多可以兩個上拉電阻共用一個濾波電容。

3.1布線要求

走線要求

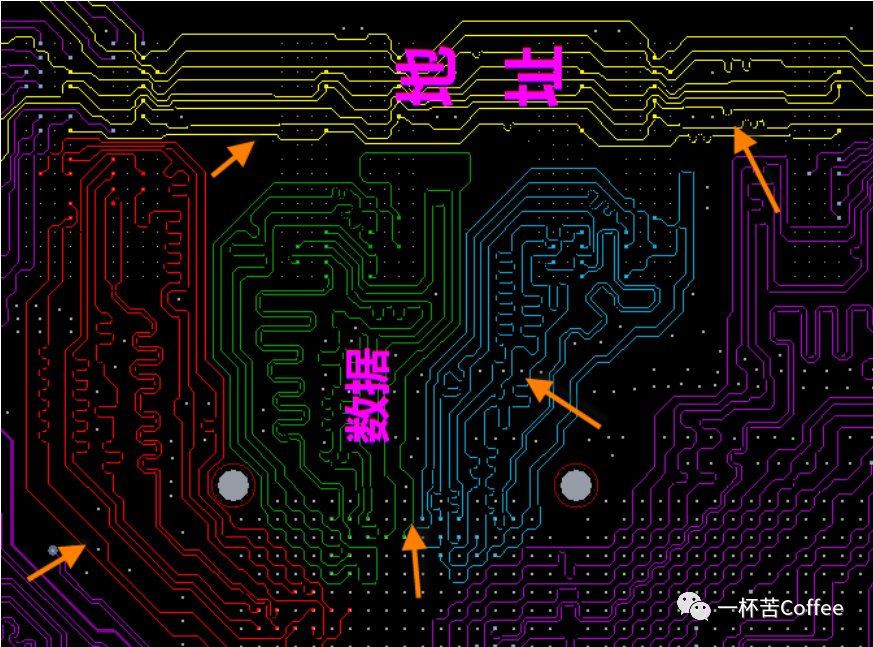

8根同組DQ數據線必須保證同層,DQM0、DQS0(Diff)有效保證與DQ數據線同層。另外地址線、控制線、以及時鐘線按照FLY-BY拓撲結構走線。

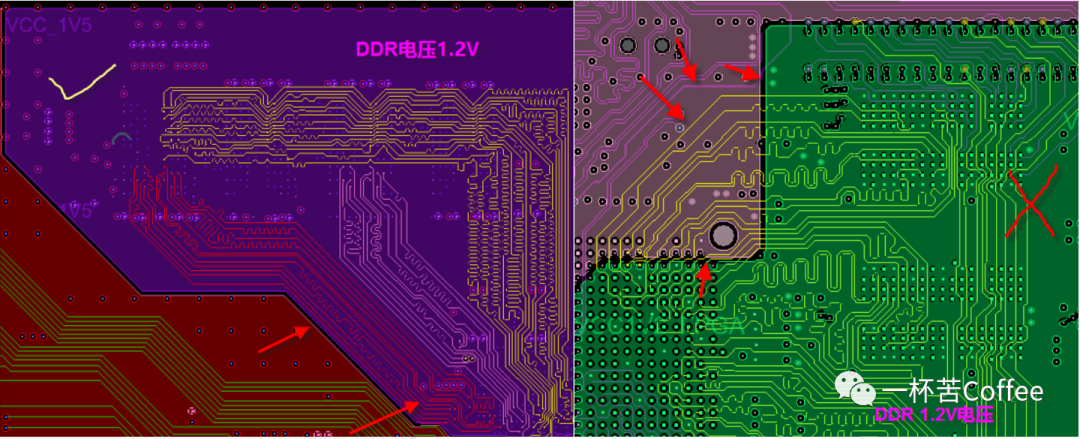

平面分割要求

為了保證電源完整性和信號完整性,DDR4的走線必須有完整電源參考平面,堅決杜絕跨分割現象,疊層時考慮讓地平面緊挨著電源平面,保證電流回流路徑最短。

等長要求

數據線走線盡可能短,走線總長度不能超過2000mil(50.8mm),分組等長,組內等長誤差需要控制在±5%。(DQS和時鐘線沒有等長誤差要求,部分芯片有組件以及DQS和時鐘線的等長要求,具體需要參考手冊)

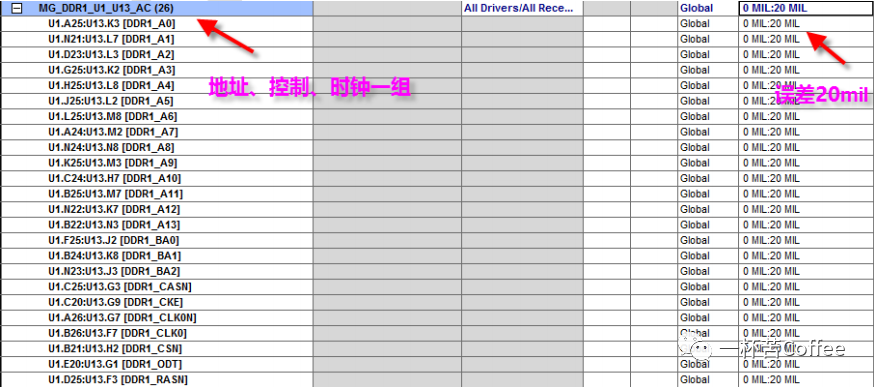

地址線、控制線、時鐘線作為一組等長,組內誤差不允許超過±20%;

DQS和時鐘差分線對內誤差范圍控制±1%;

信號的實際長度包括PIN腳長度、PIN Delay等。

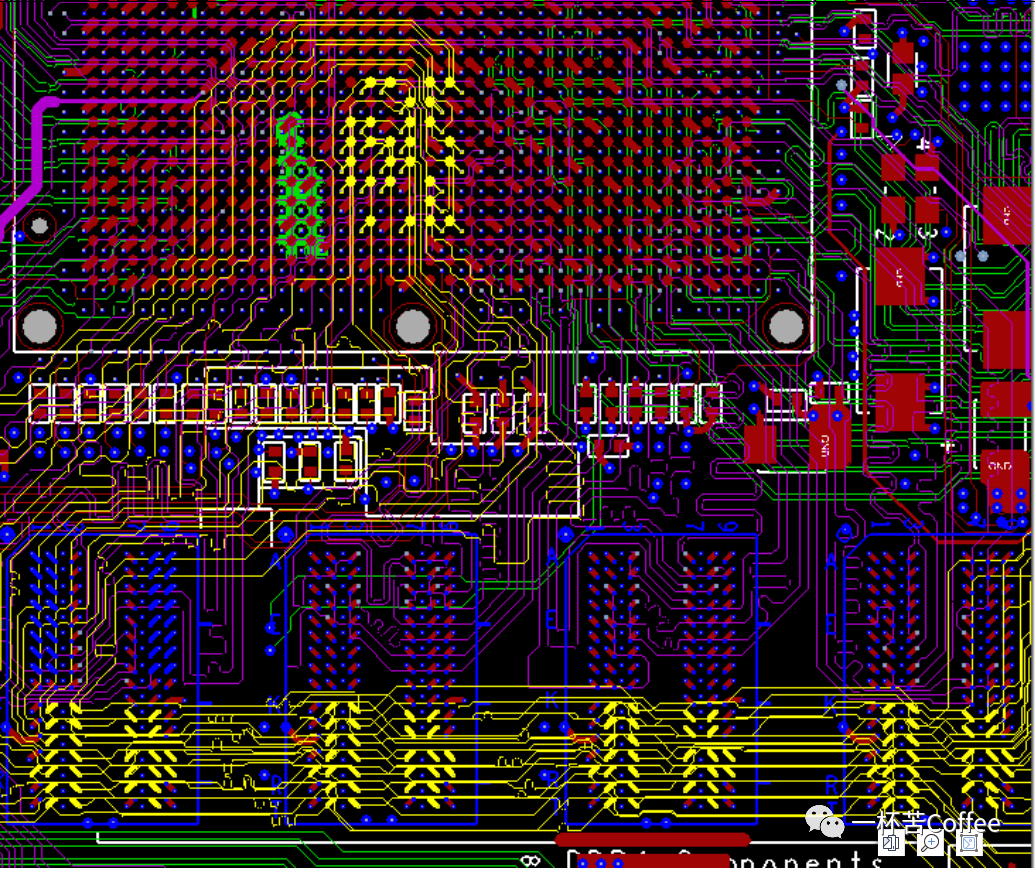

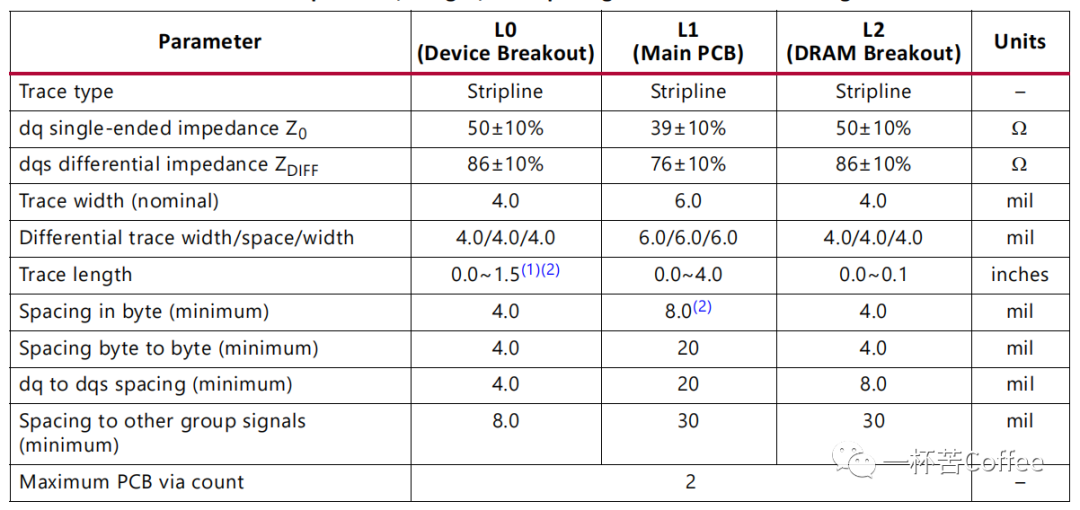

4 FPGA布線要求

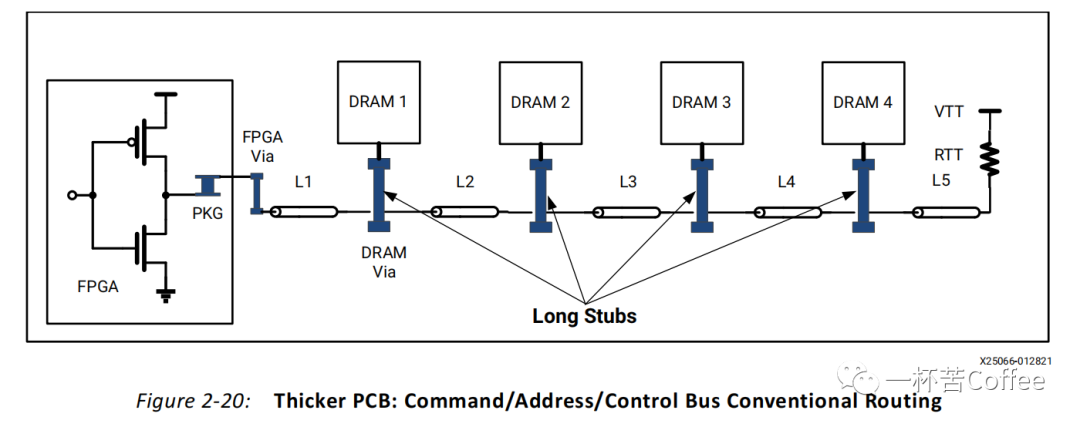

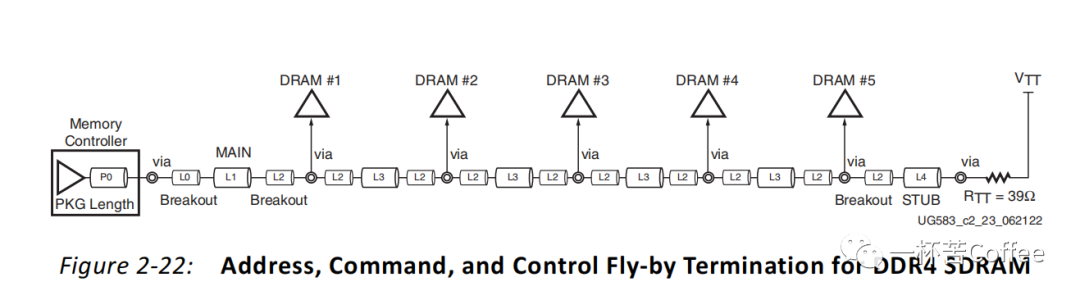

在PCB上,命令、地址和控制總線的路由見下:

4.1 FLY-BYU拓撲結構

命令、地址和控制總線的布局布線

命令、地址和控制總線布局方式見下:

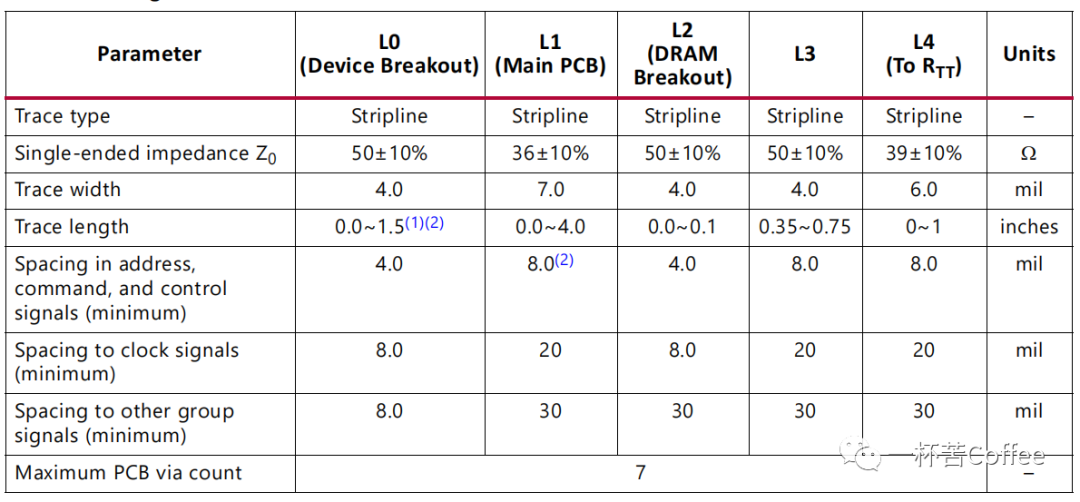

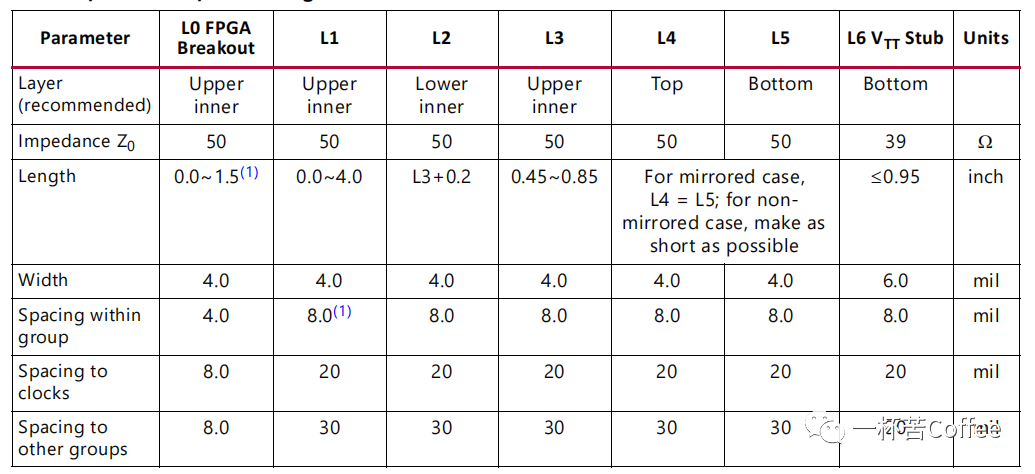

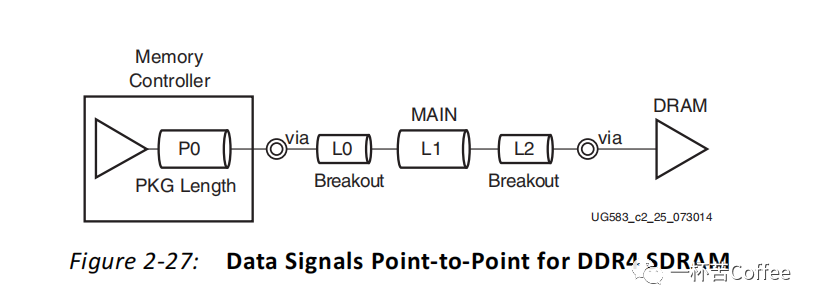

數據線的阻抗、長度以及布線指導見下表:

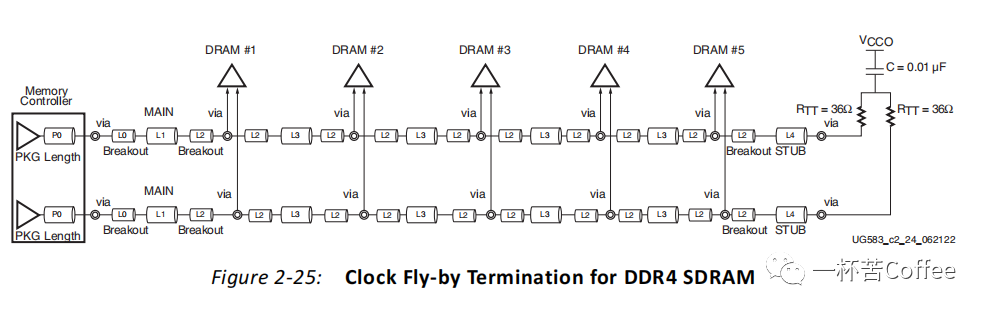

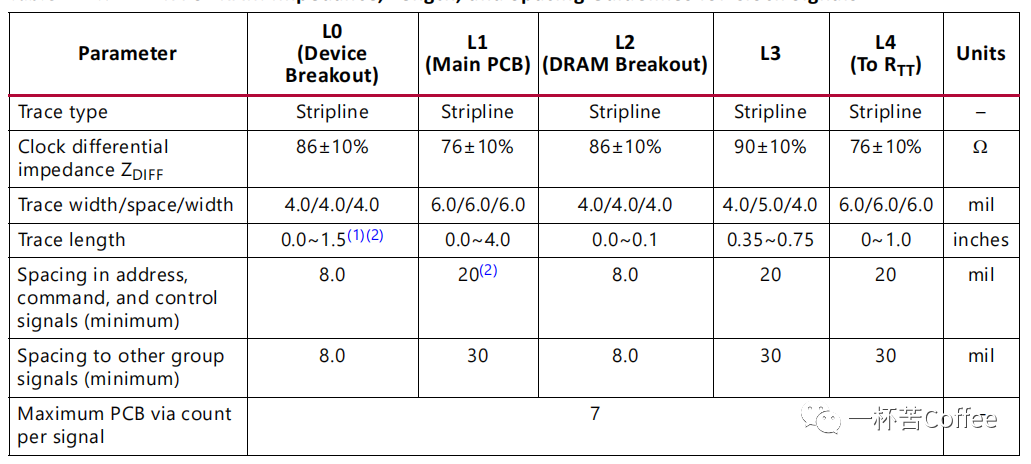

時鐘線的布局布線

命令、地址和控制總線布局方式見下:

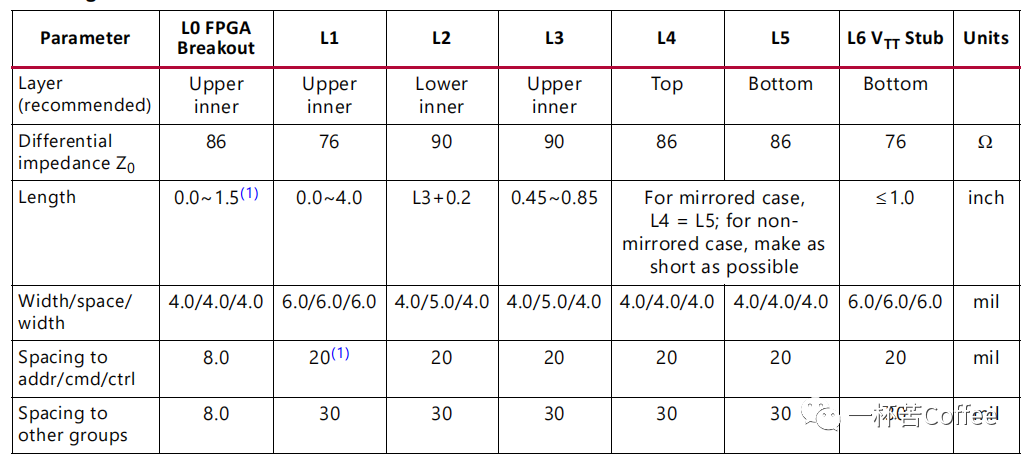

數據線的阻抗、長度以及布線指導見下表:

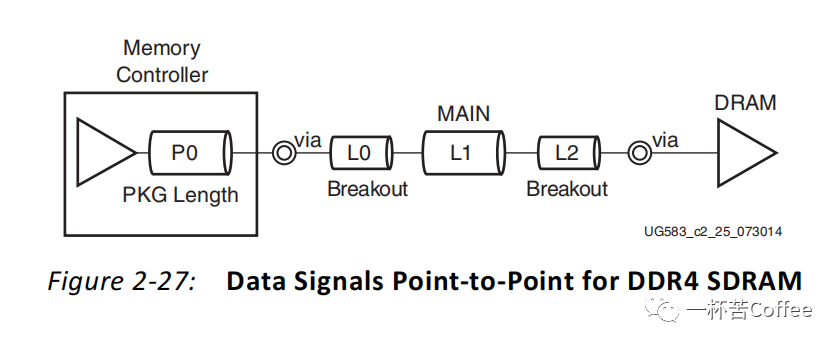

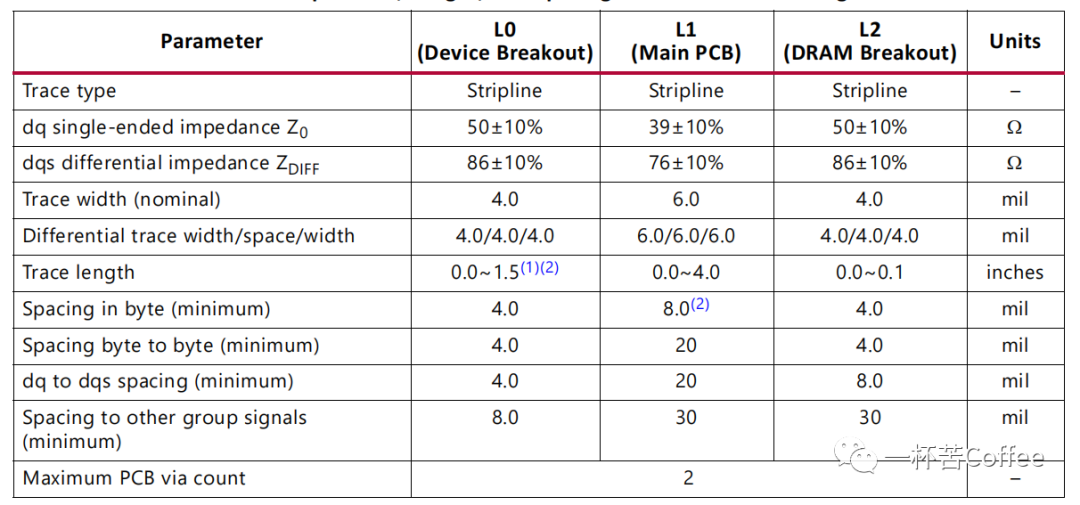

數據線

兩種拓撲結構的數據線(DQ、DM、DQS)的點對點連接方式相同。

數據線的阻抗、長度以及布線指導見下表:

4.2 Clamshell拓撲結構

命令、地址和控制總線的布局布線

命令、地址和控制總線布局方式見下:

數據線的阻抗、長度以及布線指導見下表:

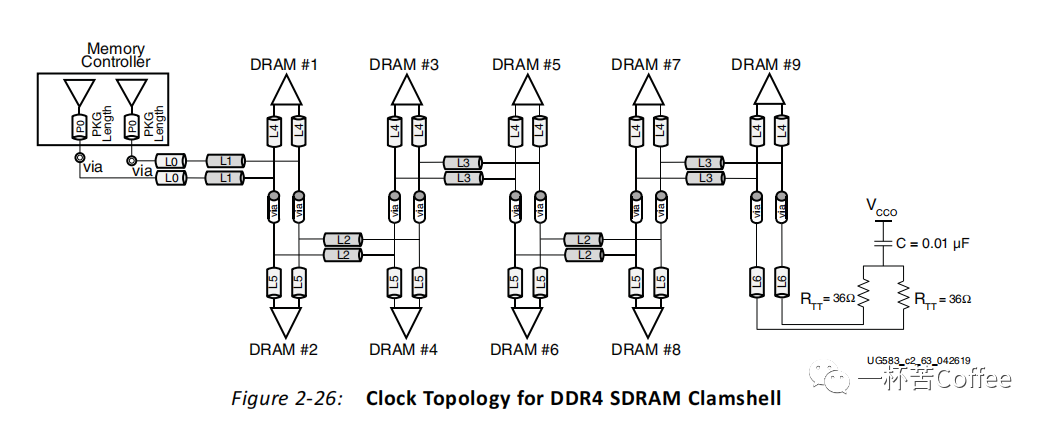

時鐘線的布局布線

命令、地址和控制總線布局方式見下:

數據線的阻抗、長度以及布線指導見下表:

數據線

兩種拓撲結構的數據線(DQ、DM、DQS)的點對點連接方式相同。

數據線的阻抗、長度以及布線指導見下表:

-

存儲器

+關注

關注

38文章

7492瀏覽量

163842 -

電路設計

+關注

關注

6675文章

2453瀏覽量

204366 -

DDR

+關注

關注

11文章

712瀏覽量

65344 -

Layout

+關注

關注

14文章

404瀏覽量

61779 -

DDR4

+關注

關注

12文章

321瀏覽量

40797

發布評論請先 登錄

相關推薦

怎么成為硬件電路設計高手?

硬件電路設計的思路分享

FPGA的硬件電路設計教程和FPGA平臺資料簡介

硬件電路設計之“磁珠”的應用資料下載

硬件電路設計之DDR電路設計(4)

硬件電路設計之DDR電路設計(4)

評論