現場可編程門陣列 (Field Programmable Gate Array, FPGA)也稱為現場可編程器件,是在 PROM ( Programmable Read Only Memory )、PLD ( ProgrammableLogic Device)、 PLA ( Programmable Logic Array)、 GAL (Gate Array Logic)、CPLD ( Complex Programmable LogicDevice)等可編程器件的基礎上,發展成的一種半定制化集成電路芯片,它具有硬件可編程的特點。

1985年 Xilinx 公司推出全球第一款 FPGA 產品 XC2064, 使用了 2μm 制造工藝,包含64個邏輯塊(合1200個邏輯門)。 2003 年 Xilinx 公司推出了 90nm制造工藝的 Spartan-3 系列產品,隨后又推出了 65nm制造工藝的 Virtex-5 系列產品和 45nm制造工藝的 virtex-6系列產品。2011年 Xilinx公司和 Altera 公司相繼推出了 28nm制造工藝的 FPGA 產品,這些產品具有高效的邏輯集成功能和更低功耗。2016年Xilinx公司和 Altera 公司推出了 16nm 制造工藝的 FPGA 產品。

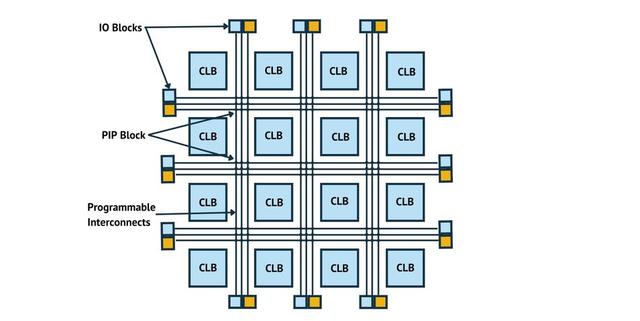

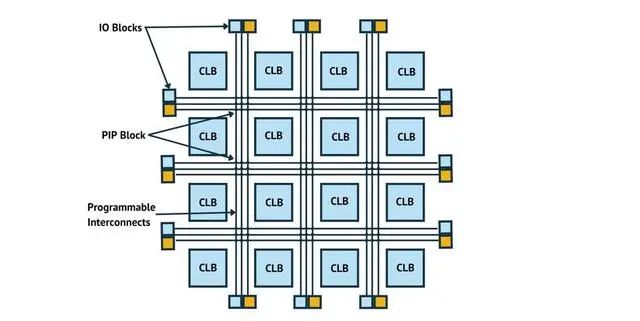

FPGA主要由可編程輸入/輸出單元(I/O Blocks)、可編程邏輯塊(Configurable Logic Block, CLB,簡稱邏輯單元)、嵌入式 RAM、可編程布線、底層嵌入功能單元和內嵌專用硬核六大部分組成。可編程邏輯塊是 FPGA 的基本邏輯單元,它由觸發器(Trigger)和查找表 (Look-Up Table, LUT)兩部分組成。

FPGA 芯片包含數以百萬計的邏輯單元,配置它們實現特定的邏輯功能十分復雜,需要使用專用 EDA 開發工具編譯出對應的配置文件或二進制碼流。主流的 FPGA 廠商的 EDA 開發工具主要有 Altera(2015 年被Intel 并購)的 QuartusⅡ、Xilinx 的ISE 和 Vivado、Lattice 的 ispLEVER、 Atmel (2016 年被 Microchip 并購)的pASSP 和 Actel (2010年被 Microsemi 并購)的Libero。

FPGA 設計方法的發展可劃分為三個時代,即硬件描述時代、嵌入式軟核時代和異構系統時代。

硬件描述時代是 FPGA設計的第一個時代。設計人員根據待設計的電路功能使用硬件描述語言 ( Hardware Description Language, HDL)完成開發。由于模塊化數字電路可被封裝為 IP (Intellectual Property)核的形式,使用 IP 核完成FPGA 的最終設計,可大大提高效率。

嵌入式軟核時代是 FPGA 設計的第二個時代。它以 Altera 公司的微處理器軟核Nios Ⅱ和 Xilinx公司的微處理器軟核Microblaze 為代表。設計人員利用 FPGA內部的邏輯資源搭建微處理器軟核,再將 I/0 接口等IP軟核連接至微處理器軟核總線,從而構成可編程系統芯片 (Programmable Systemon Chip,PSoC)。設計人員可使用C、C++等高級語言控制可編程片上系統工作,實現軟硬件協同設計。?????

在功耗、性能和開發周期等因素的驅動下,FPGA 設計進入了異構系統時代。以CPU 為核心的哈佛結構(或馮氏結構)和可編程邏輯電路同時存在于FPGA中,使異構系統更具綜合優勢。例如,Altera 的 Cyclone V 系列和 Xilinx的Zynq系列均包含ARM硬核。同時,隨著高層次綜合 ( High -Level Synthesis,HLS)的推出,FPGA 的 EDA 工具得到進一步的發展,可直接使用C、C++等語言對 FPGA 進行硬件編程,更大程度地提高了 FPGA 的設計效率。

2010 年后,神經網絡技術在人工智能領域得到了廣泛的應用。FPGA 因具有高度并行、高吞吐量、低功耗和可重構等特點而備受關注,成為在實現深度學習算法的系統中提高性能功耗比的重要器件。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603319 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121401 -

可編程器件

+關注

關注

2文章

59瀏覽量

20936 -

現場可編程門陣列

+關注

關注

1文章

20瀏覽量

4730

原文標題:現場可編程門陣列,現場可程式閘陣列,Field Programmable Gate Array (FPGA)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

簡單認識現場可編程門陣列

簡單認識現場可編程門陣列

評論