什么是DRE觸發器?

FF_DRE是一個具有異步設置(SET)和重置(RST)輸入的邊緣觸發的D觸發器(D Flip-Flop)

在任意時刻,當SET或RST為TRUE時會忽略CLK信號而設置或重置Q信號,RST比SET具有優先權,即RST和SET同為TRUE時,Q被重置為0。

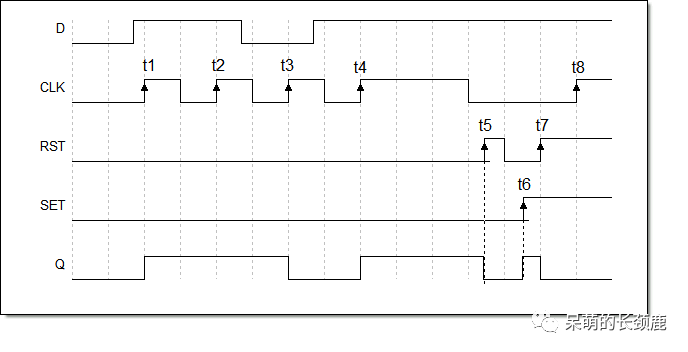

時間圖如下:

特征表如下:

其中: CLK:時鐘, RST:重置, SET: 設置 , D:輸入 , Q:輸出

- 假設最初 輸入都為0,輸出 Q = 0;

- 在t1處,RST=SET=0,D=1 ,輸出Q=1;

- 在t2處,RST=SET=0,D=1 ,輸出Q=1;

- 在t3處,RST=SET=0,D=0 ,輸出Q=0;

- 在t4處,RST=SET=0,D=1 ,輸出Q=1;

- 在t5處,RST=1 ,盡管D=1,但輸出Q=0;

- 在t6處,RST=0,SET=1,輸出Q=1;

- 在t7處,RST=SET=1,RST具有優先權,輸出Q=0;

- 在t8處,RST=1,盡管CLK上升沿,但輸出Q=0;

源代碼如下:

FUNCTION_BLOCK "FF_DRE"

TITLE = 'FF_DRE'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

SET : Bool;

D : Bool;

CLK : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST OR #SET THEN

#Q := NOT #RST;

ELSIF #CLK AND NOT #edge THEN

#Q := #D;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

D觸發器

+關注

關注

3文章

164瀏覽量

47915 -

DRE

+關注

關注

0文章

4瀏覽量

6626 -

RST

+關注

關注

0文章

31瀏覽量

7397 -

CLK

+關注

關注

0文章

127瀏覽量

17171

發布評論請先 登錄

相關推薦

D觸發器Verilog描述

,呵呵。。。上半年,由于Boss項目,學習了FPGA,學的有點急,也斷斷續續的,才過幾個月,似乎知識已經遠去,打開電腦,速覽以前的資料,記憶又回來了。。。簡單記錄下這道題,權當回憶。。。//基本D

發表于 02-22 13:54

d觸發器有幾個穩態 d觸發器和rs觸發器的區別

D觸發器的穩態 D觸發器是數字電路中常用的一種存儲元件,它有兩種穩態,即低電平穩態和高電平穩態。當輸入D為低電平時,輸出Q保持為低電平;當輸

d觸發器的邏輯功能 d觸發器sd和rd作用

D觸發器是一種常見的數字邏輯電路,它在數字系統和計算機中扮演著重要的角色。本文將詳細探討D觸發器的邏輯功能、工作原理以及RD(Reset-D

d觸發器是電平觸發還是邊沿觸發

D觸發器(Data Flip-Flop)是一種常見的數字邏輯電路元件,主要用于存儲一位二進制數據。D觸發器可以是電平觸發的,也可以是邊沿

t觸發器變為d觸發器的條件

在數字電路設計中,觸發器是一種非常重要的存儲元件,用于存儲一位二進制信息。觸發器的種類很多,其中最為常見的有JK觸發器、D觸發器和T

D觸發器變體來了,速看!

D觸發器變體來了,速看!

評論