最近接觸到TSMC的后端流程,其中關于基本單元的文件中提到了關于建立時間和保持時間的測量方法,現記錄一下自己的理解,目前我還是學生知識儲備有限,如果有不對還請同行們指正。

文件提到兩種setup/hold測量方式:10% push-up和pass/fail,按照TSMC說法,前者會更樂觀一些,因此如果是采用前者(10% push-up)的測量方式得到建立時間和保持時間,需要十份小心時序裕量是否足夠,最好人為添加margin。

以下為自己的理解:

10% push-up方式

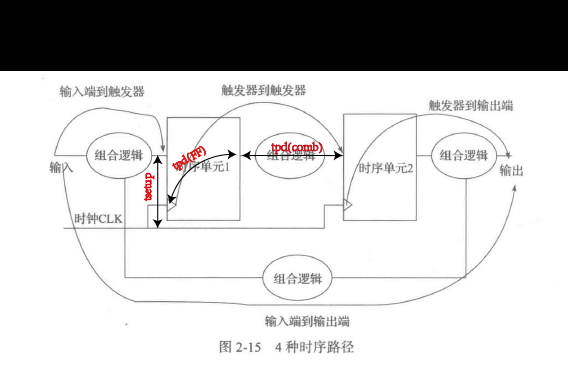

在上圖的reg-reg時序路徑,關于紅色信號: tsetup是為人為控制的值,通過調節該值測量建立保持時間;tpd(FF)為clock到Q的延時,該值會隨著D端信號的穩定時間的減小而增加; tpd(comb)是組合邏輯延時,為固定值。三個時間相加就是該路徑能運行的最快頻率。

tcycle = tpd(FF) + tpd(comb) + tsetup

上圖中,x軸為人為控制的tsetup,y軸為clock到Q的延時tpd(FF),當人為給定的tsetup很大時,tpd(FF)時間近似等于STA的時間,隨著tsetup時間越來越小,D端的數據穩定時間會“越來越短”,因此tpd(FF)的時間會增加(個人理解是因為亞穩態導致D端的數據不能穩定到固定的值),當tpd(FF)增加到原來的110%時,這時給的tsetup就會被認為是建立時間set up time。

pass/fail方式

而pass/fail是通過調整認為給定的setup/hold,去看輸出Q端的電壓波動,當電壓波動超過10%的臨界點,就被認為是建立時間/保持時間。

審核編輯:黃飛

-

TSMC

+關注

關注

3文章

177瀏覽量

84502 -

組合邏輯

+關注

關注

0文章

47瀏覽量

10041 -

電壓波動

+關注

關注

0文章

51瀏覽量

8026

發布評論請先 登錄

相關推薦

芯片設計進階之路—從CMOS到建立時間和保持時間

使用采樣保持技術實現運算放大器建立時間測定

建立時間和保持時間討論

保持時間與建立時間

為什么觸發器要滿足建立時間和保持時間

使用采樣保持技術實現運算放大器建立時間測定

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

關于建立時間和保持時間的測量方法

關于建立時間和保持時間的測量方法

評論