文章來源:半導體綜研 原文作者:關牮 JamesG

半導體芯片封裝的目的無非是要起到對芯片本身的保護作用和實現芯片之間的信號互聯。在過去的很長時間段里,芯片性能的提升主要是依靠設計以及制造工藝的提升。

隨著半導體芯片的晶體管結構進入到FinFET時代,工藝節點的進步呈現明顯的趨緩形勢。雖然根據行業的發展路線圖,工藝節點的迭代還有很大的上升空間,但我們能夠明顯感覺到摩爾定律的減緩,以及生產成本暴增帶來的壓力。

由此,通過改革封裝技術來進一步挖掘性能提升的潛力成為一個非常重要的手段。好幾年前開始,行業內就出現了通過先進封裝的技術來實現 “超越摩爾(More than Moore)”的口號。

所謂先進封裝,一般行業內的常用定義就是:所有利用前道制造的工藝方法的封裝技術。

通過先進封裝的手段,我們可以:

大幅度縮小封裝后芯片的面積

無論是多個芯片的合封,還是單個芯片的Wafer Level化封裝,都可以明顯降低封裝尺寸以減小整個系統板的使用面積。利用封裝手段縮小芯片面積在經濟上要比提升前道工藝來得更為劃算。

容納更多芯片的I/O端口數量

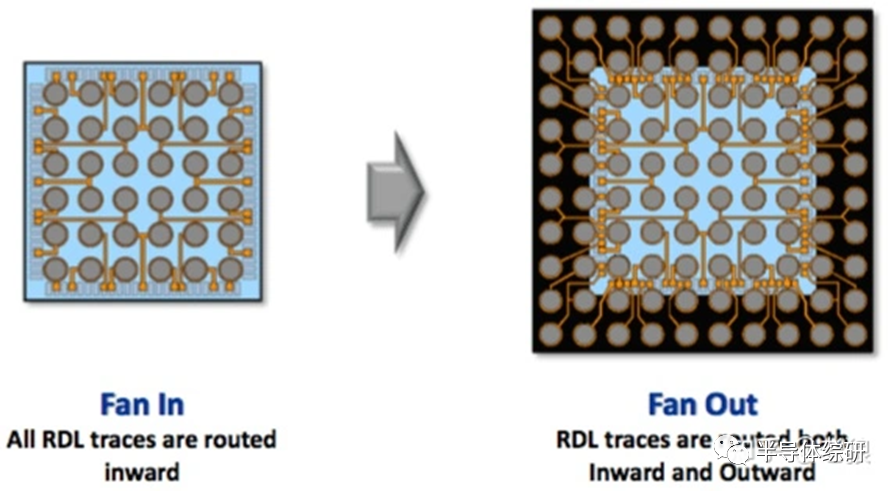

由于前道工藝方法的引入,我們可以利用RDL技術使得單位面積的芯片上能夠容納更多的I/O管腳,從而減少芯片面積的浪費。

降低芯片綜合制造成本

由于引入Chiplet的方案,我們可以比較容易地將多個不同功能、不同工藝技術/節點的芯片合封到一起,形成一個系統集成芯片(SIP)。這樣就可以避免所有功能和IP都必須采用同一種(最高工藝)的高成本方法。

提升芯片間的互聯能力

隨著大算力需求的提升,在很多應用場景里都需要計算單元(CPU、GPU...)和DRAM做大量的數據交換。這往往會導致整個系統幾乎有一半的性能和功耗浪費在信息交互上。現在我們通過各種2.5D/3D封裝,將處理器和DRAM盡可能近的連接在一起,就可以將這種損耗降低到20%以內,從而大幅度降低計算的成本。這種效率的提升遠遠超過了通過采用更先進制造工藝帶來的進步。

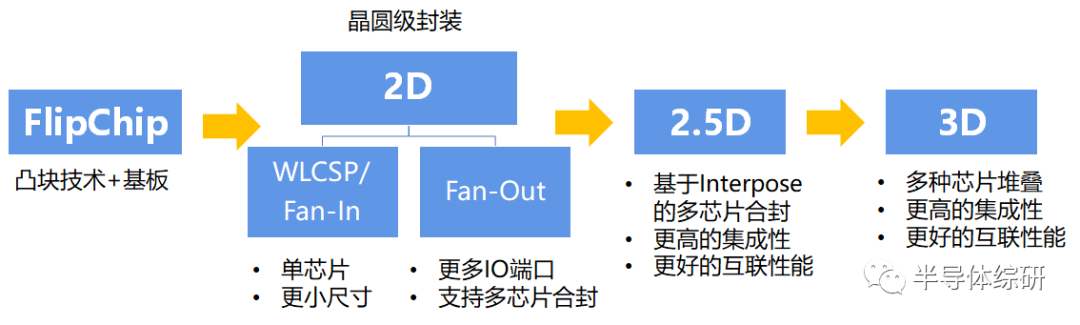

下圖是先進封裝技術的演進過程

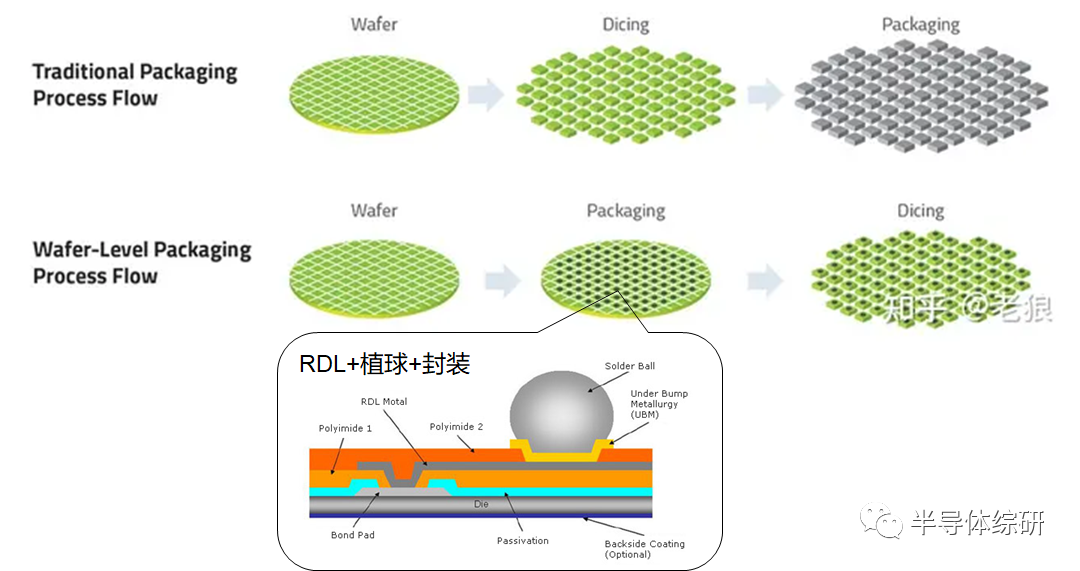

在Flipchip階段,封裝的方式還比較接近于傳統技術路線(我多數時候其實是把Flipchip當作傳統封裝來對待的)。 而從下圖可以看到,相對于傳統封裝,WLCSP(FanIn)的方法就和傳統有著明顯的區別:用前道技術直接對晶圓進行加工(RDL+凸塊)后再直接切割形成芯片。

而當芯片上的I/O端口越來越多,以至于芯片有限面積無法直接容納這么多管腳的時候,在原來WLCSP(Fan-In)的基礎上又發展出了FanOut技術:通過封裝材料擴大芯片面積來容納更多管腳。而且這樣一來,多芯片的合封也成為了可能。

當然,封裝技術的發展并未在此止步。隨著大算力芯片的技術和市場需求的高速發展,行業內又開始開發了2.5D和3D技術:

2.5D:通過Interposer(通常以硅基板為主要材料)將處理器和HBM(High Bandwidth Memory)進行高密度和高效率互聯。其中最有名的就是最近因為人工智能而火出圈的臺積電的CoWoS封裝技術。

3D:直接將不同芯片在Z軸方向上堆疊,通過TSV等方法實現更高效率互聯。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50908瀏覽量

424486 -

半導體

+關注

關注

334文章

27475瀏覽量

219565 -

封裝

+關注

關注

126文章

7935瀏覽量

143072 -

晶體管

+關注

關注

77文章

9702瀏覽量

138422 -

先進封裝

+關注

關注

2文章

413瀏覽量

257

原文標題:我們為什么需要了解一些先進封裝?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

多芯片整合封測技術--種用先進封裝技術讓系統芯片與內存達到高速傳輸

一圖了解頻率控制技術的演進

哪一種芯片不屬于 FPGA 的演進過程中的芯片類型

CDMA技術分階段向LTE演進過程

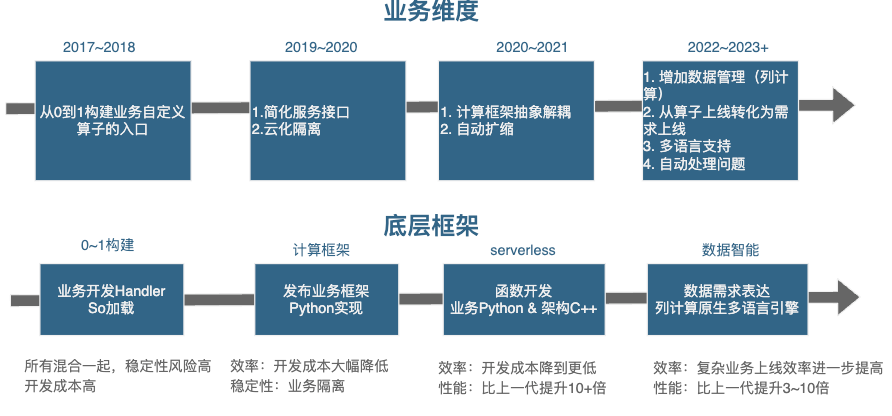

云服務架構的演進過程

淺談關于云服務架構的演進過程

從2G到5G,核心網的演進過程和思路解析

5G核心網演進過程與現存問題分析

區塊鏈的核心技術挖礦演進詳細資料說明

SaaS的演進過程(SaaS,PaaS和IaaS及特點)

百度垂類離線計算系統的演進過程 百度垂類離線計算系統的設計與實現

先進封裝技術的演進過程

先進封裝技術的演進過程

評論