看到這個題目,可能不少朋友都會滿臉問號,我們知道cell內部會有leakage,難道cell與cell之間也會有leakage嗎?對,沒錯,今天就想稍微講解一下這個問題,以便于我們后端理解cell中一些奇怪的工藝。

首先,所謂漏電流,就是指管子不導通的時候流過的電流,即pn結在反向截止狀態時,也會有一個很微弱的電流流過,我們就稱之為leakage。

對于MOS管來說,它的source、substrate、drain中總會存在一個這樣的leakage。那么相鄰cell的leakage是如何產生的呢?這就要從layout的工藝開始講起了。

不知道大家了不了解這些源漏摻雜是如何產生的,其實,工藝的順序是:首先鋪一層襯底,就以NMOS為例好了,先鋪一層P襯底,而后通過一些刻蝕沉積之類的方法,標定源漏的位置,然后在這些位置注入n離子,或者說注入電子,形成n well,對于p well就是注入p離子。

這里我就說的不太嚴謹了,應該就是注入某種材料,總之得到我們的n區p區。我們把這個能注入離子的區域稱為有源區,或者叫擴散區,有的fab會稱為OD(oxide diffusion)。

如果這個NMOS管旁邊還有個NMOS管,這兩個管子分別屬于不同的cell的話,最傳統的做法是分別來做,它們的OD是各自獨立的,兩個OD之間應該會是其他的材料。

注意,這里對于同一個cell里面可能會有許多MOS管,它們的OD是連在一起的,而cell與cell之間的OD是分開的。

那么cell間的漏電流就很好理解了,就是指分屬不同OD的n區p區之間產生的漏電流。由于兩個cell的OD并不相連,它們之間的leakage非常非常小,幾乎無限接近于0。

然而以上的layout設計會有一個弊端,就是為了分割不同的OD,必須要把cell做的很大,cell的邊界要留有一定的空間才行。

要知道PPA中的A-area是我們追求的目標,如何能把cell做的更小一點呢?后來人們提出了CNOD技術(continuous OD),意思是做cell的時候就不把相鄰cell的有源區分開了,讓他們連在一起好了,沒有了中間空隙的要求,這樣就大大降低了cell的面積。

那么,代價是什么呢?沒錯,就是會增大cell之間的漏電流。人們為了再減弱這部分漏電流,一般會在連在一起的那部分OD里注入一些奇怪的材料。具體我也不知道是啥了。

后來人們還是覺得這部分cell間leakage過大,又提出了PODE技術(poly over OD edge)。這個我就了解不多,說錯見諒。它是指在OD的邊緣上面蓋一層poly finger,可以有效減小漏電流,并且相鄰cell的OD間距也能大幅縮小。

對于FinFET來說想像起來就比較直觀,相鄰cell的兩個fin就被一塊poly阻隔了(FinFET鰭式場效應管,之后可能會專門寫文章來聊)。

后來人們為了進一步壓縮面積,又又又來了CPODE,即common PODE,意思是相鄰的cell就不需要每個人出一個poly了,兩個人公用一塊poly就可以了,漏電流也不會變大,而面積就省下來了一部分。在芯片界,作為人類最高技術的代表,即使只是為了那么一點點的改善,也要付出巨大的努力。

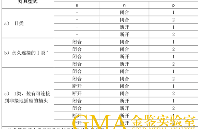

說了這么多,其實作為后端工程師,實際工作中也不會用到。只是明白有的cell會標注CPD(CPODE)、CNOD這樣的字眼,就代表了這些cell用到了相應的技術。

-

場效應管

+關注

關注

46文章

1162瀏覽量

63940 -

MOS管

+關注

關注

108文章

2418瀏覽量

66827 -

Layout

+關注

關注

14文章

404瀏覽量

61773 -

漏電流

+關注

關注

0文章

262瀏覽量

17024 -

FinFET

+關注

關注

12文章

248瀏覽量

90230

發布評論請先 登錄

相關推薦

什么是泄漏電流試驗?

醫用漏電流測量裝置(YC9706-MD-N)漏電流的測試 深圳一測

電容器漏電流測試原理是什么

什么是漏電流,漏電流和陶瓷電容有什么關系?

layout相關—芯片中相鄰單元的漏電流

layout相關—芯片中相鄰單元的漏電流

評論