半導體器件的制造由許多步驟組成,這些步驟必須產(chǎn)生定義明確的結(jié)構(gòu),并且從一個器件到下一個器件的偏差很小。每一步都必須考慮之前和隨后的制造步驟,以確保實現(xiàn)所需的高制造質(zhì)量。大多數(shù)過程都是在真空腔室中通過引入不同的氣態(tài)化學物質(zhì)進行的,這些化學物質(zhì)通過與基材反應來改變表面。IC最小特征的形成被稱為前端制造工藝(FEOL),本文將集中簡要介紹這部分,將按照如下圖所示的 22 nm 技術(shù)節(jié)點制造 FinFET 的工藝流程,解釋了 FEOL 制造過程中最重要的工藝步驟。

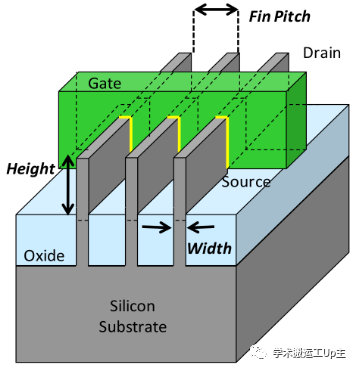

22 nm 技術(shù)節(jié)點的 FinFET圖示(分別具有單個柵極和三個源極和漏極觸點)

下面給出最重要的制造步驟的圖示, FinFET制造的FEOL步驟通常類似于以下內(nèi)容:

- 起始過程一般從清潔和拋光的晶體硅晶片開始。

- 光刻:為了形成未來的導電通道,即鰭片(fin),使用光刻技術(shù)制造掩模,其中只有某些區(qū)域被掩模材料覆蓋。平版印刷工藝具有最大分辨率,這取決于所用光的波長。常用的193 nm波長的紫外光可以達到的最小尺寸約為30 nm。為了實現(xiàn)更小的特征,使用了自對準雙圖案化(SADP),通過使用化學氣相沉積(CVD)各向同性地沉積薄層來產(chǎn)生更小的掩模。然后使用反應離子蝕刻 (RIE) 定向蝕刻該薄層,留下沉積材料的薄柱,然后用作掩模,如下圖所示:

SADP掩模版在Si襯底上

使用生成的柱子作為初始掩碼再次重復此過程稱為四重圖案 (QP)。為了避免這些復雜的多重圖案化技術(shù),一些制造商已經(jīng)實現(xiàn)了極紫外(EUV)光刻技術(shù)。

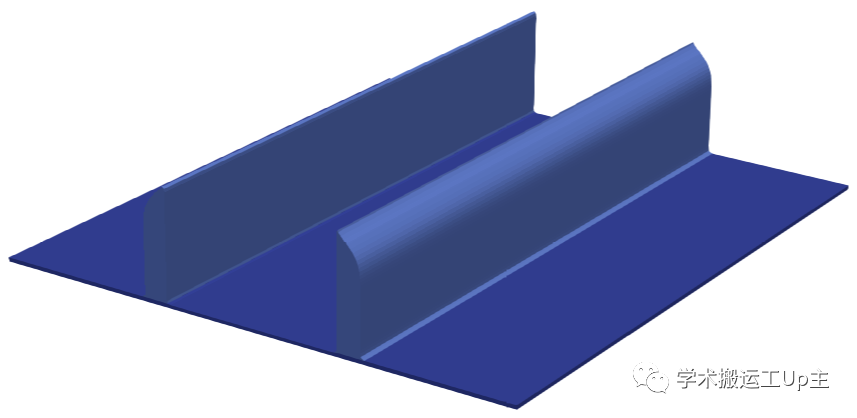

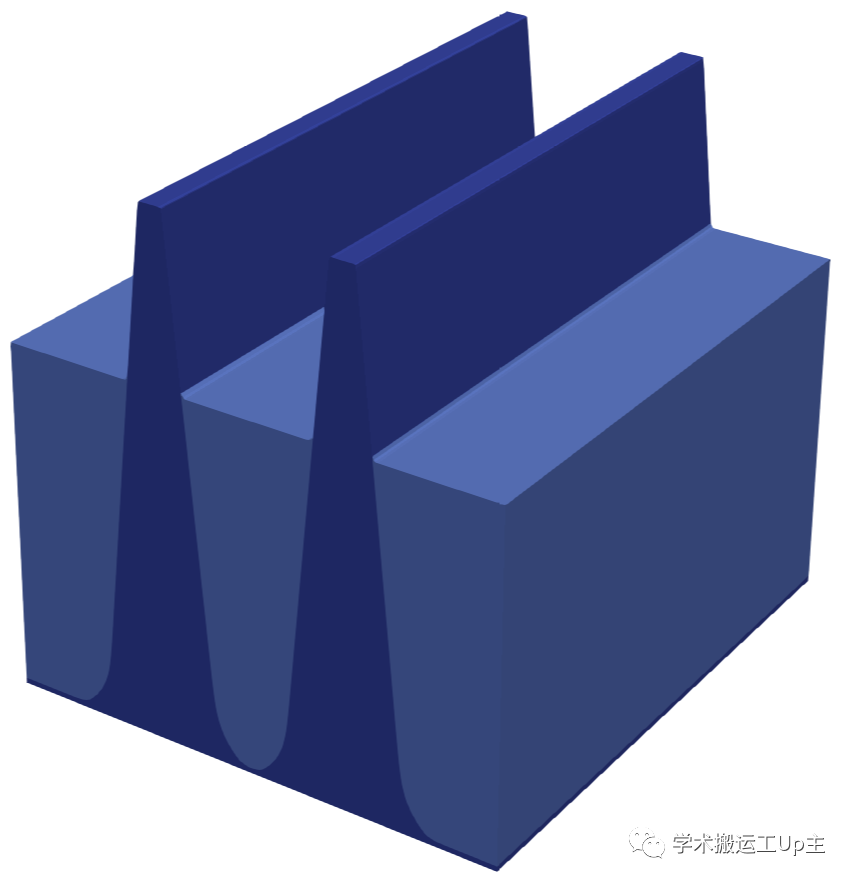

- fin圖案化:在這個階段,晶體硅襯底被蝕刻,在掩模下方留下fin,隨后形成MOSFET的導電溝道。如下圖所示,對蝕刻過程進行調(diào)整,使fin呈正錐形,從而向底部增加寬度。

硅fin通過刻蝕硅實現(xiàn)

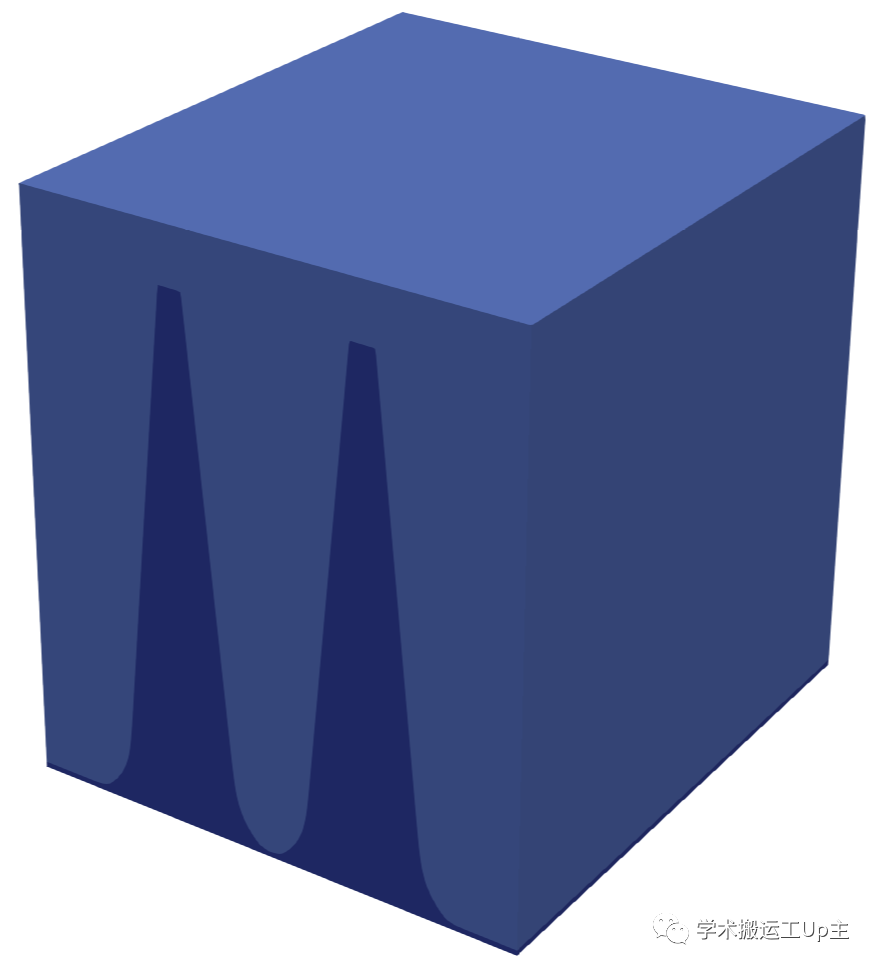

- 淺溝槽隔離 (STI):由于每個fin可能是不同晶體管的一部分,因此它們必須相互電絕緣。這是通過在各處沉積介電材料來實現(xiàn)的。然后使用化學機械平坦化 (CMP) 對晶圓進行拋光,以創(chuàng)建如下圖所示的平坦化頂面。

STI沉積以電絕緣不同fin

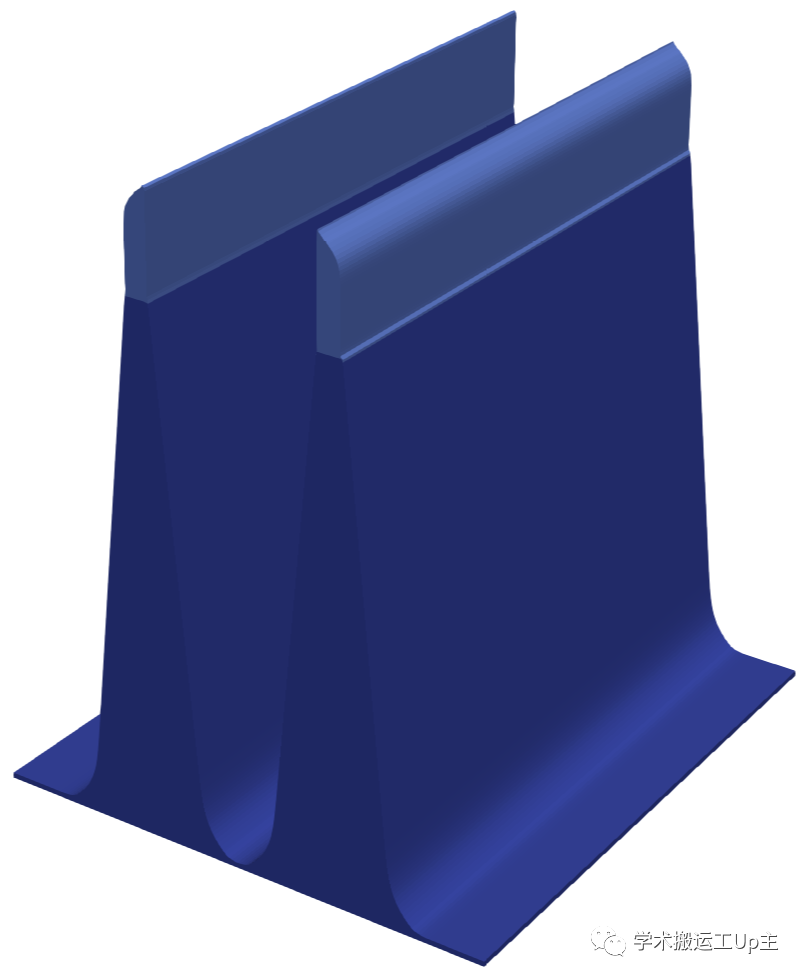

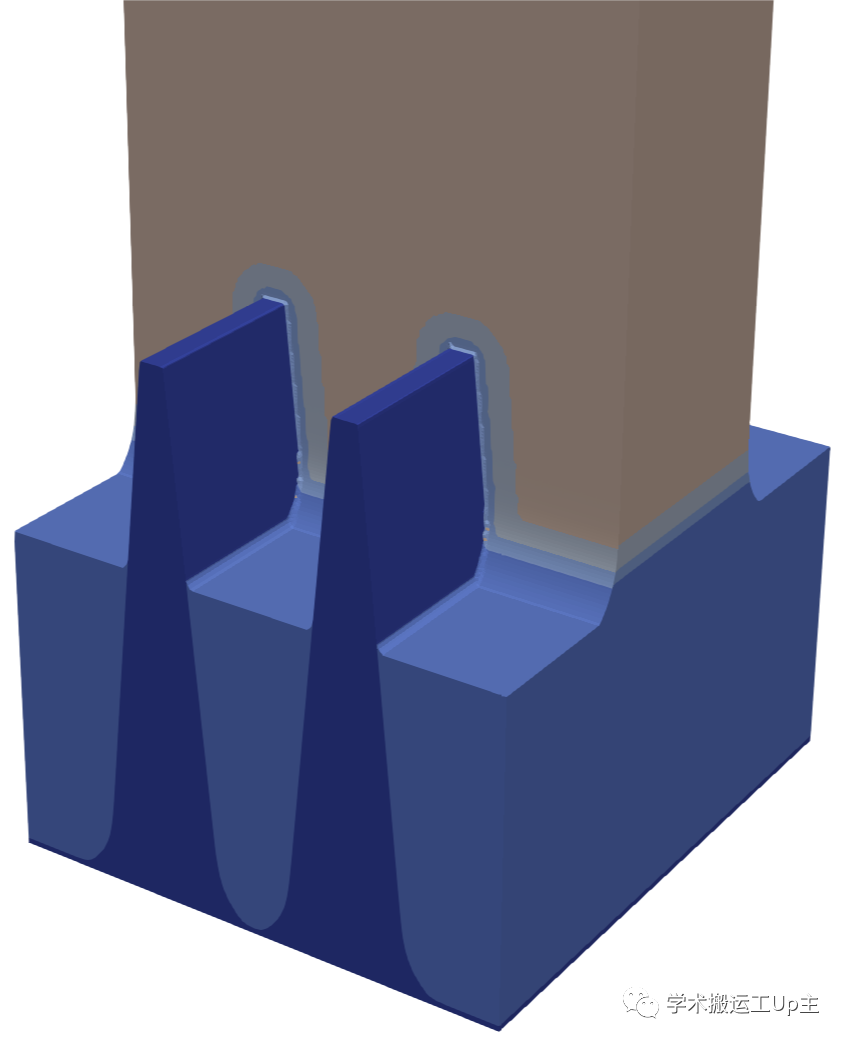

- fin釋放:一旦表面拋光,就可以選擇性地蝕刻介電材料,使晶體硅完好無損。因此,fin再次被釋放并伸出介電材料,如下圖所示,同時彼此隔離到足夠的深度。

fin被釋放以實現(xiàn)柵極與硅接觸

- 金屬柵極沉積:高介電常數(shù)金屬柵極通常由三種不同材料的堆疊組成:fin周圍具有高介電常數(shù)的薄層材料,通常表示為 κ,因此得名 high-k; 另一層稍厚的金屬,稱為柵極金屬; 最后是一層更厚的柵極接觸材料,通常是多晶硅(poly-Si)。這些材料使用CVD或原子層沉積(ALD)進行沉積。

- 柵極圖案化:在柵極接觸材料的頂部,使用光刻技術(shù)創(chuàng)建另一個掩模。然后對柵極材料一個接一個地進行蝕刻,使柵極僅覆蓋硅fin的中心部分,如下圖所示。

柵極沉積及圖案化

- 柵極間隔物(Spacer):為了將柵極與源極和漏極 (S/D) 區(qū)域電氣隔離,使用 CVD 各向同性沉積間隔物介電材料。與SADP類似,RIE隨后將其定向去除,僅將聚合物留在澆極材料的側(cè)面。從下圖中可以看出,RIE不具有選擇性,并且在此制造步驟中硅fin也會被侵蝕。

柵極spacer沉積以電絕緣S/D

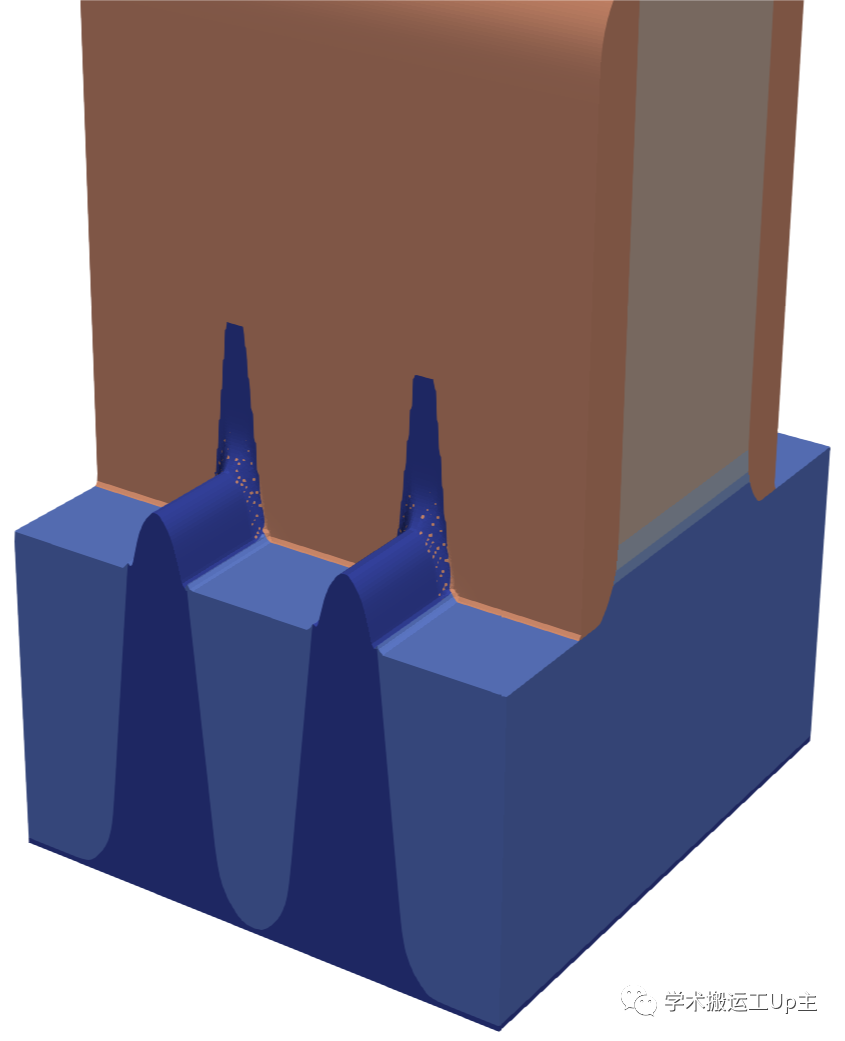

- fin凹槽:然后對硅fin進行蝕刻,以便清潔它們,為后續(xù)過程做準備,導致介電材料墊片下方的fin蝕刻不足,如下圖所示。

硅fin被刻蝕成凹槽

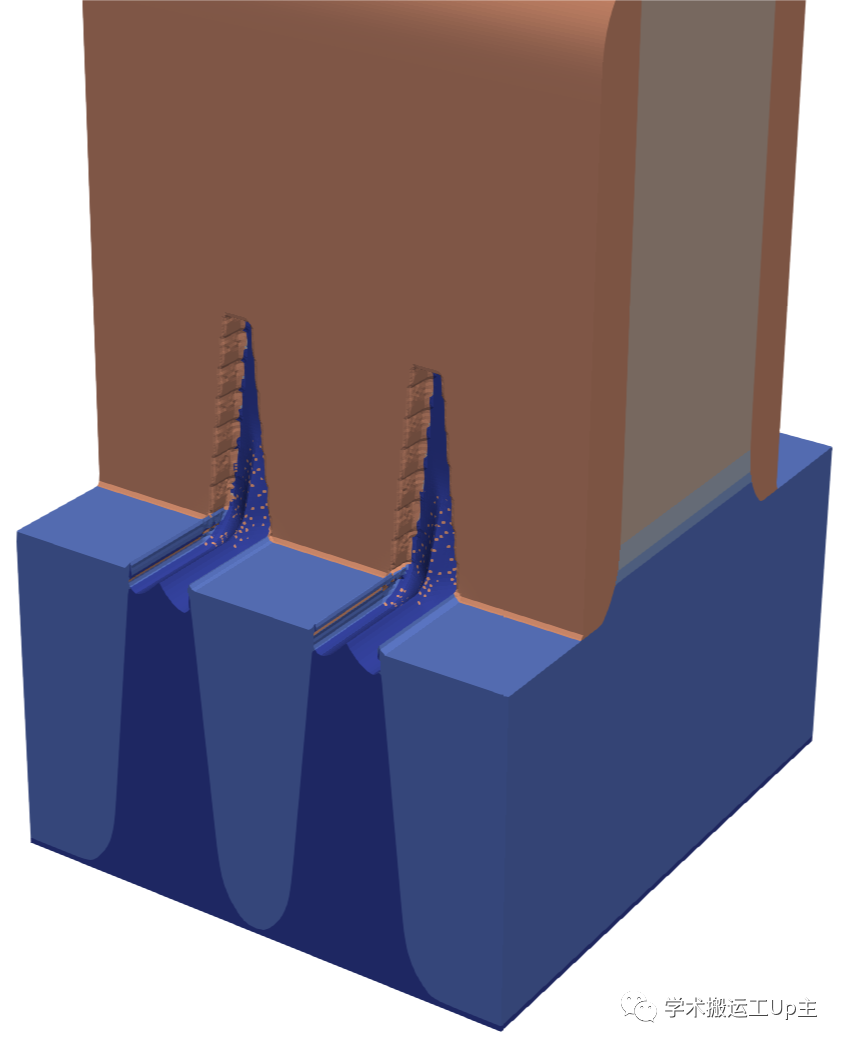

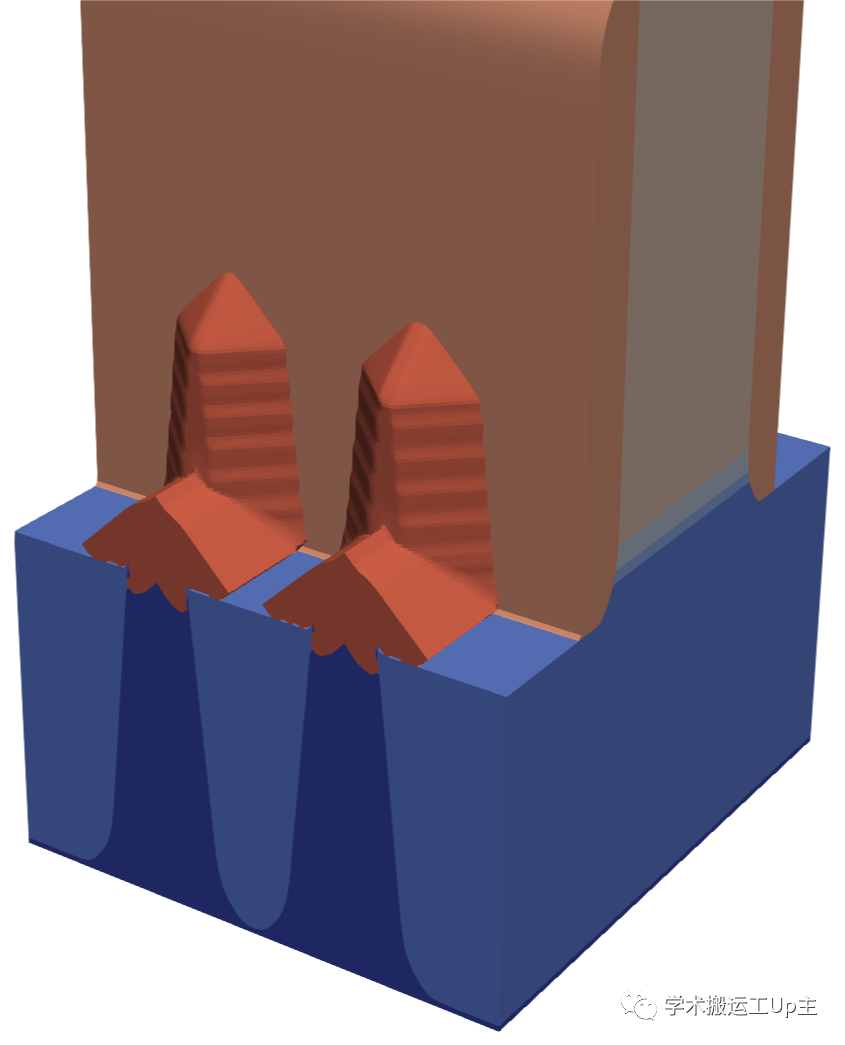

- 源極和漏極外延:現(xiàn)在已經(jīng)清潔了fin表面,可以使用外延生長創(chuàng)建晶體 S/D 觸點。這種生長速率隨晶體方向變化很大,導致在如下圖中觀察到的特征金剛石形狀。

S/D 外延

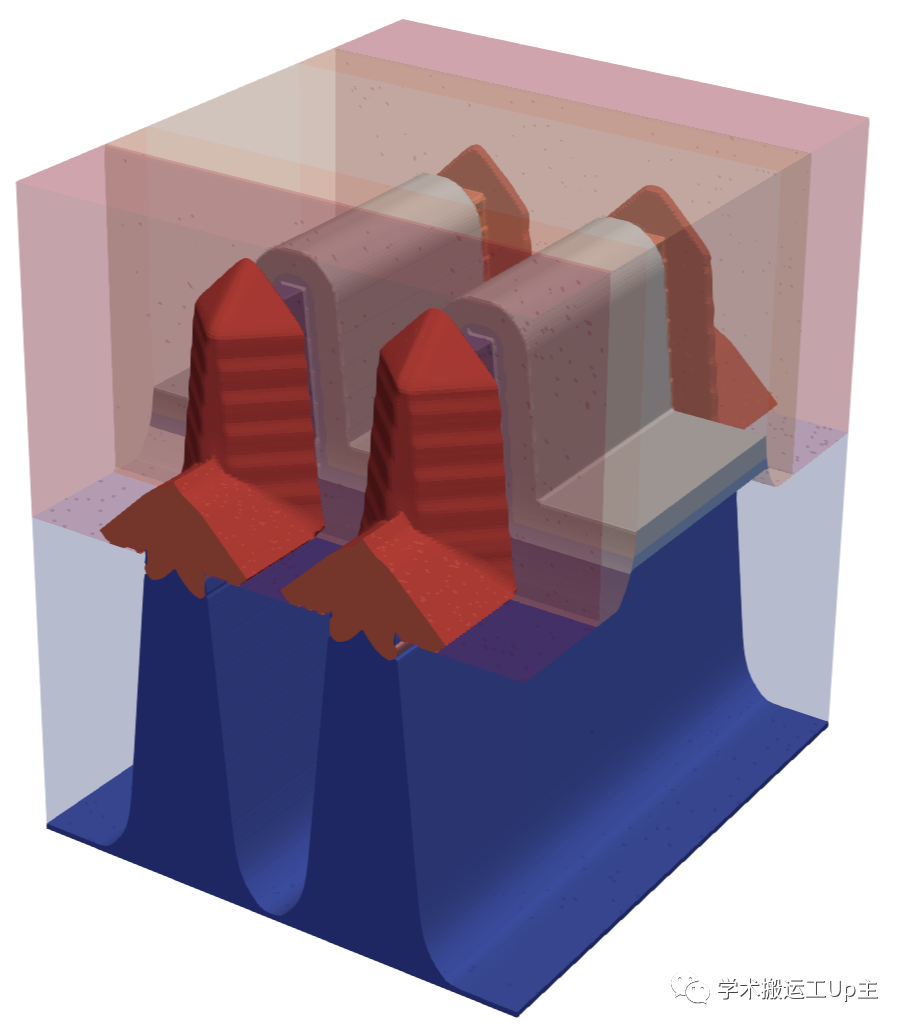

- 層間介電材料:在使用CMP拋光晶圓之前,沉積另一層介電材料以隔離S/D觸點,從而產(chǎn)生如下圖所示的最終MOSFET結(jié)構(gòu),完成FEOL制造。

FinFET的最終結(jié)構(gòu)

FEOL步驟完成后,所有晶體管在工藝金屬化過程中連接以形成電路,這是半導體制造工藝后端(BEOL)的一部分。這是分幾層進行的,每層的關鍵尺寸都會增加,最終提供足夠大的金屬觸點,以將IC連接到外圍元件。單個晶圓可能包含數(shù)百個同時制造的芯片。由于現(xiàn)在所有晶體管和互連都已形成,因此晶圓可以切割成單個芯片。然后,每個芯片都有適合特定應用的轉(zhuǎn)接板(interposer)以完成最后的封裝工藝。

-

制造工藝

+關注

關注

2文章

179瀏覽量

19757 -

22nm

+關注

關注

0文章

51瀏覽量

18007 -

工藝流程

+關注

關注

7文章

106瀏覽量

16284 -

半導體器件

+關注

關注

12文章

752瀏覽量

32050 -

FinFET

+關注

關注

12文章

248瀏覽量

90230

發(fā)布評論請先 登錄

相關推薦

聯(lián)電宣布22nm技術(shù)就緒

透視IVB核芯 22nm工藝3D技術(shù)終極揭秘

22nm平面工藝流程介紹

銳成芯微宣布在22nm工藝上推出雙模藍牙射頻IP

液晶顯示器制造工藝流程基礎技術(shù)

Intel 22nm光刻工藝背后的故事

臺積電又跳過22nm工藝 改而直上20nm

Achronix全球首款22nm FPGA,瞄準高端通信市場

現(xiàn)代集成電路芯片14nm節(jié)點FinFET的制造工藝流程詳細資料說明

22nm技術(shù)節(jié)點的FinFET制造工藝流程

22nm技術(shù)節(jié)點的FinFET制造工藝流程

評論