本文翻譯轉載于:Cadence blog

作者:Reela

在身處技術驅動的大環(huán)境中,半導體設計需要做到更迅速、更節(jié)能以及更穩(wěn)健。為了滿足這一需求,半導體制造企業(yè)需要不斷突破技術創(chuàng)新。通過對更多參數(shù)及其影響的分析,客戶才能實現(xiàn)較現(xiàn)行設計方法更優(yōu)秀的 PPA 目標。例如,全局額定值或全局的裕度會造成性能和功耗的顯著浪費。

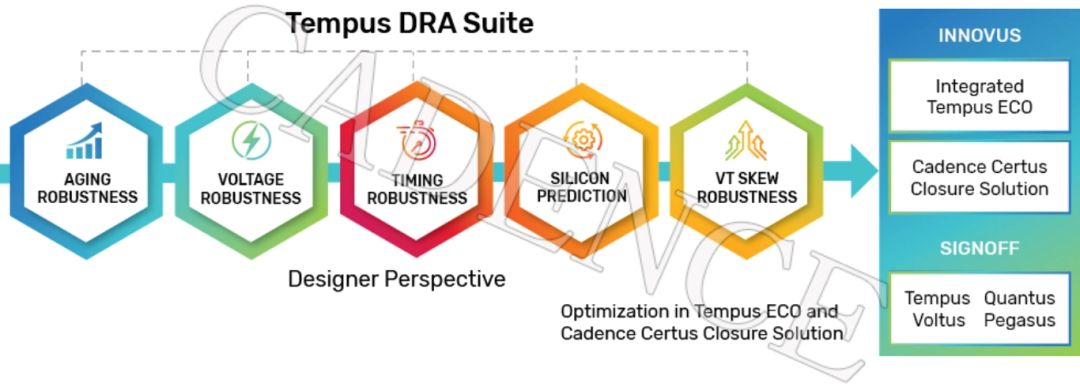

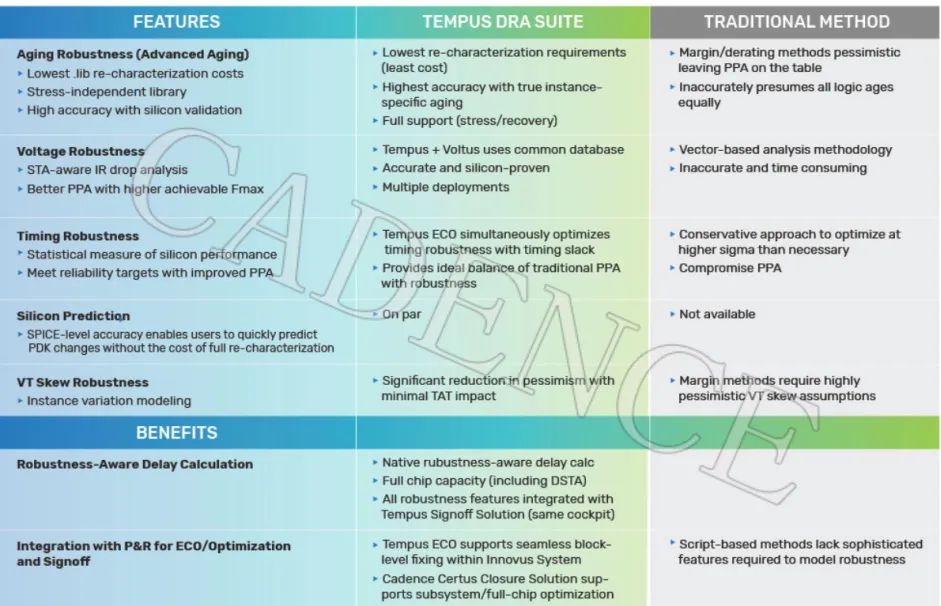

為了應對類似挑戰(zhàn),Cadence 持續(xù)創(chuàng)新并開發(fā)了 Cadence Tempus 設計穩(wěn)健性分析(DRA)套件,提供解決上述問題所需要的分析能力。該套件采用先進的建模算法,賦能工程師分析,識別并糾正對變化極為敏感的關鍵設計要素,包括適用于模塊級的 Tempus ECO Options 和子系統(tǒng)/全芯片級的 Cadence Certus 收斂解決方案,兩者皆可在 Innovus 設計實現(xiàn)系統(tǒng)中調用。通過充分發(fā)揮套件的高級分析特性,客戶可以強化設計穩(wěn)健性,優(yōu)化功耗、性能和面積(PPA)目標,較傳統(tǒng)基于裕度的方法實現(xiàn)最高達 10% 的 PPA 目標提升。

TempusDRA 套件

Tempus DRA 套件集合了卓越的分析能力,針對老化效應、電壓降和閾值電壓偏斜等不同類型的時序偏差,解決設計層的穩(wěn)健性問題。該套件包括 5 種高級分析能力,分別適用于穩(wěn)健半導體設計的特定流程。

老化穩(wěn)健性

01

Tempus DRA 套件以其卓越的老化穩(wěn)健性分析能力在業(yè)界獨樹一幟,PPA 目標最高可提高 10%,適用于汽車、航空航天、消費者電子、移動設備和大規(guī)模計算等領域。該套件允許工程師在 Cadence Liberate Library 表征化流程工具內控制老化表征環(huán)境及參數(shù),提供老化環(huán)境的完整分析結果,并通過統(tǒng)計學圖表直觀呈現(xiàn)應力和恢復狀態(tài)。

與老化感知時序和限制結合,老化穩(wěn)健性可以實現(xiàn) SPICE 級精度的卓越 PPA 結果。在臺積電 TMI 和其他 SPICE 可靠性模型的支持下,可以跟蹤任意場景下的靜態(tài)時序分析(STA)、實例老化、非統(tǒng)一老化及恢復模型選擇,并且能調節(jié) STA 的最優(yōu)設置。得益于此,老化效應導致的非必要延遲被清除,進一步加速設計收斂。

電壓穩(wěn)健性

02

電壓穩(wěn)健性分析與 Tempus 電源完整性(PI)和 Voltus IC 電源完整性解決方案無縫集成,大幅提升了現(xiàn)有的簽核解決方案。該集成采用了新一代(IR)壓降分析和修復技術。電壓穩(wěn)健性分析通過 Tempus ECO Option 實現(xiàn)修復流程的自動化,并通過優(yōu)化 Victim 及 Aggressor 信號路徑解決壓降問題。值得注意的是,該分析可以識別傳統(tǒng) IR 壓降簽核方法容易忽略的時序違例,防止可能導致高昂成本硅片失效的發(fā)生。最大 IR 壓降設計裕度的降低也可以幫助實現(xiàn)更優(yōu)的 PPA 目標。

時序穩(wěn)健性

03

時序穩(wěn)健性分析是 Tempus DRA 套件的第三項分析能力。這項強大的能力可以通過對硅片性能的統(tǒng)計學測量而達到時序的準確性,在符合 Sigma 可靠性要求的同時顯著提高設計 PPA。其用戶友好的界面可以加速設計局部更改(ECO)流程,提供相較于傳統(tǒng) SPICE 蒙特卡洛分析更直截了當?shù)姆椒ā?/p>

硅預測

04

硅預測是 Tempus DRA 套件的第四項分析能力,專注于硅片特性的持續(xù)調優(yōu),可以對硅片的設備模型、庫和目標設備模型提供快速反饋,幫助設計工程師對設計進行快速調整。硅預測支持包括 PBA(物理設計、構建和分析),GBA(全局構建與分析)等設計的各個階段,并在 Tempus 時序解決方案、Tempus ECO Option 和 Innovus 設計實現(xiàn)系統(tǒng)中可用。

設計工程師可以用硅預測功能建立模型與硬件的相關性,獲得理想的硅片性能,并在 Tempus 時序和 Liberate 表征化流程期間實現(xiàn)精準的統(tǒng)計學建模,在硅前靜態(tài)時序分析(STA)簽核時識別離散參數(shù)。該分析能力可以賦能設計團隊,助其達成確鑿的收斂和優(yōu)化,利用硅預測預判延遲,并提高 PPA 和良率。

電壓閾值偏斜穩(wěn)健性

05

電壓閾值(VT)偏斜穩(wěn)健性是 Tempus DRA 套件的第五項分析能力,用于應對目前 STA 方法固有的時序悲觀。Tempus DRA 套件幫助工程師更靈敏的分析 TT(溫度和電壓)corners,為每個 VT 類型執(zhí)行快速降額以將延遲優(yōu)化至慢 corners 和快 corners(SSG 和 FFG)。設計師可以將庫與 VT 類型捆綁,為每個 VT 類型定義慢和快降額。Tempus DRA 套件可以執(zhí)行優(yōu)化排列,并根據(jù) VT 類型的啟動和捕捉路徑找出最差的松弛變量。

Tempus DRA 套件是一套高級分析能力的完整合集,致力于增強設計層穩(wěn)健性,對比傳統(tǒng)方法實現(xiàn)更卓越的 PPA 提升。得益于其對老化穩(wěn)健性、電壓穩(wěn)健性、時序穩(wěn)健性、硅預測和 VT 偏斜穩(wěn)健性的專注,該套件可以助力設計團隊在快速迭代的技術環(huán)境下創(chuàng)建更高效、可靠、具有競爭力的半導體解決方案。這是實現(xiàn)新一代半導體設計的關鍵一步。

Tempus DRA 套件是廣泛 Cadence 數(shù)字與簽核工作流程的組成部分,支持 Cadence 智能系統(tǒng)設計戰(zhàn)略,助理實現(xiàn)卓越的片上系統(tǒng)(SoC)設計。

點擊文末“閱讀原文”,了解更多 Tempus 時序解決方案的高級分析特性。

關于 Cadence

Cadence 是電子系統(tǒng)設計領域的關鍵領導者,擁有超過 30 年的計算軟件專業(yè)積累。基于公司的智能系統(tǒng)設計戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念成為現(xiàn)實。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計算、5G 通訊、汽車、移動設備、航空、消費電子、工業(yè)和醫(yī)療等最具活力的應用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產品。Cadence 已連續(xù)九年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版權所有。在全球范圍保留所有權利。Cadence、Cadence 徽標和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標志均為 Cadence Design Systems, Inc. 的商標或注冊商標。所有其他標識均為其各自所有者的資產。

-

Cadence

+關注

關注

65文章

926瀏覽量

142296

原文標題:Tempus DRA 套件加速先進節(jié)點技術

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

為DRA71x、DRA79x和TDA2E-17供電的LP8733-Q1和LP8732-Q1用戶指南

TPS659039-Q1為DRA74x、DRA75x、TDA2x和AM572x供電的用戶指南

CoWoS先進封裝技術介紹

DRA74x、DRA75x和DA2x系列設備的服務質量(QoS)旋鈕

如何在DRA821U上使用Linux實現(xiàn)快速引導

DRA75x、DRA74x信息娛樂應用處理器器件版本2.0數(shù)據(jù)表

DRA75xP、DRA74xP信息娛樂應用處理器芯片版本1.0數(shù)據(jù)表

DRA77xP、DRA76xP信息娛樂應用處理器芯片版本1.0數(shù)據(jù)表

DRA829 Jacinto?處理器數(shù)據(jù)表

DRA821 Jacinto?處理器數(shù)據(jù)表

CDN節(jié)點是什么

IMEC推出針對N2節(jié)點的設計探路PDK

Tempus DRA 套件加速先進節(jié)點技術

Tempus DRA 套件加速先進節(jié)點技術

評論