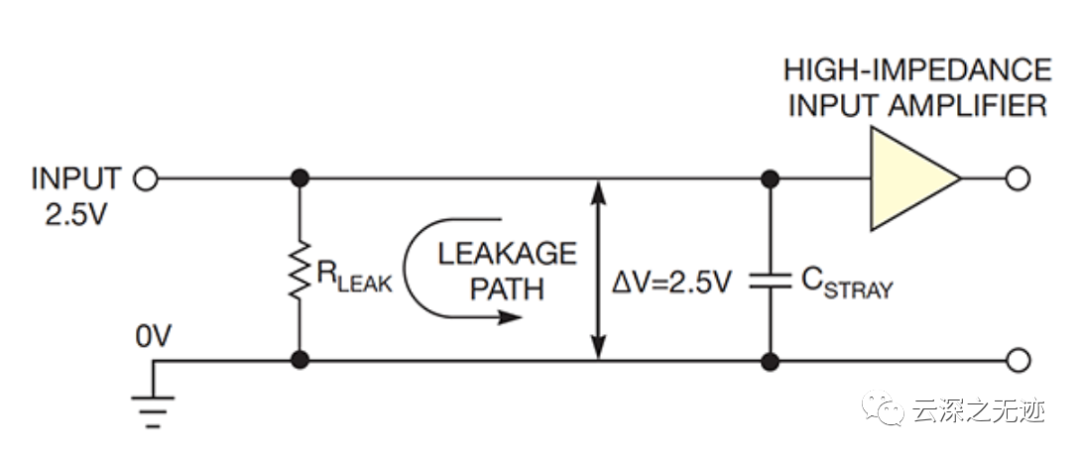

本文的第 1 部分定義并描述了承載這些低電流的設(shè)計(jì),解釋了設(shè)計(jì)這些電路時(shí)出現(xiàn)的問(wèn)題,并研究了屏蔽和防護(hù)方法的應(yīng)用。

第 2 部分研究你的元件選擇如何影響低泄漏電路的性能,并討論噪聲如何滲透到低泄漏設(shè)計(jì)中。

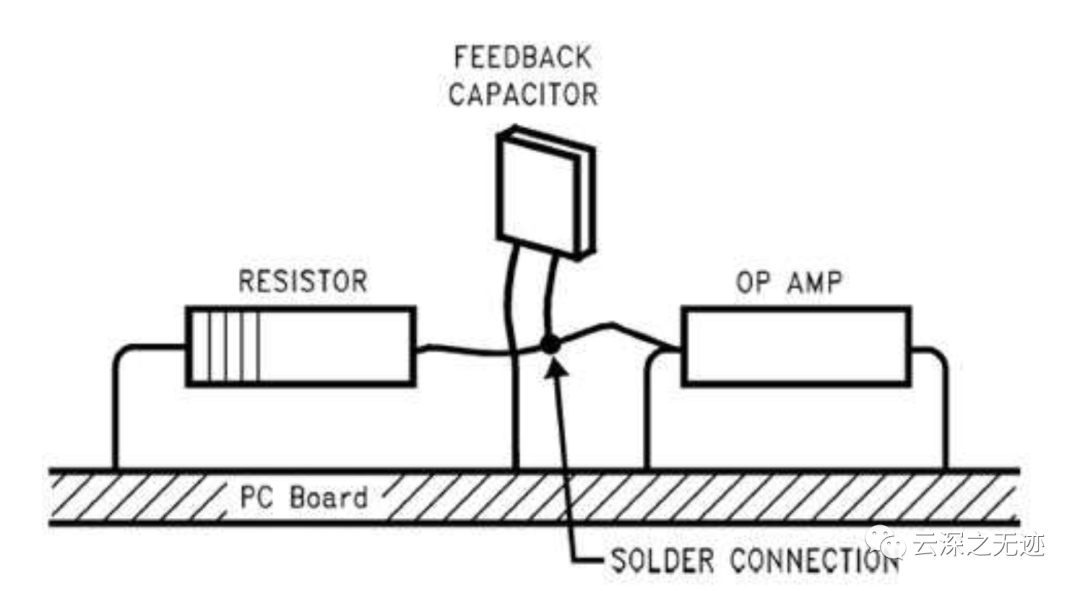

經(jīng)典的低電流技術(shù)是“空中”布線技術(shù),其中關(guān)鍵路徑或電路節(jié)點(diǎn)中的組件引線在電路板上方焊接在一起。這些元件引線和走線不與電路板接觸,因此有效消除了PC板的影響。 Teflon 支座端子可用于支撐大型組件或人口密集的節(jié)點(diǎn)。組件下方的區(qū)域應(yīng)該是堅(jiān)固的、裸露的防護(hù)平面。

圖 1:空中布線

該技術(shù)提供了最低的泄漏、最低的雜散電容和最佳的整體低電流性能,但需要手工組裝,并且在大規(guī)模生產(chǎn)或有限的空間區(qū)域中不容易實(shí)現(xiàn)。整個(gè)電路不必放置在電路板上方,只需放置關(guān)鍵節(jié)點(diǎn)即可。在上面的圖 1 中,電路的反相節(jié)點(diǎn)(包括輸入信號(hào)、反饋電阻和電容器)都直接焊接到運(yùn)放反相端子的彎曲腿上。 使用雙通道的第二個(gè)通道 這里有一個(gè)小技巧:如果你正在設(shè)計(jì)使用非反相配置的電路,請(qǐng)使用雙通道的第二個(gè)(“B”)通道作為主放大器。

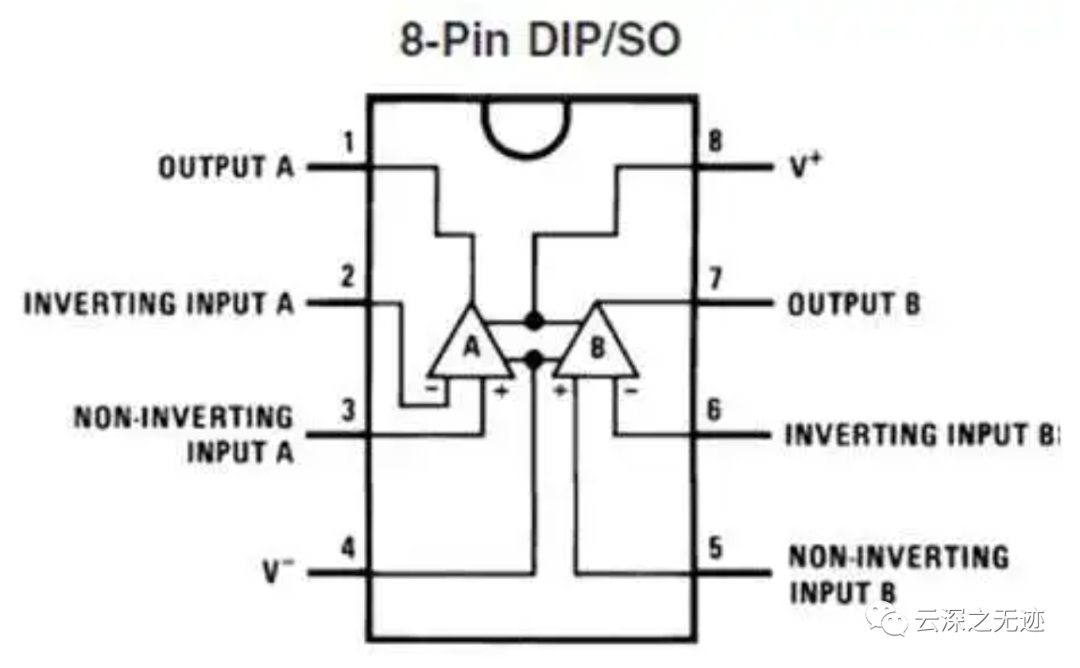

圖 2:標(biāo)準(zhǔn)雙運(yùn)放引腳排列

在標(biāo)準(zhǔn)雙引腳排列中,“B”同相輸入距離負(fù)電源引腳較遠(yuǎn),并且也受到反相引腳向北“保護(hù)”,并且輸入位于封裝的一角,以便于安裝與源的連接。在 V- 和“B”非反相引腳之間還有更多的空間來(lái)運(yùn)行保護(hù)走線。“A”通道放大器可用作保護(hù)驅(qū)動(dòng)器。 單引腳排列遇到與“A”通道相同的問(wèn)題,其中非反相輸入靠近電源。除了微小的單選項(xiàng)之外,如果單版本和雙版本都采用相同的 8 引腳封裝,則使用雙版本可能更有利。 小包裝可能不太好…

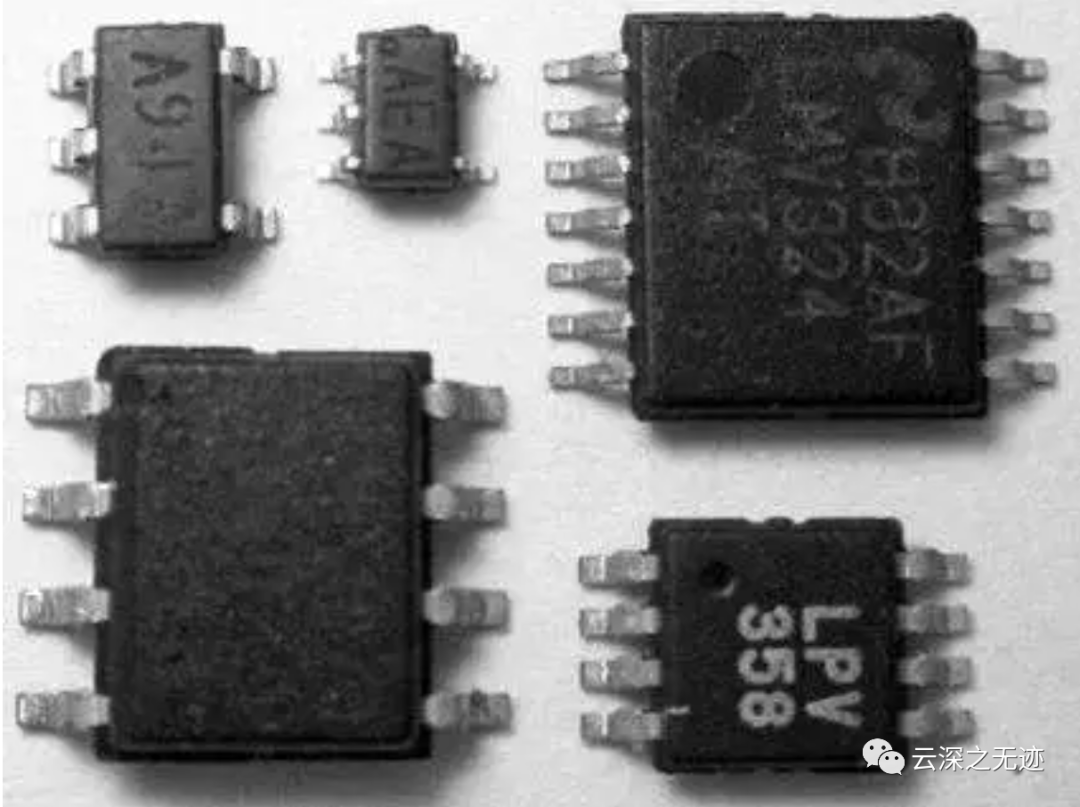

圖 3:小型封裝比較(頂行)SOT-23、SC-70、TSSOP-14,(底行)SOIC-8 和 MSOP-8 引線間距較窄的封裝往往具有較高的泄漏。這主要是因?yàn)橐€間距很小并且更靠近電源線和其他引腳。電路板每平方的電阻率保持不變,但將焊盤移得更近會(huì)縮短距離,從而降低電阻率。 此外,更緊密的螺距會(huì)更快地積聚污垢,并且在這些緊密的螺距下更難以正確清潔。如果空間不是很寶貴的話,這是 SOIC-8 比 MSOP-8 更好的少數(shù)情況之一。舊的DIP封裝仍然是這方面最好的封裝。出于同樣的原因,SOT-23 單路優(yōu)于 SC-70 單路。 設(shè)計(jì)和布局建議以下是自己的設(shè)計(jì)時(shí)需要牢記的一些一般性建議。 保護(hù)走線應(yīng)圍繞所有輸入級(jí)。內(nèi)層和底層也保護(hù)PC板。輸出不需要保護(hù),因?yàn)樗堑妥杩沟模鼞?yīng)該與輸入級(jí)屏蔽。

保護(hù)間距和輸入電容之間需要權(quán)衡。保護(hù)線和輸入走線之間的間隙越大,輸入電容就越小。 最大限度地減少輸入表面積,以減少雜散電容和電離沖擊的影響。由于在皮安信號(hào)電平下,IR 壓降并不是一個(gè)大問(wèn)題,而且速度通常較低,因此請(qǐng)使用盡可能窄的走線寬度以減少雜散。使用最小尺寸的 SMT 焊盤來(lái)最大化焊盤之間的空間。 固定所有松散的電線。靈敏的高阻抗電路可以“看到”導(dǎo)線的移動(dòng) (ΔC)。在防護(hù)區(qū)域內(nèi),跳線或互連線應(yīng)裸露(無(wú)絕緣層,最好是鍍錫實(shí)心銅)。

去除阻焊層的印刷電路板區(qū)域應(yīng)封閉在密封防護(hù)罩或防護(hù)罩內(nèi),以防止潮濕和灰塵。 僅根據(jù)需要在導(dǎo)體周圍使用盡可能多的聚四氟乙烯或其他絕緣材料。守衛(wèi)其余區(qū)域。請(qǐng)注意高壓所需的間距。 注意板上的塑料和膠帶的使用。使用防靜電導(dǎo)電膠帶。 陶瓷電容器是壓電電容器,機(jī)械振動(dòng)和噪音會(huì)在電容器上產(chǎn)生電荷。在輸入、集成、反饋或偏置網(wǎng)絡(luò)中使用陶瓷電容時(shí)要小心。 整個(gè)外殼應(yīng)環(huán)境密封,當(dāng)濕度可能成為問(wèn)題時(shí),應(yīng)使用干燥劑包。作為定期校準(zhǔn)或現(xiàn)場(chǎng)服務(wù)的一部分,用戶或計(jì)量實(shí)驗(yàn)室應(yīng)易于更換這些包。

最大限度地減少電路板的彎曲和應(yīng)力。使用多個(gè)板安裝點(diǎn)或支架,并且不僅通過(guò)板支持外部用戶控件和連接器。 正如文章開頭提到的,與“傳統(tǒng)”電路相比,設(shè)計(jì)成功的亞皮安級(jí)電路需要不同的設(shè)計(jì)實(shí)踐。通過(guò)遵循上述簡(jiǎn)單的建議,就可以取得很高的首次成功率。 設(shè)計(jì)挑戰(zhàn)作者的任務(wù)是提高 LMP7721 低輸入偏置電流 CMOS 運(yùn)算放大器評(píng)估板的性能。該電路板需要展示器件的近飛安輸入電流性能,同時(shí)仍使用標(biāo)準(zhǔn)低成本 FR4 電路板和傳統(tǒng)的表面貼裝組件。該板還必須支持多種電路配置。

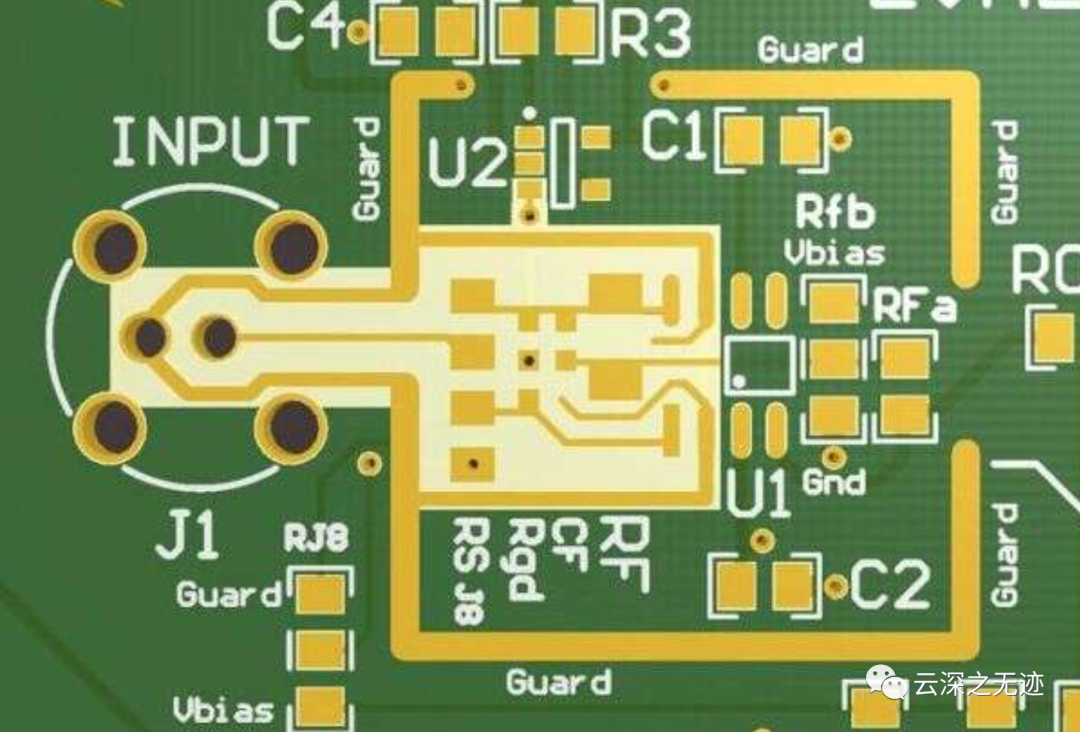

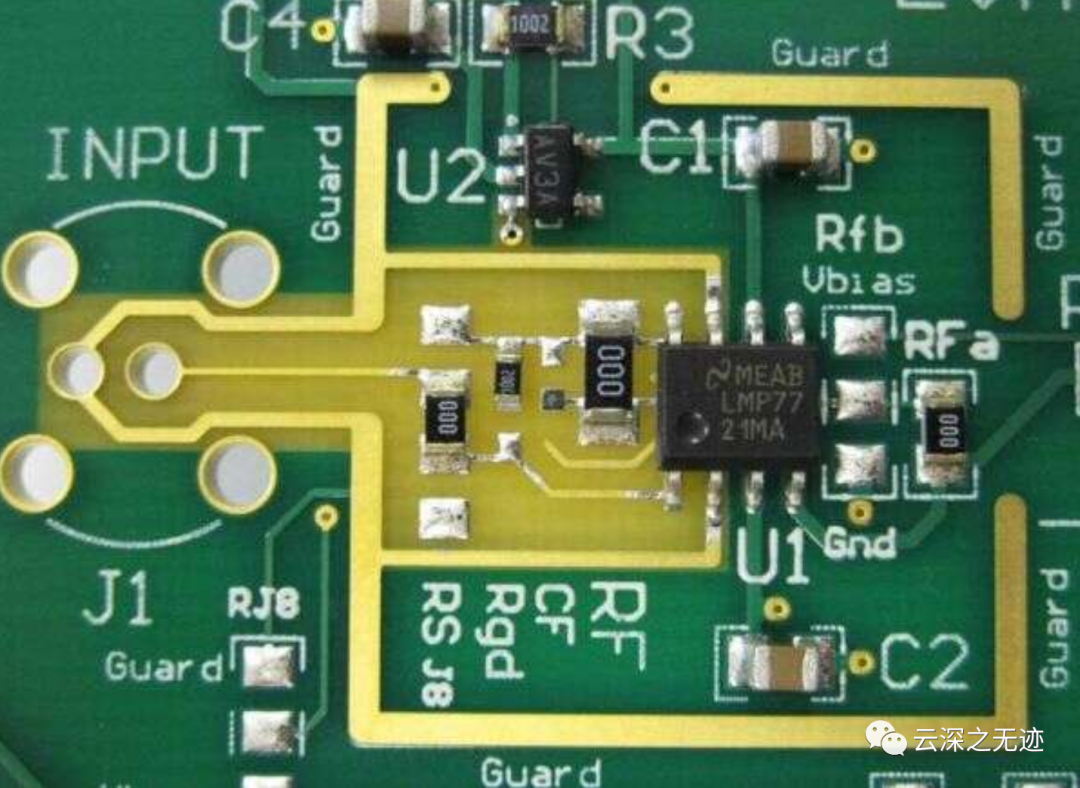

圖 4:LMP7721 評(píng)估板 第一步是最小化輸入表面積。這減少了雜散輸入電容,使輸入更容易保護(hù),最大限度地減少靜電耦合和電離沖擊的影響。

圖 5:顯示保護(hù)區(qū)的板輸入部分

在輸入電路周圍添加了廣泛的緩沖保護(hù)系統(tǒng)。在周邊添加了寬跡線,以允許在整個(gè)電路周圍安裝可選的金屬屏蔽。 輸入走線和所有敏感反饋組件均位于較小防護(hù)箱的周邊內(nèi)。較大的外部裸銅方盒用于焊接在金屬防護(hù)罩上,以覆蓋整個(gè)輸入電路。 LMP7721 具有獨(dú)特的引腳排列,通過(guò)保護(hù)引腳(引腳 2 和 7)將輸入引腳(引腳 1 和 8)與電源和輸出引腳分開。這些引腳連接到防護(hù)裝置,以提供一直到引線框架級(jí)別的防護(hù)。 該區(qū)域的阻焊層也被去除,以減少電荷積累。

圖 6:多用途電阻墊

為了最大限度地減少輸入電容并減少輸入的物理表面積,輸入走線非常薄,并且電阻焊盤具有跳線的雙重作用。 該布局旨在通過(guò)更改一些電阻器和跳線電阻器來(lái)適應(yīng)反相、非反相和緩沖器配置(照片中顯示了“緩沖器”配置)。 通常,每個(gè)電阻器,甚至是未使用的電阻器選項(xiàng),都會(huì)有自己的焊盤。這將使幾個(gè)未連接的焊盤“浮動(dòng)”而未使用。 相反,焊盤的布局使得將電阻器放置在適當(dāng)?shù)奈恢眉纯赏瓿呻娐凡⑦x擇配置。 其結(jié)果是一個(gè)非常緊密、緊湊的布局,并且暴露的輸入導(dǎo)體最少。

當(dāng)然,專用電路會(huì)更小、更緊湊。 正確清潔電路板正確清潔電路板對(duì)于提供預(yù)期的亞皮安性能至關(guān)重要。 與傳統(tǒng)方法相比,正確清潔電路板和組件需要一些額外的步驟。剩余的助焊劑殘留物、水分和清潔殘留物會(huì)嚴(yán)重降低低電流性能。 不建議在最終清潔中使用“免洗”噴霧助焊劑。水溶性助焊劑仍然會(huì)留下一層薄膜。 對(duì)受保護(hù)區(qū)域內(nèi)的組件進(jìn)行任何返工后,應(yīng)重新清潔電路板。 應(yīng)使用異丙醇或甲醇清洗電路板,確保清除電路板上所有殘留的水分。應(yīng)擦洗元件引線之間的區(qū)域,并徹底沖洗表面安裝器件下方的區(qū)域。

圖7:用酸刷清潔板

在上圖中,使用酸刷擦洗電路板,該酸刷已將長(zhǎng)刷毛切成短長(zhǎng)度以增加刷毛硬度。這是為了更好地擦洗設(shè)備引腳之間。 “標(biāo)準(zhǔn)”清潔后,建議的擴(kuò)展清潔程序?yàn)椋?除去所有水分——否則它會(huì)與酒精發(fā)生反應(yīng)并留下白色粉末狀沉積物。 用酒精(80% 或更高)淹沒(méi)板。

用硬刷擦洗器件引線、連接器之間以及周圍的組件。 再次用酒精沖洗以清除碎片并用壓縮空氣吹掉多余的碎片。還可在 SMT 設(shè)備下進(jìn)行沖洗和吹氣。不要忘記板的底部! 快速擦干,然后用干凈的毛巾擦干。 烘烤板以除去剩余的水分。 清潔后,只能拿住板子的邊緣,不要觸摸防護(hù)區(qū)域內(nèi)的任何東西。

避免在板上呼吸,因?yàn)楹粑械柠}水會(huì)嚴(yán)重降低性能。如果保護(hù)區(qū)內(nèi)的部件發(fā)生任何變化,應(yīng)重復(fù)清潔程序。 電路板應(yīng)存放在密封的容器或袋子中,最好帶有干燥劑包。 驗(yàn)證電路板的性能組裝和清潔電路板后,必須測(cè)量電路板的性能。設(shè)計(jì)了一個(gè)簡(jiǎn)單的測(cè)試來(lái)檢查性能。 對(duì)于反相放大器或跨阻放大器,只需斷開電源并觀察基線“零”電平即可測(cè)量泄漏。任何高于理論基線水平的水平很可能是由于泄漏造成的。然而,由于這些電路包含大電阻,因此由于噪聲,解析毫微微安可能會(huì)很困難。

同相配置具有最高的輸入阻抗并且對(duì)泄漏最敏感。

因此,選擇非反相緩沖器配置來(lái)測(cè)試電路板性能。 為了測(cè)試同相輸入,使用了開路“浮動(dòng)”測(cè)試。漏電流在輸入電容上積分。根據(jù)所得的漂移率和已知的輸入電容值,可以計(jì)算出漏電流。 同相輸入“浮動(dòng)”測(cè)試相當(dāng)簡(jiǎn)單。輸入暫時(shí)用電線接地,然后通過(guò)快速?gòu)妮斎肷习蔚艚拥鼐€來(lái)打開。

然后允許輸入“浮動(dòng)”未連接,同時(shí)定期測(cè)量輸出電壓以計(jì)算電流。 測(cè)試所需的設(shè)備相當(dāng)簡(jiǎn)單,只需要一個(gè)數(shù)字萬(wàn)用表和一個(gè)秒表或類似的間隔記錄裝置。如果有數(shù)字示波器,也可用于此功能。 設(shè)置該設(shè)置被封裝在一個(gè)鋼制咖啡罐中,并用金屬蓋或鋁箔(不是塑料蓋)覆蓋。

圖 8:咖啡罐內(nèi)的測(cè)試電路。(可以看到測(cè)試線連接到輸入端) 一根長(zhǎng)而薄的接地非絕緣總線穿過(guò)頂部的一個(gè)小孔,插入輸入端。該電線如圖 8 左側(cè)所示。電線末端已彎曲成狹窄的“V”形,并摩擦配合到輸入墊中,因此可以快速輕松地拉出。 要開始測(cè)試,請(qǐng)將電線從外殼中完全拉出以打開輸入并開始測(cè)試。以 10 秒的間隔記錄輸出電壓,持續(xù) 500 秒。

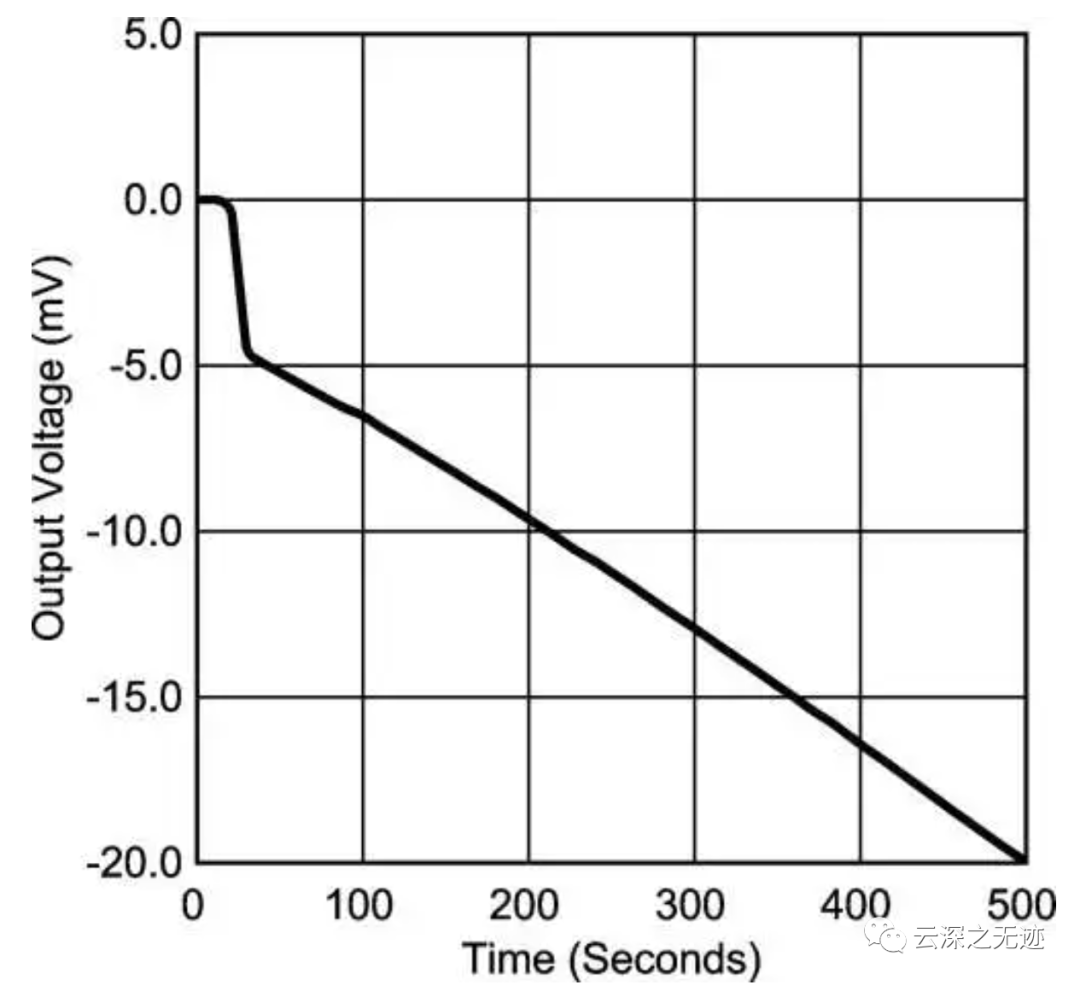

圖 9:測(cè)量的開路輸入結(jié)果

圖 9 顯示了結(jié)果。在前兩次采樣后(20 秒),將電線拉出。可見的是拉出電線后輸出的初始跳躍(由于機(jī)械干擾)。大約 40 秒后,輸出穩(wěn)定到每秒小于 1mV 的恒定漂移率。 使用已知的輸入電容(該板之前測(cè)量的電容約為 12pF)以及測(cè)得的電壓和時(shí)間變化,可以使用以下簡(jiǎn)單公式對(duì)輸出電壓隨時(shí)間的變化進(jìn)行積分,從而計(jì)算出輸入漏電流: i = (Δv / Δt) * C 看圖9,我們可以粗略計(jì)算出平均輸入電流。輸出從 200 秒時(shí)的 -10mV 變?yōu)?500 秒時(shí)的 -20mV。ΔV為-10mV,ΔT為300秒。將這些值代入公式即可得出約飛安級(jí)的泄漏。 (-10mV / 300秒) * 12.2pF = -1.2fA 這對(duì)于 FR4 板來(lái)說(shuō)是非常好的性能! 測(cè)量輸入電容輸入電容受多種因素影響。最突出的是放大器的輸入電容和走線電容。 大多數(shù)運(yùn)算放大器的輸入電容范圍為 2pF 至 15pF,“低噪聲”CMOS 器件的輸入電容高達(dá) 40pF。插座、PCB 走線、保護(hù)元件、反饋元件、連接器和電纜可以顯著增加該值。

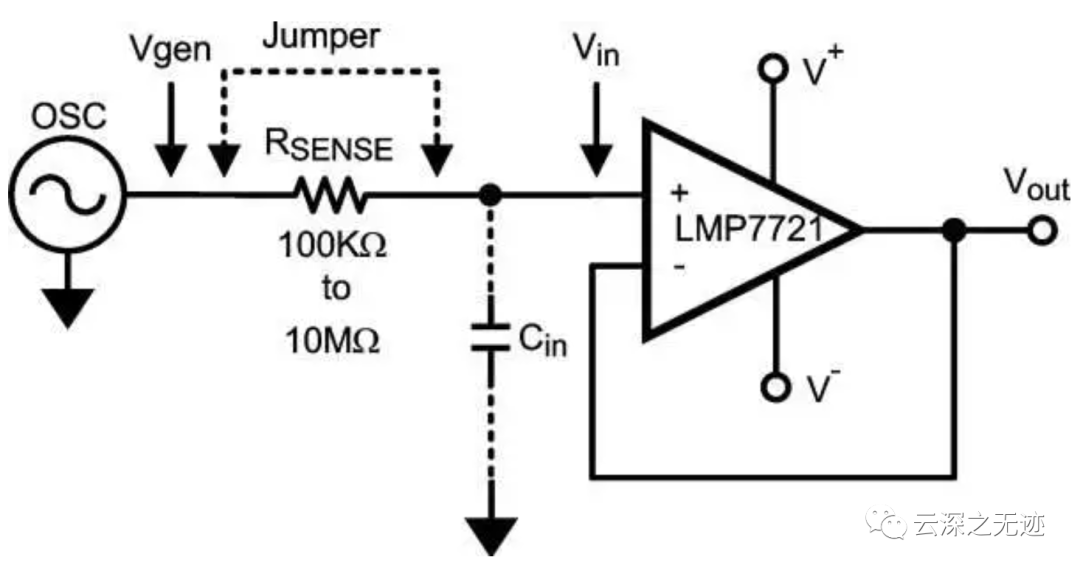

實(shí)際的總電容值將取決于您的個(gè)人電路和布局。 了解電路的輸入電容對(duì)于電路設(shè)計(jì)和電流測(cè)量都至關(guān)重要。測(cè)量電容的方法有多種,例如使用電容計(jì),但這種方法存在問(wèn)題。 大多數(shù)電容表都基于“電橋”或交流源測(cè)量配置,并且不能將其端子之一接地。一些手持式數(shù)字萬(wàn)用表具有電容功能,您可以利用手持設(shè)備的“浮動(dòng)”特性,但這些儀表通常在皮法范圍內(nèi)不準(zhǔn)確,和/或在“浮動(dòng)”時(shí)容易受到噪聲拾取或鄰近效應(yīng)的影響。 一種簡(jiǎn)單的技術(shù)涉及使用與輸入串聯(lián)的大串聯(lián)電阻(100K 至 >10M)和正弦波信號(hào)發(fā)生器(10Hz 至 ~100KHz)。

圖 10:輸入電容測(cè)試電路 RC 極由大串聯(lián)測(cè)試電阻 (Rsense) 和輸入電容 (Cin) 創(chuàng)建。

為了找到這個(gè)極點(diǎn),交流信號(hào)通過(guò)串聯(lián)電阻饋送,同時(shí)掃描發(fā)生器頻率,直到監(jiān)控的輸出幅度下降到參考頻率幅度的 70.7% (-3dB)。通過(guò)了解極點(diǎn)頻率和電阻值,就可以計(jì)算出輸入電容。 為了執(zhí)行測(cè)試,在檢測(cè)電阻器上放置一個(gè)臨時(shí)跳線以將其短路。將示波器或交流電壓表連接到放大器輸出 (Vout),然后將發(fā)生器設(shè)置為低參考頻率;例如 10Hz,并將幅度設(shè)置為一些方便的值,例如 100mV (Vgen)。 移除測(cè)試電阻器上的跳線,掃描發(fā)電機(jī)頻率,直到輸出電壓降至初始 Vin (70.7mV) 的 70.7%,并記錄發(fā)電機(jī)頻率。 現(xiàn)在頻率和電阻已知,因此現(xiàn)在可以根據(jù) RC 公式計(jì)算電容: Cin = 1 / (6.28 * R * F) 例如,使用 10Mohm 串聯(lián)電阻,我們發(fā)現(xiàn) 100mV 輸出在 1.305kHz 時(shí)降至 70.7mV。所以: Cin = 1 / (6.28 * 10M * 1305) 辛=12.2pF 此測(cè)量有幾點(diǎn)需要注意。

第一個(gè)是檢測(cè)電阻器兩端的雜散電容,對(duì)于 1/4 瓦電阻器,一般約為 0.15pF 至 0.3pF,會(huì)影響結(jié)果。避免這一問(wèn)題的方法是串聯(lián)使用幾個(gè)較低值的電阻器來(lái)創(chuàng)建一個(gè)具有低電容的大檢測(cè)電阻器。每個(gè)電阻器的雜散電容表現(xiàn)為串聯(lián)電容,因此串聯(lián)使用的電阻器越多,總串聯(lián)電容越小。 為此,電阻器被端對(duì)端焊接并允許彎曲到空氣中,遠(yuǎn)離附近的物體以最大限度地減少雜散電容。對(duì)于此測(cè)量,五個(gè) 2MΩ 電阻器被端對(duì)端焊接。有關(guān)實(shí)際使用的電阻串的照片,請(qǐng)參見第 2 部分中的圖 3 。

第二點(diǎn)是要注意電路的整體帶寬并注意輸出轉(zhuǎn)換速率限制。當(dāng)您找到極點(diǎn)頻率時(shí),最好再次短路檢測(cè)電阻并確保幅度與原始參考頻率 (~100mV) 相同,以驗(yàn)證你沒(méi)有耗盡帶寬或達(dá)到轉(zhuǎn)換速率限制。 如果幅度不同,請(qǐng)?jiān)黾訖z測(cè)電阻器的值或在輸入端添加已知電容以降低極點(diǎn)頻率(添加 20pF,然后從結(jié)果中減去 20pF)。任何類型的電容器都可用于此測(cè)試,因?yàn)樾孤┎⒉恢匾榱朔乐箟簲[限制,請(qǐng)使用盡可能低的幅度以獲得良好的結(jié)果。 總結(jié)我們希望本教程能讓你更好地理解亞皮安測(cè)量所面臨的挑戰(zhàn)。創(chuàng)造力是這些層面上最好的工具。與任何時(shí)候挑戰(zhàn)自然極限一樣,要為輕微的挫折和電路或布局修改做好準(zhǔn)備。

審核編輯:劉清

-

CMOS

+關(guān)注

關(guān)注

58文章

5735瀏覽量

235914 -

運(yùn)算放大器

+關(guān)注

關(guān)注

215文章

4966瀏覽量

173384 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1368瀏覽量

61790 -

smt

+關(guān)注

關(guān)注

40文章

2925瀏覽量

69593 -

雜散電容

+關(guān)注

關(guān)注

0文章

17瀏覽量

1426

原文標(biāo)題:設(shè)計(jì)低泄漏飛安電路,第 3 部分:低電流設(shè)計(jì)技術(shù)

文章出處:【微信號(hào):TT1827652464,微信公眾號(hào):云深之無(wú)跡】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

設(shè)計(jì)低泄漏飛安電路-組件選擇

設(shè)計(jì)低泄漏飛安電路—低電流的承載

泄漏電流安規(guī)常識(shí)的求教

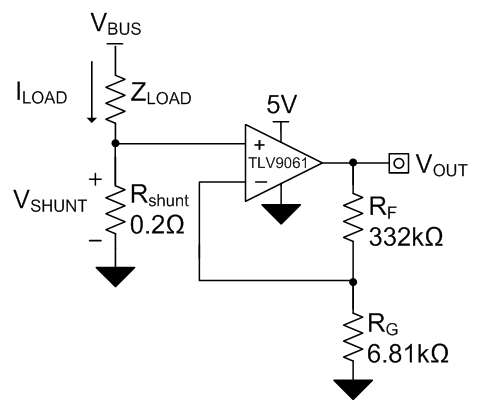

如何使用應(yīng)用印刷電路板PCB技術(shù)設(shè)計(jì)低側(cè)電流感應(yīng)電路?

如何利用印刷電路板技術(shù)設(shè)計(jì)低側(cè)電流感應(yīng)電路

如何使用應(yīng)用PCB技術(shù)設(shè)計(jì)低側(cè)電流感應(yīng)電路

±16.5V 低電容、低泄漏電流、精密SPDT開關(guān)TMUX6119數(shù)據(jù)表

36V、低電容、低泄漏電流、精密4:1模擬多路復(fù)用器TMUX6104數(shù)據(jù)表

±17V 低電容、低泄漏電流、精密四通道SPST開關(guān)TMUX611x數(shù)據(jù)表

5V、低泄漏電流、2:1 精密開關(guān)TMUX1119數(shù)據(jù)表

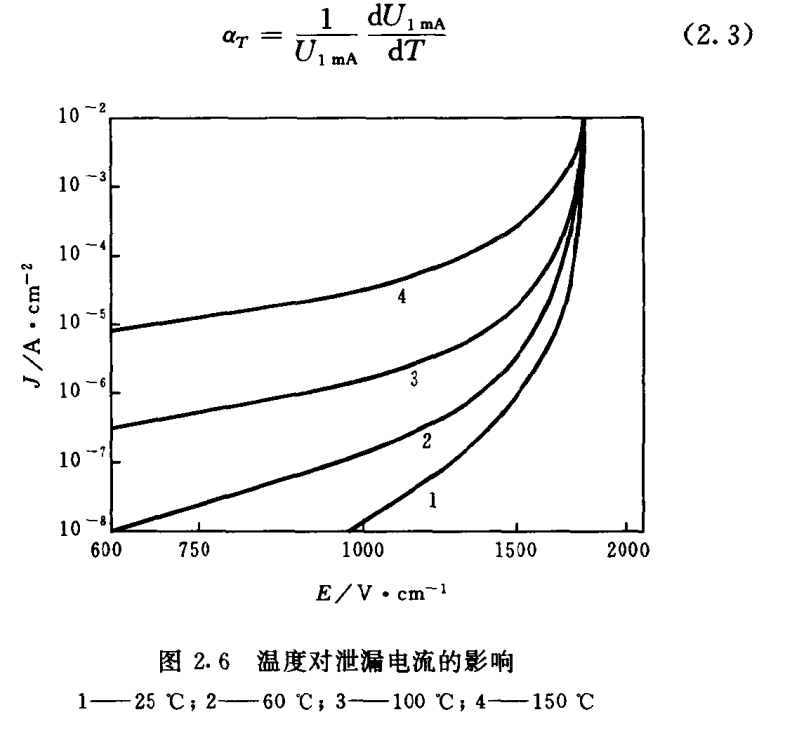

ZnO電阻片在低電場(chǎng)區(qū)域的泄漏電流及其電阻的負(fù)溫度系數(shù)

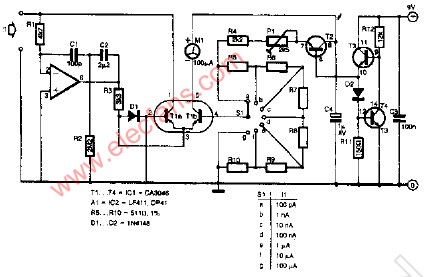

具有集成式精密增益的低漂移、低側(cè)雙向電流感測(cè)電路

設(shè)計(jì)低泄漏飛安電路—低電流設(shè)計(jì)技術(shù)

設(shè)計(jì)低泄漏飛安電路—低電流設(shè)計(jì)技術(shù)

評(píng)論