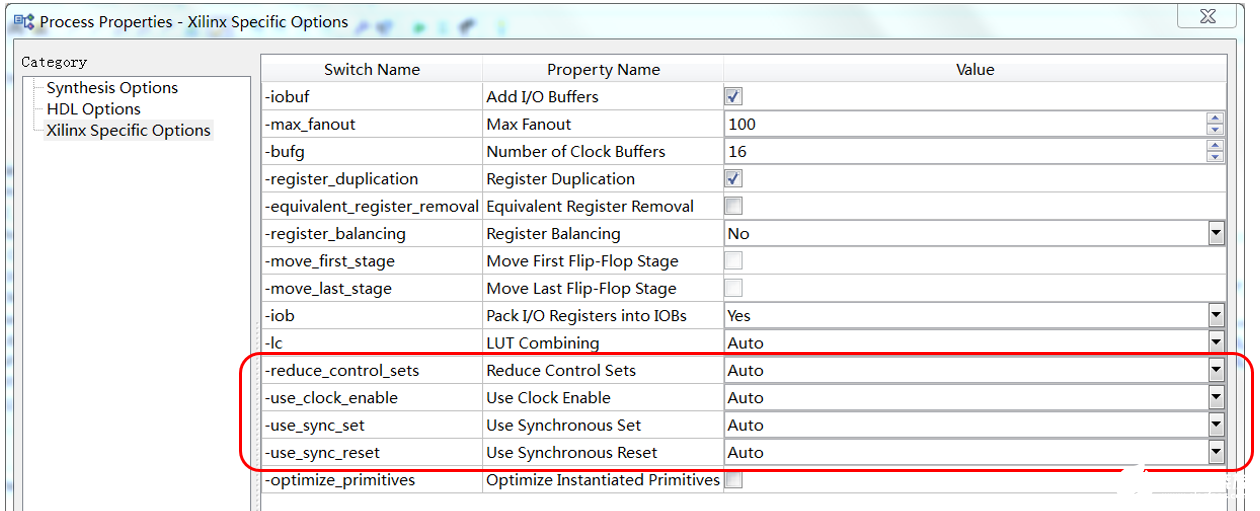

Spartan-6的一個Slice中包含8個觸發器(FFs),每個觸發器包括兩個控制信號:CE、SR(只能用作Reset或Set之一),但這8個觸發器共用控制信號輸入端口,這一特性限制控制信號不同的觸發器在布局(Map)時,不能優化入同一Slice,正是基于此,Xilinx推薦對于低扇出的觸發器控制信號在代碼編寫時盡量吸收進觸發器D輸入端之前的LUT中,并在XST的綜合屬性選項中提供配置項,讓XST綜合時自動將低扇出的控制信號吸收進觸發器D輸入端之前的LUT中,如下圖:

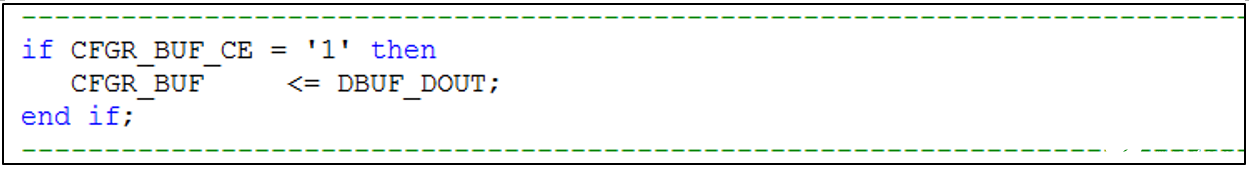

但是,對于設計中大量使用的門控型總線數據,即滿足某種條件時寄存一組總線數據,采用FDE的設計方式更有利于控制CE信號的扇出數量,基于此思路,特別試驗,代碼如下,其中DBUF_DOUT、CFGR_BUF即為32-bits的總線型數據:

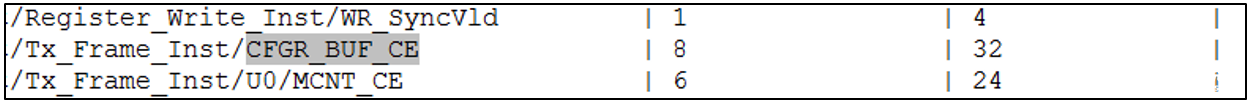

布局后,查看XST的Map Report中的Control Sets章節,如下圖:

可以看到,CFGR_BUF[31:0]這組總線數據采用8個Slices實現,每個Slice使用4個FFs,符合設計預期。

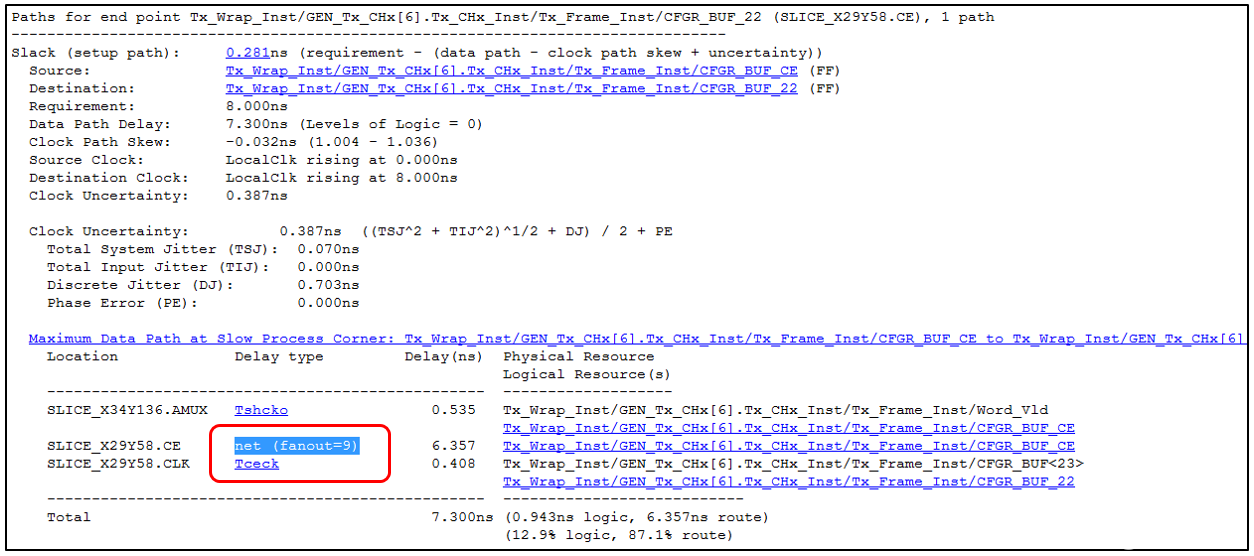

查看PAR后的Static Timing報告,可以看到,Static Timing報告中對CFGR_BUF_CE信號的扇出數量統計為9,即每個Slice的CE輸入端口統計為一個信號扇出,符合設計預期,如下圖:

綜合Xilinx用戶手冊介紹的原理和實際試驗結果,可以得出如下結論:XST在對Spartan-6布局布線時一個Slice的SR、CE輸入端口統計為一個信號扇出負載。

審核編輯:黃飛

-

Xilinx

+關注

關注

71文章

2169瀏覽量

121843 -

觸發器

+關注

關注

14文章

2002瀏覽量

61273 -

控制信號

+關注

關注

0文章

167瀏覽量

12009

發布評論請先 登錄

相關推薦

XMC4300從控制器與Spartan-6 FPGA兼容嗎?

Spartan-6 IO是否具有內置的施密特觸發器?

Spartan-6 FPGA工業影像目標設計平臺(Xilin

基于Spartan-6的FPGA SP601開發設計方案

Spartan-6 FPGA Configuration User Guide

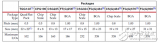

Xilinx Spartan-6系列封裝概述和管腳分配

Spartan-6 FPGA中的DCM功能介紹

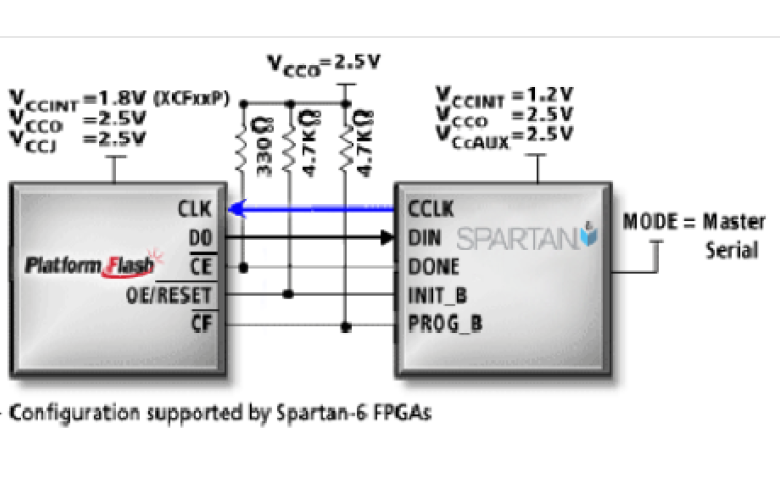

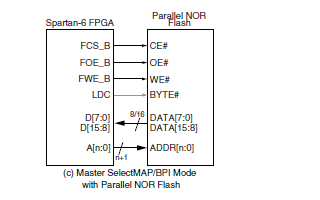

Spartan-6 FPGA的配置教程說明

Spartan-6觸發器控制信號的扇出數量統計方式

Spartan-6觸發器控制信號的扇出數量統計方式

評論