本文的目的不是介紹內存尋址的具體設計,其實很多細節我也不了解,而是想通過內存尋址的設計思想看看對 FPGA 的設計有什么幫助和借鑒。

內存尋址有兩個的重要的設計:

內存分頁

頁表分級

關于內存分頁 - 規整即簡單

內存分頁即將內存分割為以頁(一般是4KB)為單元的塊,然后內存的分配和使用都是以頁為最小單元。假如一個進程只需要 2KB 的內存,仍然給其分配 4KB(一頁)的空間。

關于內存分頁的好處,我覺得知乎上一位知友的描述非常生動和形象。他將內存分頁比喻為停車場劃分停車位。停車位的劃分使得停車人尋找停車位時變得簡單,停車人不再需要自己判斷位置空間是否夠大能停下車,只需要看有沒有空位即可。同時也使停車位的使用管理變得高效,停車場管理人員可以很容易判斷并發布停車位的空位信息。當然,這可能只是內存分頁的好處中的其中一個。

我們可以總結一下內存分頁的使用場景:

有一塊大的 memory 空間

有很多 Users 要使用 memory

Users 使用 memory 的時間和空間大小不確定

那么當我們在 FPGA 設計中遇到這樣類似的場景時,便可以借鑒內存分頁的思想,將 memory 劃分為不同的塊,來提高 memory 的使用和管理效率。當然,對于 memory 塊的劃分可能導致 memory 的浪費,像前面舉的例子,只需要 2KB 的內存,卻分配了 4KB 的空間。如何正確的取舍,去做 tradeoff,這也是設計者需要考慮的。

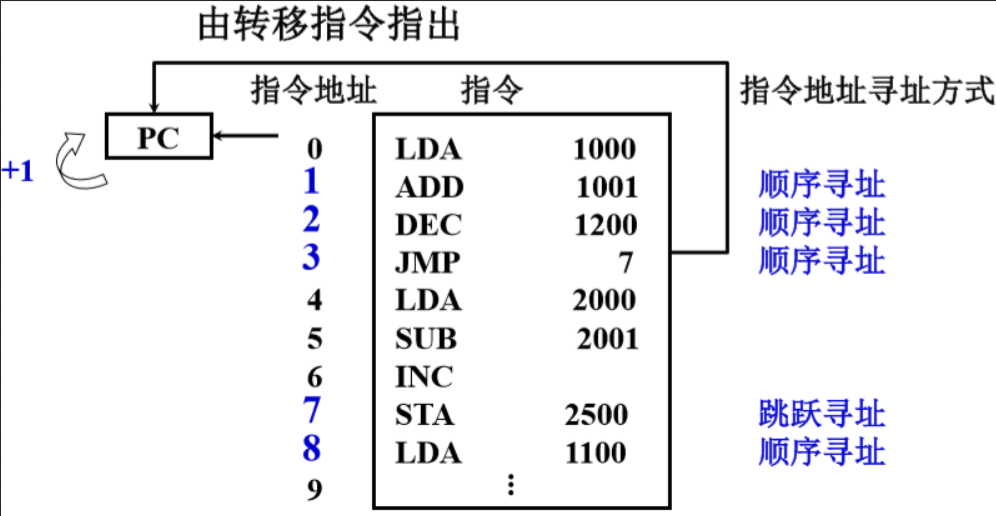

再往本質里看,這其實是硬件設計上的一個“規整”問題。就像CPU指令集的設計,因為不同指令對 bit 利用的規整,簡化了CPU的設計。規整即簡單。

關于頁表分級 - 時間換空間

頁表是用來將虛擬地址映射為物理地址的數據結構。對于 4KB 的頁單元,需要 12-bit 來尋址。如果地址線的總位寬是 32-bit,那么我們需要 2^20 (32-12=20) 個頁表,假如每個表項用 4 byte,那么頁表總共要用到 4MB 的內存。這還只是一個進程用到的空間。

頁表分級減少了頁表對內存的使用量。用過兩級分頁(第一級頁目錄+第二級頁表),即先通過第一級頁目錄查找到頁表,再通過第二級頁表去查找頁,只有當第一級的頁目錄項用到時才去分配第二級的頁表。舉個例子,假如頁目錄和頁表分別占用10-bit。頁目錄有2^10個項 (一共占用 4KB 內存),假如頁目錄只有第一項被用到,那么我們只需要分配其對應的頁表,這個頁表也是有2^10個項 (一共占用 4KB 內存),那么此時只用到了 4KB+4KB = 8KB 內存,相比于 4MB 節省了很大部分。

我們總結一下頁表分級的場景:

多個 Users 共用一份地址線訪問 memory

每個 Users 都需要自己的 memory 空間

實際有效的 Users 的數目是動態變化的

Users 對 memory 空間的使用也是動態變化的

遇到類似的場景我們便可以考慮將地址分級,對 Users 動態分配 memory 空間,幾個 Users 甚至可以復用一份 memory,達到節省 memory 使用的目的。這樣做當然增加了 memory 控制和管理的復雜度,也是設計上的 tradeoff。

再往本質里看,這個場景其實利用了事件發生的時間上的差異。是時間“換”空間的概念,地址分級只是實現這個概念的一個手段。

總結

本文思考了內存尋址的兩個設計點對 FPGA 設計的借鑒意義。很多時候,設計的思想是相通的,尤其是像 CPU 或者 Linux內核 這樣的經典的,經久不衰的設計。

來源: 本文轉載自FPGA開發之路 公眾號

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603429 -

內核

+關注

關注

3文章

1372瀏覽量

40291 -

cpu

+關注

關注

68文章

10863瀏覽量

211784 -

Linux

+關注

關注

87文章

11304瀏覽量

209524 -

內存

+關注

關注

8文章

3025瀏覽量

74056

原文標題:從內存尋址看 FPGA 設計

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么是單片機尋址方式?尋址方式有哪些?

Hexagon DSP的十二種尋址模式

單片機的可尋址內存是何意思

ARM指令尋址方式之內存訪問指令尋址

西門子PLC如何尋址,具體方法是怎樣的

尋址方式與內存計算的詳細說明

內存尋址的具體設計

內存尋址的具體設計

評論