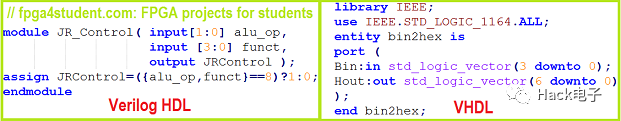

Verilog和VHDL之間的區(qū)別將在本文中通過示例進(jìn)行詳細(xì)說明。對優(yōu)點(diǎn)和缺點(diǎn)的Verilog和VHDL進(jìn)行了討論。

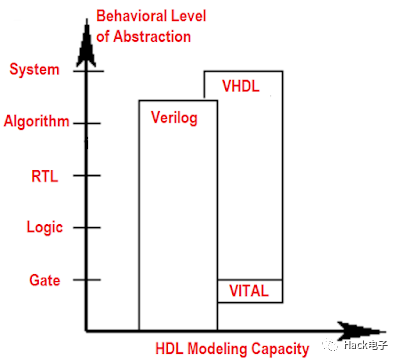

HDL 建模能力:Verilog與VHDL

首先,讓我們討論一下 Verilog 和 VHDL 的硬件建模能力,因?yàn)樗鼈兌际怯糜诮S布挠布枋稣Z言。

下圖顯示了 Verilog 和 VHDL 在硬件抽象行為級別方面的 HDL 建模能力。

圖形來源:Douglas J. Smith,“VHDL 和 Verilog 比較和對比加上用 VHDL、Verilog 和 C 編寫的建模示例”

低級建模

如上圖所示,Verilog 和 VHDL 都能夠?qū)τ布M(jìn)行建模。但是,在底層硬件建模方面,Verilog優(yōu)于VHDL。這是合理的,因?yàn)?Verilog 最初是為建模和模擬邏輯門而創(chuàng)建的。事實(shí)上,Verilog 具有內(nèi)置原語或低級邏輯門,因此設(shè)計(jì)人員可以在 Verilog 代碼中實(shí)例化原語,而 VHDL 則沒有。

Verilog 的門基元:and、nand、or、nor、xor、xnor、buf、not、bufif0、notif0、bufif1、notif1、pullup、pulldown。

Verilog 的開關(guān)原語:pmos、nmos、rpmos、rnmos、cmos、rcmos、tran、rtran、tranif0、rtranif0、tranif1、rtranif1。

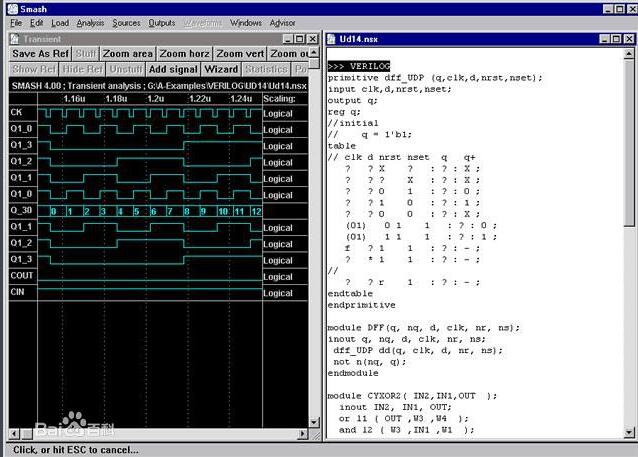

更重要的是,Verilog 支持用戶定義基元 (UDP),因此設(shè)計(jì)人員可以定義自己的單元基元。此功能對于 ASIC 設(shè)計(jì)人員來說尤其必要。

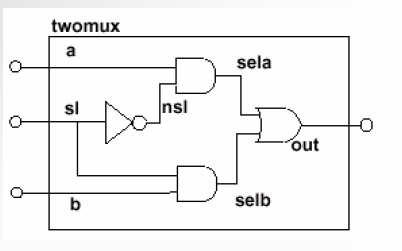

以下是有關(guān)如何在 Verilog 代碼中實(shí)例化門基元的 Verilog 示例:

or #5 u1(x,y,z); and #10 u2(i1,i2,i3); ADC_CIRCUIT u3(in1,out1,out2,clock); // ADC_CIRCUIT is an User-Defined Primitive for // Analog to Digital Converter for example.

Verilog 中一些低級內(nèi)置門基元的 VHDL 等效項(xiàng)可以通過使用邏輯運(yùn)算符如 NOT、AND、NAND、OR、NOR、XOR、XNOR 來實(shí)現(xiàn)。

下面是 Verilog 門基元的 VHDL 等效代碼示例:

or u1(x,y,z); in Verilog <=> x <=< span=""> y OR z; in VHDLand u2(i1,i2,i3); (Verilog) <=> i3 <=< span=""> i2 AND i3; in VHDL

為了支持 Verilog 中的 UDP 功能,VITAL(VHDL Initiative Towards ASIC Libraries-VHDL 面向 ASIC 庫的倡議)問世,使 ASIC 設(shè)計(jì)人員能夠在符合 VITAL 的 VHDL 中創(chuàng)建自己的單元基元或 ASIC 庫,如上圖所示。盡管如此,VHDL 仍然可能無法實(shí)現(xiàn) Verilog 對低級硬件建模的支持。因此,如果我是 ASIC 設(shè)計(jì)師,我會更喜歡 Verilog 而不是 VHDL。

高級建模

另一方面,如上述圖表所示,VHDL 在高級硬件建模方面優(yōu)于 Verilog。與 Verilog 相比,VHDL 為高級硬件建模提供了更多功能和構(gòu)造。以下是在比較 VHDL 和 Verilog 時支持高級硬件建模的主要不同功能:

?VHDL 中的用戶定義數(shù)據(jù)類型

Verilog 的數(shù)據(jù)類型非常簡單,都是用 Verilog 語言定義的(用戶不能在 Verilog 中定義自己的數(shù)據(jù)類型)。Verilog 有兩種主要的數(shù)據(jù)類型,包括 net 數(shù)據(jù)類型(用于將組件連接在一起,例如wire(最流行)、wor、wand、tri、trior 等)和變量數(shù)據(jù)類型(用于臨時存儲,例如reg(最流行),整數(shù)、時間、實(shí)數(shù)和實(shí)時)。

VHDL支持許多不同的數(shù)據(jù)類型,包括預(yù)定義的 VHDL 數(shù)據(jù)類型和用戶定義的數(shù)據(jù)類型。預(yù)定義的 VHDL 數(shù)據(jù)類型包括位、位向量、字符串、時間、布爾值、字符和數(shù)字(實(shí)數(shù)或整數(shù))。VHDL 允許設(shè)計(jì)人員根據(jù)預(yù)定義的 VHDL 數(shù)據(jù)類型定義不同的類型;對于可能使用許多不同數(shù)據(jù)類型的復(fù)雜和高級系統(tǒng)來說,這是一個很好的功能。以下是用于定義新數(shù)據(jù)類型的示例 VHDL 代碼:

type int_8bit is range 0 to 255 -- define 8-bit unsigned numbers signal i : int_8bit; type state_FSM is (Idle, start, calculate , finish, delay) -- define symbolic states to represent FSM states. signal current_state, next_state: state_FSM;

?VHDL 中的設(shè)計(jì)重用包

VHDL 中的包通常用于數(shù)據(jù)類型和子程序的聲明。VHDL 包中聲明的子程序或數(shù)據(jù)類型可用于許多不同的實(shí)體或體系結(jié)構(gòu)。例如:

package fsm_type is type FSM_states is (IDLE, TRANSMIT, RECEIVE, STOP); end package -- to use the FSM_states type in an entity or architecture -- use the following statement on top of the entity use work.fsm_type.all entity example is

Verilog 中沒有包定義。與 VHDL 包最接近的 Verilog 等效項(xiàng)是`includeVerilog 編譯器指令。函數(shù)或定義可以單獨(dú)保存在另一個文件中,然后通過使用`include指令在模塊中使用它。下面是一個 Verilog 示例代碼:

// Below is the content of "VerilogVsVHDL.h" file `define INPUT_VERILOG "./test_VerilogvsVHDL.hex" // Input file name `define OUTPUT_VHDL "VHDL.bmp" // Output file name `define VERILOG_VHDL_DIFFERENCE // Then call it in every single module that you want to use the definition above `include "VerilogVsVHDL.h"

?VHDL 中的配置語句

一個 VHDL 設(shè)計(jì)可以為一個實(shí)體獲得許多具有不同體系結(jié)構(gòu)的設(shè)計(jì)實(shí)體。配置語句將確切的設(shè)計(jì)實(shí)體與設(shè)計(jì)中的組件實(shí)例相關(guān)聯(lián)。當(dāng)實(shí)體中有多個架構(gòu)時,配置語句會繼續(xù)指定所需的設(shè)計(jì)架構(gòu)分配給實(shí)體以進(jìn)行綜合或仿真。當(dāng) VHDL 設(shè)計(jì)人員需要管理大型高級設(shè)計(jì)時,此功能非常有用。

以下是配置語句的 VHDL 示例代碼:

entity BUF is generic (DELAY : TIME := 10 ns); port ( BUF_IN : in BIT; BUF_OUT : out BIT); end BUF; -- The first design architecture for BUF architecture STRUCT_BUF1 of BUF is signal temp: bit; begin BUF_OUT <=< span=""> not temp after DELAY; temp <=< span=""> not BUF_IN after DELAY; end STRUCT_BUF1; -- The second design architecture for BUF architecture STRUCT_BUF2 of BUF is begin BUF_OUT <=< span=""> BUF_IN after 2*DELAY;; end STRUCT_BUF2; -- Testbench to simulate BUF entity entity BUF_TESTBENCH is end BUF_TESTBENCH; architecture STRUCT_BUF_TEST of BUF_TESTBENCH is signal TEST1, TEST2 : BIT := '1'; -- BUF_COMP component declaration: component BUF_COMP is generic (TIME_DELAY : TIME); port ( IN1 : in BIT; OUT1 : out BIT ); end component; begin -- instantiation of BUF_COMP component: DUT:BUF_COMP generic map (10 ns) port map (TEST1,TEST2); end STRUCT_BUF_TEST; -- Configuration specify the design entity and architecture -- for the DUT component instance in the testbench above configuration CONFIG_BUF of TEST_BUF is -- Associate BUF_COMP component instance to BUF design entity -- and STRUCT_BUF1 design architecture for simulation for STRUCT_BUF_TEST for DUT : BUF_COMP use entity WORK.BUF (STRUCT_BUF1) generic map (DELAY => TIME_DELAY) port map (BUF_IN => IN1, BUF_OUT => OUT1); end for; end for ; end CONFIG_BUF;

Verilog-2001 中還添加了配置塊。

?VHDL 中的庫管理

同時查看 Verilog 和 VHDL 代碼時,最明顯的區(qū)別是 Verilog 沒有庫管理,而 VHDL 在代碼頂部包含設(shè)計(jì)庫。VHDL 庫包含已編譯的架構(gòu)、實(shí)體、包和配置。此功能在管理大型設(shè)計(jì)結(jié)構(gòu)時非常有用。上面已經(jīng)給出了 VHDL 中的包和配置示例。以下是 VHDL 中庫管理的 VHDL 示例代碼:

-- library management in VHDL library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.numeric_std.all; use work.clock_div.all;

簡而言之,VHDL 在高級硬件建模方面比 Verilog 更好。由于 FPGA 設(shè)計(jì)流程不需要低級硬件建模,如果我是 FPGA 設(shè)計(jì)師,我更喜歡 VHDL 而不是 Verilog。

值得一提的是,SystemVerilog 的創(chuàng)建是為了通過將 VHDL 中的高級功能和結(jié)構(gòu)添加到 Verilog 中進(jìn)行驗(yàn)證來增強(qiáng) Verilog 語言在高級建模中的弱點(diǎn)。SystemVerilog 現(xiàn)在廣泛用于 IC 驗(yàn)證。

冗長(Verboseness:):Verilog 與 VHDL

?VHDL 是強(qiáng)類型的vs Verilog 是松散類型的

VHDL 是一種非常強(qiáng)類型的硬件描述語言,因此必須使用匹配和定義的數(shù)據(jù)類型正確編寫 VHDL 代碼。這意味著如果在 VHDL 中分配時混合數(shù)據(jù)類型或不匹配信號,將會出現(xiàn)編譯錯誤。另一方面,Verilog 是一種松散類型的語言。在 Verilog 中,您可以在分配時混合數(shù)據(jù)類型或不匹配信號。下面是不匹配信號的 VHDL 示例代碼:

signal test_reg1: std_logic_vector(3 downto 0); signal test_reg2: std_logic_vector(7 downto 0); test_reg2 <=< span=""> test_reg1; -- You cannot assign a 4-bit signal to an 8-bit signal -- in VHDL, it will introduce a syntax error below: -- Width mismatch. Expected width 8, Actual width is 4 -- for dimension 1 of test_reg1.

編譯上面的VHDL代碼時,會出現(xiàn)語法錯誤“Width mismatch. Expected width 8, Actual width is 4”。如果將VHDL代碼改為“test_reg2 <= "0000"&test_reg1;?"匹配位寬,則不會出現(xiàn)語法錯誤。?

如果在 Verilog 中將 4 位信號分配給 8 位信號會怎樣?

wire [3:0] test1; wire [7:0] test2; // In Verilog, you can assign 4-bit signal to 8-bit signal. assign test2 = test1; // there will be no syntax error during synthesis

當(dāng)您將 4 位信號分配給 8 位信號時,Verilog 編譯器不會引入語法錯誤。在 Verilog 中,不同位寬的信號可以相互分配。Verilog 編譯器將使源信號的寬度適應(yīng)目標(biāo)信號的寬度。未使用的位將在綜合期間進(jìn)行優(yōu)化。

下面是在分配信號時混合數(shù)據(jù)類型的另一個 VHDL 示例:

signal test1: std_logic_vector(7 downto 0); signal test2: integer; test2 <=< span=""> test1; -- Syntax Error: type of test2 is incompatile with type of test1

上面的 VHDL 代碼會引入一個語法錯誤“(type of test2 is incompatible with type of test1)test2 的類型與 test1 的類型不兼容”。你必須轉(zhuǎn)換test1的分配之前整數(shù)數(shù)據(jù)類型TEST1到TEST2如下:

library IEEE; USE ieee.numeric_std.ALL; signal test1: std_logic_vector(3 downto 0); signal test2: integer; -- Use IEEE.NUMBERIC_STD.ALL Library for this conversion test2 <=< span=""> to_integer(unsigned(test1)); -- No syntax errors this time

另一方面,Verilog 在分配時混合數(shù)據(jù)類型時沒有問題。以下是一個 Verilog 示例:

reg [3:0] test1;

integer test2;

always @(test1) begin

test2 = test1;

end

// NO syntax errors when compiling

當(dāng)您將具有reg數(shù)據(jù)類型的信號分配給具有不同數(shù)據(jù)類型(如integer )的另一個信號時,Verilog 編譯器不會像在 VHDL 中那樣引入語法錯誤。

?VHDL 復(fù)雜數(shù)據(jù)類型與 Verilog 簡單數(shù)據(jù)類型

如上所述,VHDL 有許多不同的復(fù)雜數(shù)據(jù)類型,用戶還可以定義許多其他復(fù)雜數(shù)據(jù)類型。這也使得 VHDL 比 Verilog 更冗長,因?yàn)?Verilog 只有 2 種主要數(shù)據(jù)類型,并且 Verilog 中不允許用戶定義的數(shù)據(jù)類型。

換句話說,為了對同一電路建模,VHDL 代碼通常比 Verilog 代碼更冗長、更長,因?yàn)?VHDL 的強(qiáng)類型,我們需要在不同的復(fù)雜數(shù)據(jù)類型之間執(zhí)行轉(zhuǎn)換。它可以是優(yōu)點(diǎn)也可以是缺點(diǎn)。事實(shí)上,當(dāng)您在 VHDL 代碼中分配錯誤的內(nèi)容時,VHDL 編譯器更有可能引入語法錯誤。當(dāng)您成功編譯 VHDL 代碼時,與 Verilog 相比,您的 VHDL 代碼更有可能正常工作。另一方面,Verilog 是松散類型的,更簡潔,更簡單。但是編譯成功后,很有可能你的Verilog代碼中仍然存在錯誤。

下面是另一個使 VHDL 比 Verilog 更冗長的示例代碼:

-- VHDL code for ALU process(SEL,ABUS,BBUS,tmp1,tmp2) begin case(SEL) is when "0000" => ALUOUT <=< span=""> tmp1; -- ADD when "0001" => ALUOUT <=< span=""> tmp2;-- SUB when "0010" => ALUOUT <=< span=""> BBUS; -- AND when others => ALUOUT <=< span=""> ABUS; end case; end process; // Verilog equivalent to VHDL ALU assign ALUOUT=(SEL==0)?tmp1:((SEL==1)?tmp2:((SEL==2)?BBUS:ABUS));

VHDL 中的 if else、when/else、with/select 語句可以在 Verilog 中使用條件運(yùn)算符 (?) 表達(dá)得更簡潔,如上例所示。

Verilog 和 VHDL 之間的其他區(qū)別:

?Verilog 類似于C 編程語言,而 VHDL 類似于Ada或 Pascal 編程語言

?Verilog 區(qū)分大小寫,而 VHDL 不區(qū)分大小寫。這意味著DAta1和Data1在Verilog中是兩個不同的信號,但在VHDL中是相同的信號。

?在 Verilog 中,要在模塊中使用組件實(shí)例,您只需在模塊中使用正確的端口映射對其進(jìn)行實(shí)例化。在VHDL中,在實(shí)例化實(shí)例之前,如果您使用舊的實(shí)例化語句作為以下示例,則通常需要將組件聲明為架構(gòu)或包中。在 VHDL-93 中,您可以像這樣直接實(shí)例化實(shí)體:“Label_name: entity work.component_name port map (port list);”。

例如,要在 VHDL 中實(shí)例化實(shí)體 clk_div,將在體系結(jié)構(gòu)代碼中添加一個組件聲明,如下所示:

architecture Behavioral of digital_clock is -- component declaration before instantiation below component clk_div port ( clk_50: in std_logic; clk_1s : out std_logic ); end component; signal clk, clk_1s: std_logic; begin -- component instantiation create_1s_clock: clk_div port map (clk_50 => clk, clk_1s => clk_1s); end

或者在包中聲明組件以供重用:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

package clock_div_pack is

component clk_div is

port (

clk_50: in std_logic;

clk_1s : out std_logic

);

end component clk_div;

end package;

-- Declare the component in a separate package and

-- reuse by using the following statement:

use work.clock_div_pack.all;

entity clock is

end clock;

architecture Behavioral of clock is

signal clk, clk_1s: std_logic;

begin

create_1s_clock: clk_div port map (clk_50 => clk, clk_1s => clk_1s);

end

在 VHDL-93 中直接實(shí)例化實(shí)體的示例代碼:

create_1s_clock: entity work.clk_div port map (clk_50 => clk, clk_1s => clk_1s);

?Verilog 具有編譯器指令,例如`timescale(聲明時間單位和延遲精度)、`define(將文本字符串聲明為宏名稱)、`ifdef、ifndef `else `elseif `endif(條件編譯)、`include(包括一個可以包含函數(shù)或其他聲明的文件)等。VHDL 沒有編譯器指令。

?VHDL 支持枚舉和記錄數(shù)據(jù)類型,允許用戶為一種數(shù)據(jù)類型定義多個信號。Verilog 不支持枚舉和記錄類型。下面是枚舉和記錄類型的 VHDL 代碼:

type FSM is (IDLE, TEST, VERILOGvsVHDL, STOP, FPGA4student); -- enumerated type type int_4 is range 0 to 15; -- record tye in VHDL type record_example is record data1: integer; data2: int_4; data3: FSM; end record;

?等等。

盡管 Verilog 和 VHDL 之間存在差異,但它們是兩種最流行的硬件描述語言。如果可以,最好同時學(xué)習(xí)它們。重要的是要記住,在編碼時始終考慮邏輯門或硬件以開發(fā)硬件編碼思維,而在使用 Verilog 和 VHDL 編碼時忘記軟件編程思維,這一點(diǎn)非常重要。

審核編輯:劉清

-

NAND

+關(guān)注

關(guān)注

16文章

1708瀏覽量

137225 -

asic

+關(guān)注

關(guān)注

34文章

1237瀏覽量

121400 -

VHDL語言

+關(guān)注

關(guān)注

1文章

113瀏覽量

18302 -

編譯器

+關(guān)注

關(guān)注

1文章

1645瀏覽量

49578 -

Verilog HDL

+關(guān)注

關(guān)注

17文章

126瀏覽量

50665

原文標(biāo)題:例說Verilog HDL和VHDL區(qū)別,助你選擇適合自己的硬件描述語言

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

如何用VHDL、Verilog HDL實(shí)現(xiàn)設(shè)計(jì)輸入?

X-HDL v3.2.55 VHDL/Verilog語言翻譯器

VHDL和Verilog HDL語言對比

Verilog HDL與VHDL及FPGA的比較分析

vhdl和verilog的區(qū)別_vhdl和verilog哪個好?

Verilog HDL的基礎(chǔ)知識詳細(xì)說明

Verilog HDL和VHDL的區(qū)別

Verilog HDL語言技術(shù)要點(diǎn)

Verilog HDL教程135例免費(fèi)下載

評論