SN74HC165DR是一種8位串行至并行移位寄存器。它是一款集成電路芯片,通常用于將并行輸入轉換為串行輸出。在這篇文章中,我們將詳細介紹SN74HC165DR的工作原理,包括其內部結構和關鍵功能。

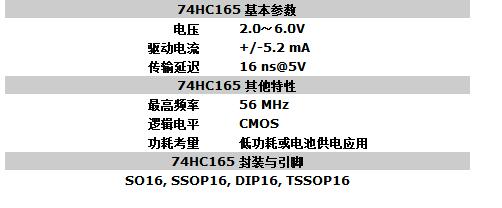

SN74HC165DR是一種非常常用的集成電路芯片,在數字電子系統中起著重要的作用。它具有高速、高性能和低功耗的特性,可以完成從并行到串行的數據轉換,并通過串行輸出將數據傳輸到后續的處理電路中。

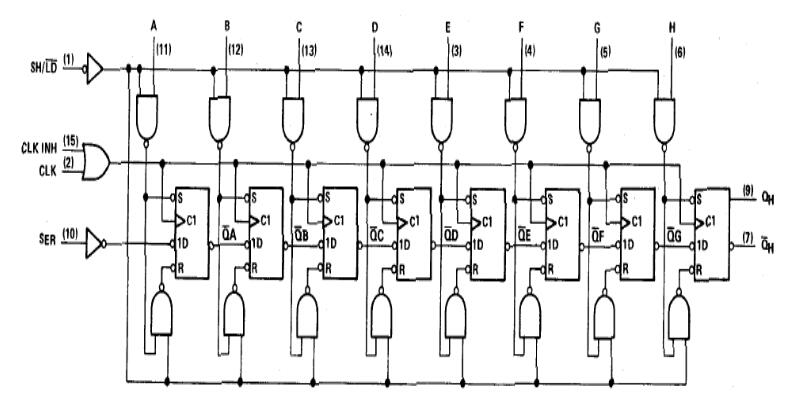

SN74HC165DR的內部結構

SN74HC165DR由多個邏輯門、存儲單元和控制電路組成。

- 邏輯門:SN74HC165DR內部包含多個邏輯門,用于實現數據的輸入和輸出操作。這些邏輯門可以執行與、或、非等邏輯運算,以實現數據處理和控制功能。

- 存儲單元:SN74HC165DR內部包含8個存儲單元,用于存儲輸入數據。每個存儲單元均為D觸發器,可以存儲一個比特位的數據。

- 控制電路:SN74HC165DR還包含一些控制電路,用于控制數據輸入和輸出的時序。通過適當的時序控制,可以實現數據的穩定和準確的傳輸。

SN74HC165DR的關鍵功能

- 并行輸入:SN74HC165DR具有8個并行輸入引腳,分別為A0~A7。通過這些引腳,可以將8個并行輸入數據傳輸到芯片內部。

- 串行輸出:SN74HC165DR具有一個串行輸出引腳,稱為Q7。通過這個引腳,可以將數據按順序傳輸到后續的電路中。

- 移位操作:SN74HC165DR具有一個移位引腳,稱為SH/LD (Shift/Load)。通過在移位操作時將SH/LD引腳置高,可以使芯片進入移位模式,此時輸入數據將通過串行輸出引腳按順序輸出。當移位操作完成后,將SH/LD引腳置低,芯片將停止移位,并將輸出數據保持不變。

- 并行加載:SN74HC165DR具有一個并行加載引腳,稱為PL (Parallel Load)。通過將PL引腳置高,可以使芯片進入并行加載模式。在這種模式下,芯片會讀取并行引腳的狀態,并將數據存儲到內部的存儲單元中。當PL引腳置低時,芯片將停止并行加載,并將存儲的數據保持不變。

- 串行時鐘:SN74HC165DR具有一個串行時鐘引腳,稱為CLK (Clock)。通過在每個時鐘脈沖到來時改變輸入數據,可以實現數據的串行移位操作。

SN74HC165DR的工作原理

SN74HC165DR的工作過程可以分為以下幾個步驟:

- 并行加載:如果PL引腳置高,芯片將進入并行加載模式。此時,芯片將讀取并行輸入引腳A0~A7的狀態,并將這些數據存儲到內部的存儲單元中。

- 移位操作:如果SH/LD引腳置高,芯片將進入移位模式。在移位模式下,芯片將按順序將存儲的數據從Q7引腳輸出。通過在每個時鐘脈沖到來時改變輸入數據,芯片可以實現數據的串行移位操作。

- 控制時序:芯片內部的控制電路會根據時鐘信號和控制引腳的狀態來控制數據的傳輸。通過適當的時序控制,可以確保數據的穩定和準確的傳輸。

總結

SN74HC165DR是一種功能豐富的集成電路芯片,具有高速、高性能和低功耗的特性。它可以將并行輸入轉換為串行輸出,并通過適當的時序控制實現數據的穩定和準確的傳輸。在數字電子系統中,SN74HC165DR扮演著重要的角色,廣泛應用于數據采集、控制和通信等領域。通過對SN74HC165DR的工作原理的詳細了解,我們可以更好地理解和應用這一功能強大的集成電路芯片。

-

芯片

+關注

關注

455文章

50817瀏覽量

423676 -

集成電路

+關注

關注

5388文章

11547瀏覽量

361836 -

移位寄存器

+關注

關注

3文章

258瀏覽量

22274

發布評論請先 登錄

相關推薦

[轉帖]SN74HC165DR的技術參數

74hc165無法使用

74HC165讀取按鍵鍵值的問題

74HC165

74HC165編程篇

74HC165 pdf datasheet

用74HC165讀8個按鍵狀態

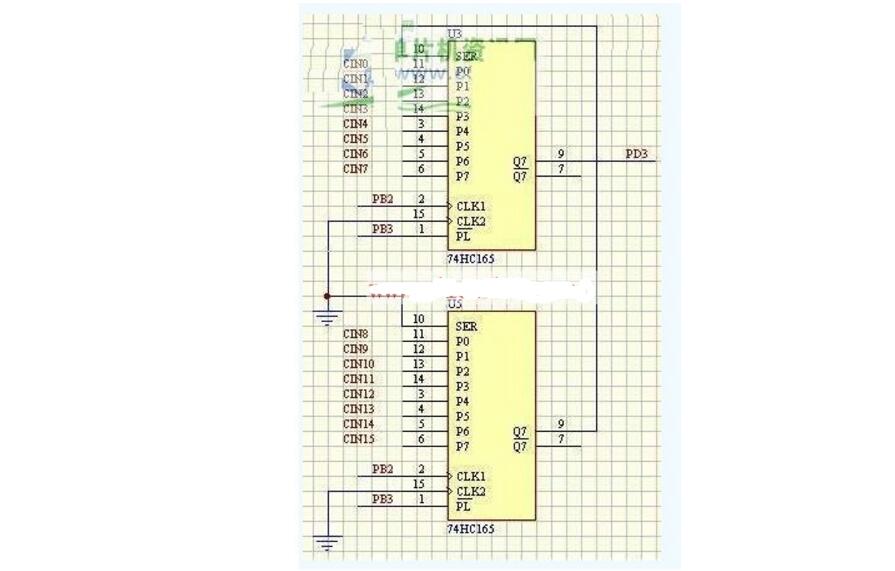

74hc165中文資料詳細(74hc165工作原理_引腳圖及功能_應用電路_邏輯圖)

74hc165使用方法(74hc165功能_內部結構圖_時序圖)

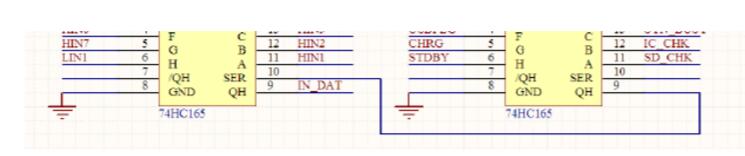

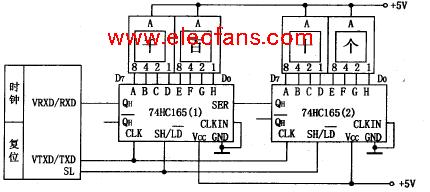

74hc165級聯用法(74hc165級聯電路圖及程序)

SN74HC165-EP 增強型產品 8 位并行負載移位寄存器

sn74hc165dr工作原理

sn74hc165dr工作原理

評論