1,帶寬

示波器帶寬的定義沒有變,就是輸入一個正弦波,保持幅度不變,增加信號頻率,當示波器上顯示的信號是實際信號幅度的70.7%(即3dB衰減)的時候,該對應的頻率就等于示波器帶寬。100MHz的帶寬在測量100MHz的正弦波時,幅度會下降到原來的0.7,但是100mhz帶寬的示波器不能測100mhz的方波,因為方波由基波和奇次諧波組成,5次以下的諧波對方波波形影響很大,所有要較好的看清楚方波,示波器帶寬至少要比待測波形頻率大5倍。

2.采樣率

每秒采樣多少個樣點。根據香農定理,為了避免波形混疊,采樣率應該大于波形頻率的2倍。一般來說采樣率是帶寬的5倍即可,比如200M帶寬的示波器,配1G采樣率就可以了。追求更高的采樣率無非為了抓小毛刺,但是這些高頻毛刺在帶寬層已經被濾掉了,更高的采樣率并不能帶來很好的收益。

3.存儲深度

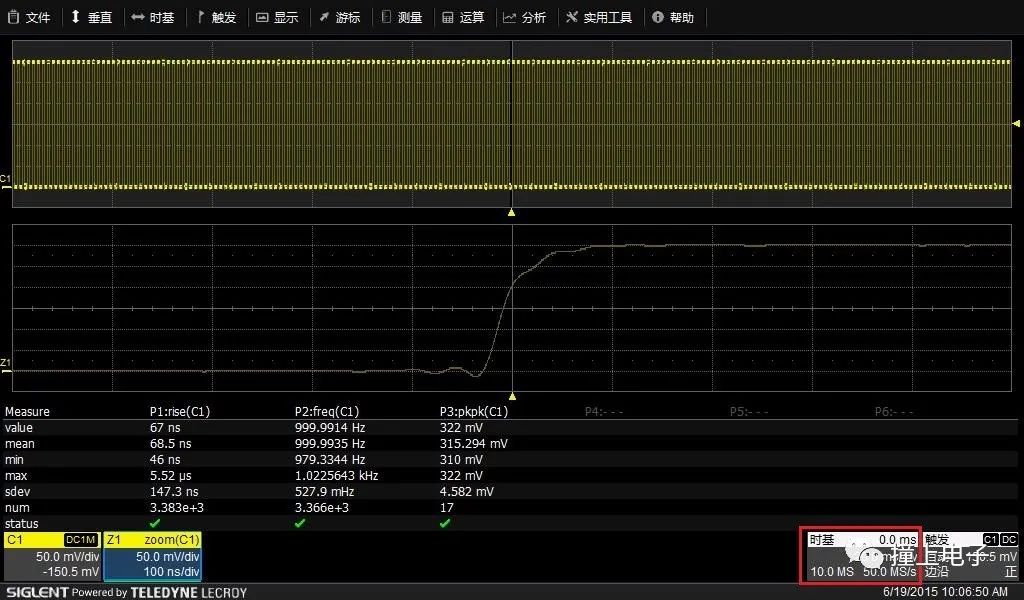

表示示波器可以保存的采樣點的個數。存儲深度=采樣率*采樣時間。我一直執著地將它稱為示波器中的第一關系式,因為很多工程師在使用示波器過程中因為忘記這個關系式而產生錯誤。如下圖為鼎陽科技SDS3000示波器的顯示界面。右下方紅色方框中,右邊兩個數值50MS/s和20ms/div相乘,再乘以10,就等于左邊的數10MS。當前采樣率為50MS/s,當前時基為20ms/div,因為水平軸是10格(有些示波器是12格或14格),因此采樣時間為200ms, 50MS/s * 200ms = 10MS。就是說以50MS/s的采樣率捕獲200ms的波形,需要示波器的存儲深度是10MS。

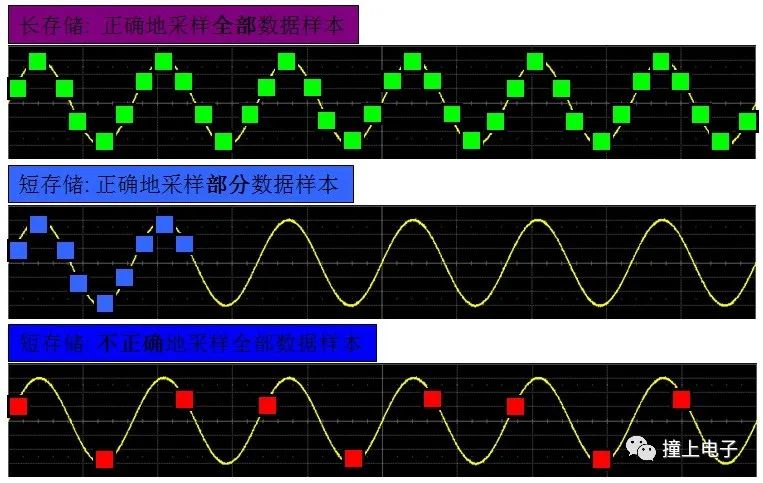

下面的示意圖也清晰地演繹了這個關系式的重要性。第一個圖形表明在采樣率足夠的前提下觀察多個周期的樣本,需要的存儲深度深度很長,圖示中需要36個采樣點。第二個圖形采樣率依然保持不變,但存儲深度變小,只有9個采樣點,因此只能采樣一個周期多點的波形。第三個波形仍然是存儲深度很小,只有9個采樣點,但仍然要采樣和第一個圖形一樣多個周期的波形,其結果是采樣率變小,測量得到的波形就會失真。

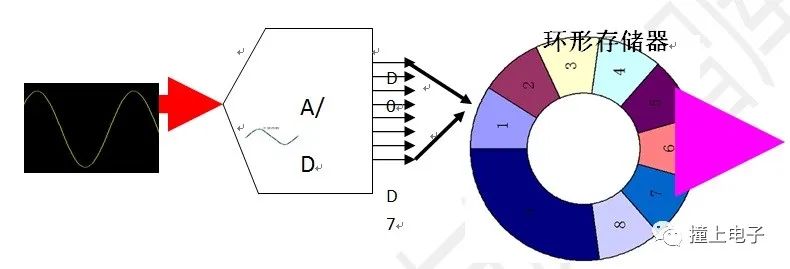

假如存儲深度是“1千萬個采樣點”,示波器廠商寫作10Mpts,10MS或10M的都有。這里,pts可以理解為points的縮寫,S理解為Samples的意思。存儲器保存滿了,達到存儲深度的極限之后怎么辦?我們可以將示波器的存儲器理解為環形存儲器。示波器不斷采樣得到新的采樣點會填充進來,老的采樣點會自動地溢出,這樣周而復始的過程直到示波器被“觸發信號”“叫停”或者間隔一定長的時間被強迫“叫停”為止。“叫停”一次,示波器就將存儲器中保存的這些采樣點“搬移”到示波器的屏幕上顯示。這兩次“搬移”之間等待的時間相對于采樣的時間極其漫長,被稱為“死區時間”。

對于高端示波器,存儲器芯片一直是核心技術,對于里面的技術細節筆者知之甚少。示波器中的ADC速率太快,普通的存儲介質根本來不及在這么短的時間內“吞吐”那么大量的數據量。還是用具體的數字來理解高速ADC的超大數據量對存儲器“吞吐量”提出的要求。譬如ADC的采樣率是20GS/s,也就是說每秒鐘要采樣20G個點,而每個點是由8個0和1組成。如果ADC的輸出是完全按照串行數據的傳輸到存儲器中,那么傳輸速率就是160Gbps。這是什么概念?現在的PCI-Express 3.0的速率是 8Gbps,最高速的高速芯片在單板上傳輸速率能達到25Gbps,但還不成熟,也沒有用到示波器上。高速ADC的采樣點怎么傳輸到存儲器中,這是一個難題! 其實這么高速的ADC也不可能是單芯片設計的,內部是由很多2.5GS/s或1.25GS/s,250MS/s的“小的”ADC“交織拼接”實現的。既然不完全是串行的方式實現,采用并行傳輸之后,傳輸到存儲器的數據又怎么校準、對齊,再通過觸發機制規整地顯示到示波器屏幕上呢?這是示波器廠商的一點點小秘密。示波器發展到今天這方面門檻談不上多高,但還是有那么一點點的。一個示波器的帶寬是40Mhz,40MHZ是指示波器能測量標準正弦波的能力.但因為平時用示波器測試時基本不是正弦波,所以我們在考慮示波器帶寬時,通常會按被測信號頻率的三倍來考慮,更高倍當然最好.所以一定要注意,不是40 MHZ的示波器就能測40MHZ的所有信號.如果是數字示波器要,注意存儲深度、采樣率等都是很重要的。

-

示波器

+關注

關注

113文章

6246瀏覽量

184941 -

存儲

+關注

關注

13文章

4314瀏覽量

85842 -

帶寬

+關注

關注

3文章

929瀏覽量

40921

發布評論請先 登錄

相關推薦

泰克公司推出三個用于示波器的安卓應用程序

示波器不可忽略的一個重要參數

“三個張江”的概念

EMC三個重要規律

示波器的兩個最重要參數之示波器寬帶和采樣率詳解

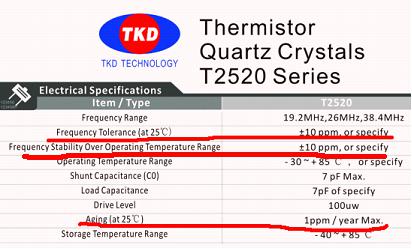

晶振選型時必須考慮的三個重要參數

示波器最重要的三個參數

示波器最重要的三個參數

評論