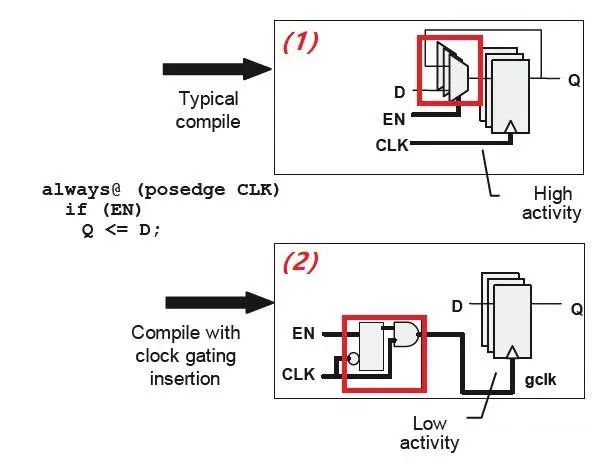

時鐘XOR自門控(Self Gating)基本思路和時鐘門控類似,都是當寄存器中的數據保持不變時,通過關閉某些寄存器的時鐘信號來降低設計的動態功耗。不過XOR 自門控是利用異或門(XOR)將存儲在寄存器中的數據與到達寄存器的數據引腳的數據進行比較,輸出門控時鐘使能信號。

在講解XOR自門控之前,先回顧一下時鐘門控(Clock Gating)技術的缺點。

時鐘門控使用條件:

代碼中有確定的門控時鐘使能信號或者有門控時鐘使能譯碼邏輯存在。比如下面代碼中的EN信號:

input [n:0] D;

input CLK,EN;

output [n:0] Q;

always@ (posedge CLK)

begin

if (EN)

Q<=D;

end

時鐘門控的缺陷:

從上面代碼能看出,要想使用時鐘門控技術,對代碼風格有一定的要求,得有時鐘門控信號。這可是硬傷,畢竟設計中不可能所有的寄存器都能找到這樣邏輯,也不能保證所有寫Verilog代碼的人都有這樣的覺悟。

因此,這就導致設計中有些寄存器組無法采用門控時鐘技術。

XOR自門控與時鐘門控的不同之處:

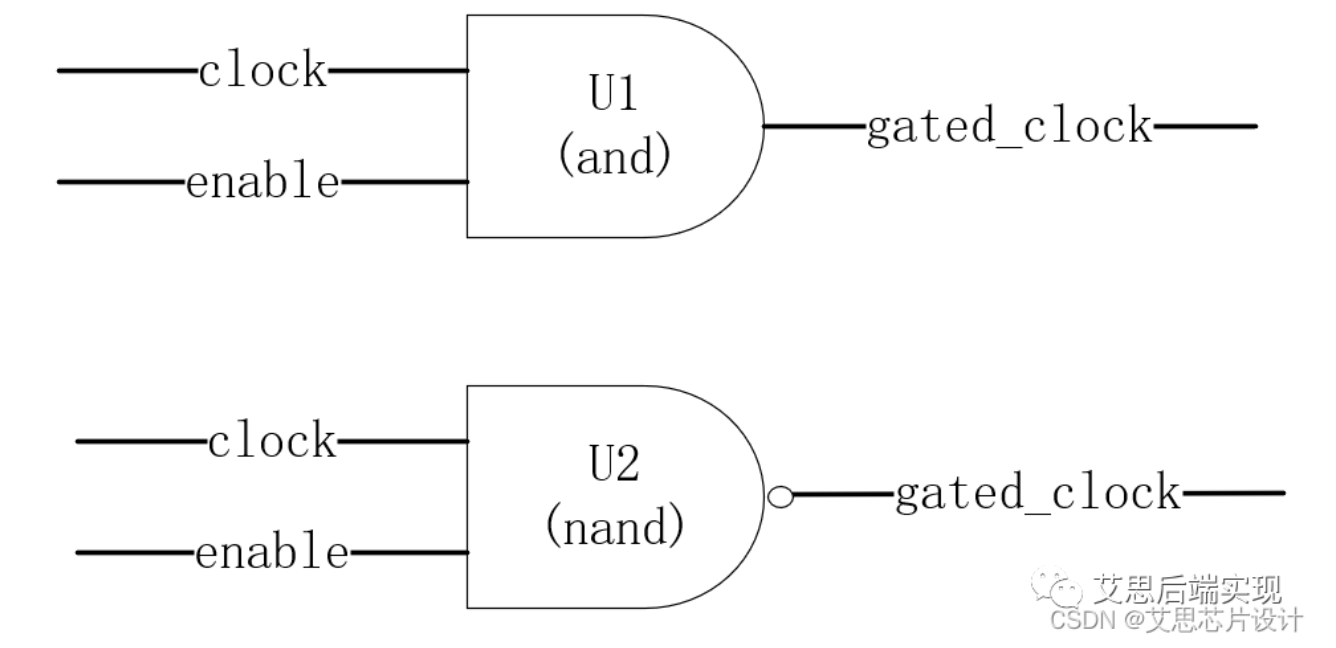

與時鐘門控的不同之處在于,時鐘門控技術依賴于現有設計中的使能條件,而XOR 自門控則利用異或門(XOR)將存儲在寄存器中的數據與到達寄存器的數據引腳的數據進行比較,輸出門控時鐘使能信號。如果數據不變,則由異或門直接關斷寄存器的時鐘輸入信號。下圖顯示了插入XOR自門控單元產生門控時鐘使能信號的原理。

XOR自門控單元

XOR自門控的優點:

默認情況下,工具僅支持非門控時鐘寄存器上的XOR自門控。

以下是XOR自門控的優點:

?有些情況,某些寄存器的使能條件無法從現有邏輯推斷出,因此無法用傳統的門控時鐘技術來關斷它們的時鐘信號。這種情況下可以使用XOR自門控來關斷它們的時鐘信號;

?時鐘門控和XOR自門控并不沖突,可以同時使用。對于那些已經采用門控時鐘關斷的寄存器,可以使用下面的命令允許在這些寄存器上采用XOR自門控:

set_self_gating_options

-interaction_with_clock_gating

采用了該技術之后,這些寄存器時鐘信號的關斷時間可能會增加。

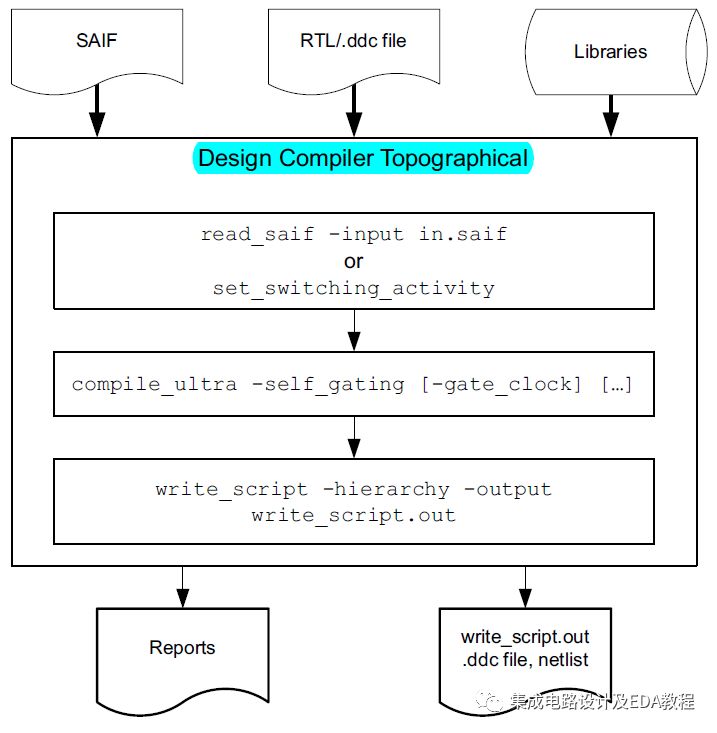

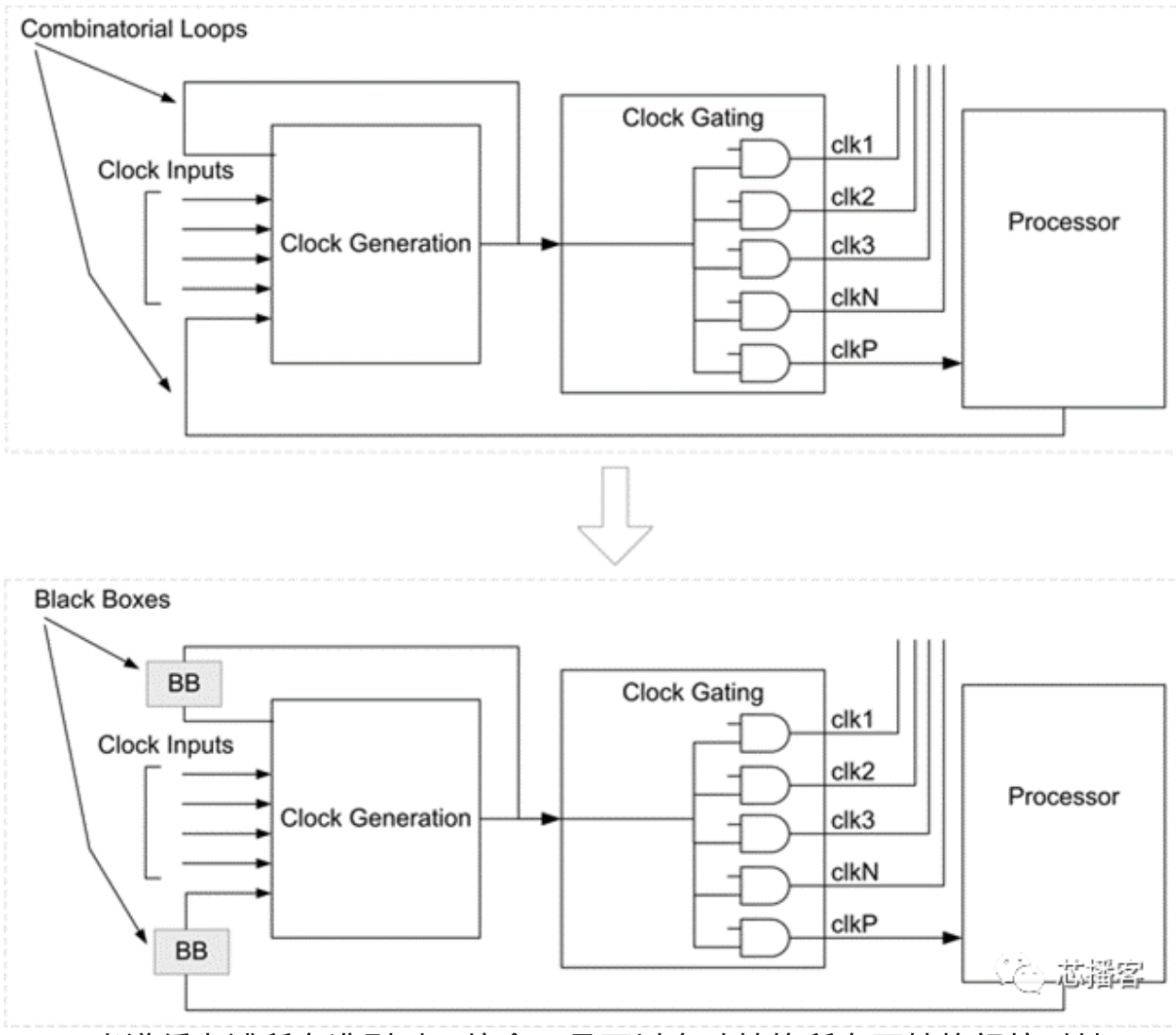

DCT實現的Flow:

DCT實現的Flow

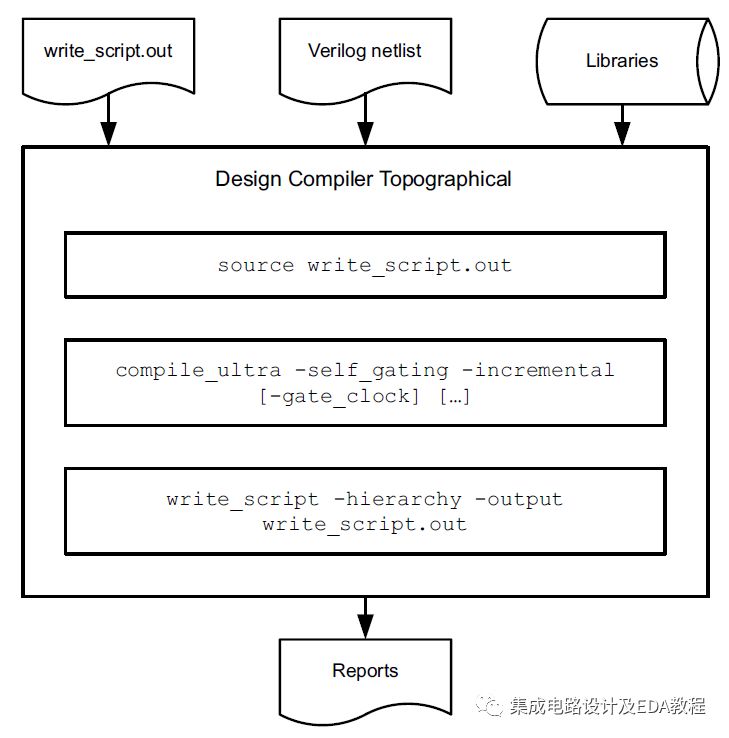

注意:當具有XOR自門控單元的ASCII網表被讀回到Power Compiler工具中時,所有屬性信息都將丟失,并且工具無法識別自門控單元用于報告或優化。Power Compiler工具使用write_script命令支持XOR自門控ASCII流程。如下圖所示,使用下面的命令保存設計的當前屬性:

write_script -hierarchy -output file_name

XOR Self-Gating ASCII Flow

將需要將設計讀回工具時,可以使用source命令來加載由write_script命令導出的腳本。這將設置設計中的所有必需屬性,包括用于報告和優化目的的自門控單元。

DCT實現:

使用set_self_gating_objects命令可以指定XOR自門控的對象,運行compile_ultra -self_gating命令時會執行XOR自門控。

如果不想對MID子設計中的D_OUT寄存器組執行XOR自門控,可以用下面的命令:

dc_shell-topo> set_self_gating_objects -exclude MID/D_OUT_reg[*]

dc_shell-topo> compile_ultra -self_gating

對時鐘門控寄存器執行XOR自門控:

默認情況下,Power Compiler工具不會在時鐘門控寄存器上執行XOR自門控。如果要對時鐘門控的寄存器執行XOR自門控,可以使用以下命令:

dc_shell-topo> set_self_gating_options

-interaction_with_clock_gating insert

指定XOR自門控選項:

要指定XOR自動門控的條件并定義與時鐘門控的交互,使用set_self_gating_options命令。在用命令compile_ultra -self_gating進行編譯,Power Compiler插入XOR門時,會采用這些設置。

應用舉例:

使用set_self_gating_options命令,對2位到9位之間的寄存器插入XOR自門控:

dc_shell-topo> set_self_gating_options -min_bitwidth 2 -max_bitwidth 9

dc_shell-topo> compile_ultra -self_gating

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5343瀏覽量

120377 -

時鐘

+關注

關注

10文章

1733瀏覽量

131485 -

門控時鐘

+關注

關注

0文章

27瀏覽量

8951 -

XOR

+關注

關注

0文章

12瀏覽量

161959

原文標題:數字IC低功耗設計之--XOR自門控與Design Compiler topo實現

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

fpga門控時鐘問題

FPGA的時鐘門控是好還是壞?

什么是時鐘門控?如何去實線時鐘門控的設計呢

基于門控時鐘的低功耗電路設計方案

XOR自門控與時鐘門控的不同之處

XOR自門控與時鐘門控的不同之處

評論