(一)單bit信號(hào)同步器

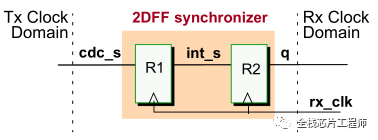

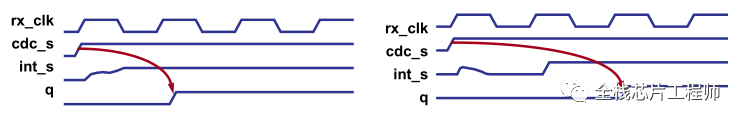

最經(jīng)典的2DFF 1-bit同步器如下,下圖結(jié)構(gòu)通常用于單bit控制信號(hào)的異步處理:

絕大數(shù)情況下,當(dāng)?shù)谝粋€(gè)寄存器R1進(jìn)入亞穩(wěn)態(tài)后,在第二級(jí)寄存器R2采樣R1的輸出前,R1的輸出已經(jīng)能穩(wěn)定在0或1。

注意:

cdc_s信號(hào)必須做到glitch free,也就是我們通常說(shuō)的寄存輸出;

int_s信號(hào)鏈路禁止組合邏輯,其本質(zhì)也是杜絕glitch的出現(xiàn)。

偏執(zhí)狂的IC designer肯定會(huì)問(wèn),第一級(jí)寄存器R1的行為到底是啥樣子的?由于cdc_s信號(hào)是Tx clock Domain,而R1寄存器的采用時(shí)鐘是Rx clock Domain,當(dāng)Rx clock采樣時(shí),若cdc_s正好跳變(不滿足setup/hold),那么就會(huì)出現(xiàn)如下兩種情況,而前仿真是無(wú)法仿真出下圖2種行為的(具體見(jiàn)芯片設(shè)計(jì)之CDC異步電路(一)一文)。

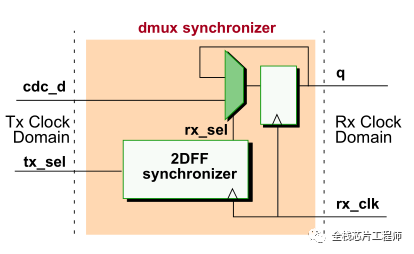

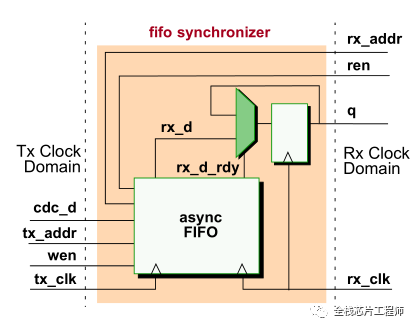

(二)DMUX同步器 兩級(jí)寄存器(先進(jìn)工藝要求三級(jí))的同步器通常用于控制信號(hào)的異步處理,但是data bus的異步處理呢?我們可以采用DMUX結(jié)構(gòu)。

注意:

tx_sel、rx_sel有效時(shí),cdc_d數(shù)據(jù)總線必須保持穩(wěn)定;

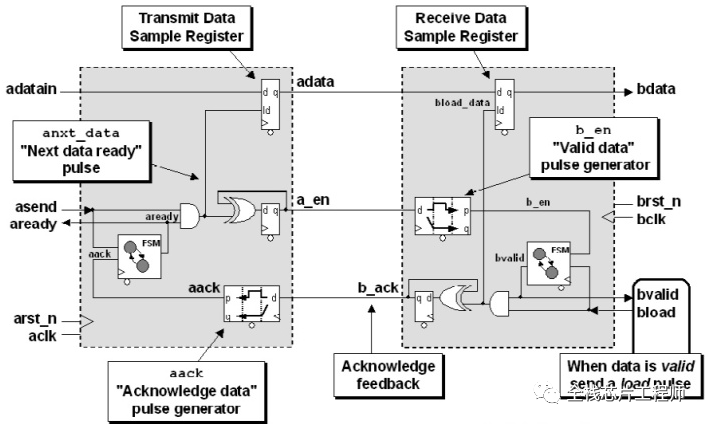

(三)握手處理

源時(shí)鐘域先將數(shù)據(jù)發(fā)送到總線上,并給出一個(gè)valid信號(hào),而目標(biāo)時(shí)鐘域同步valid信號(hào)后,若valid信號(hào)為高電平則采樣總線數(shù)據(jù),并返回一個(gè)ready信號(hào)給源時(shí)鐘域。源時(shí)鐘域再次同步該ready信號(hào),若ready信號(hào)為高,則代表一次握手成功,數(shù)據(jù)傳輸完畢,開(kāi)始進(jìn)行下一次數(shù)據(jù)傳輸。

采用握手機(jī)制可以保證異步multi-bit數(shù)據(jù)傳輸不出現(xiàn)錯(cuò)誤,但由于需要等待握手的完成再傳輸數(shù)據(jù),因此傳輸效率較低。

(四)異步FIFO

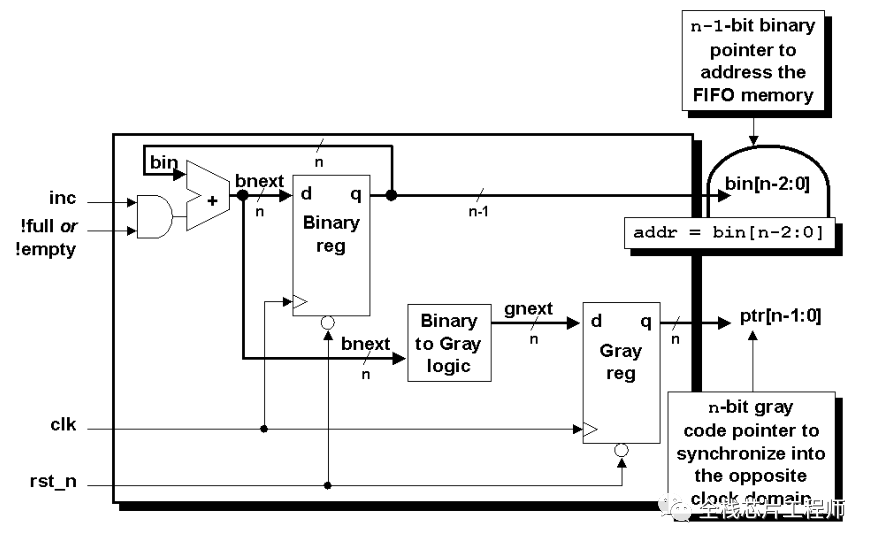

老生常談的異步FIFO,其本質(zhì)是采用格雷碼,在地址連續(xù)的情況下,其對(duì)應(yīng)格雷碼每個(gè)周期只變化1bit,因此可以直接異步采樣。

注意:

FIFO的overflow、underflow問(wèn)題;

tx_addr是連續(xù)的,即地址hamming distance是1;

FIFO深度須2^n;

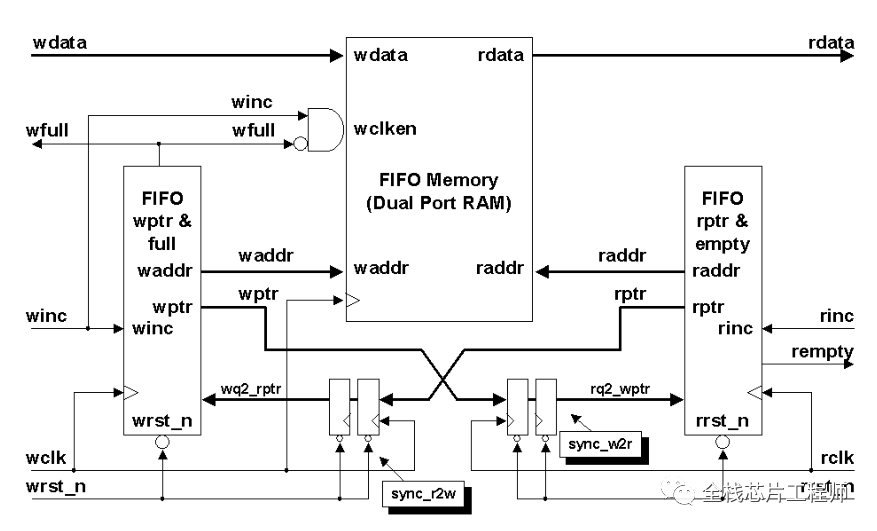

經(jīng)典的FIFO結(jié)構(gòu)如下:

核心電路:是將FIFO讀寫(xiě)地址指針的二進(jìn)制碼轉(zhuǎn)成格雷碼,方便同步器打兩拍傳遞到對(duì)向時(shí)鐘域去做空滿判斷。

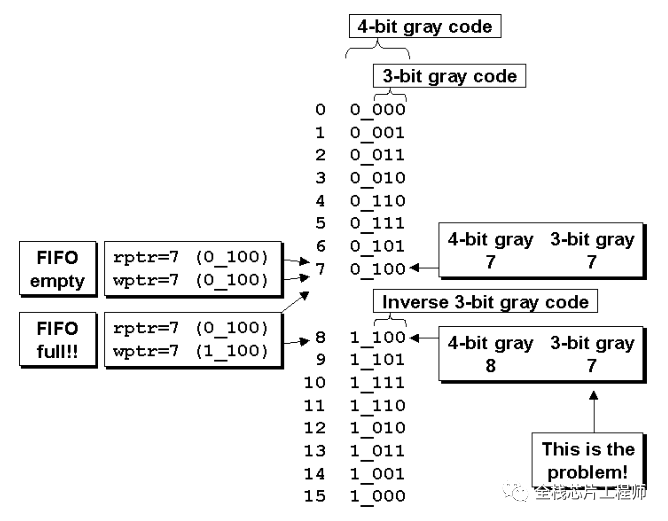

空滿判斷:為了區(qū)別空滿,我們?cè)黾?bit的地址(MSB),我習(xí)慣直接用Gray碼比較讀寫(xiě)指針判定空滿:

當(dāng)Gray碼讀寫(xiě)指針完全相等時(shí),F(xiàn)IFO空;

當(dāng)Gray碼讀寫(xiě)指針最高2bit相反,其余bit相同時(shí),F(xiàn)IFO滿; 通常二進(jìn)制碼比較空滿是:最高bit不同,其余bit相同,則FIFO滿,而格雷碼則不同哈。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5401瀏覽量

122748 -

CDC

+關(guān)注

關(guān)注

0文章

57瀏覽量

18065 -

同步器

+關(guān)注

關(guān)注

1文章

104瀏覽量

14983 -

FIFO存儲(chǔ)

+關(guān)注

關(guān)注

0文章

103瀏覽量

6119 -

異步處理

+關(guān)注

關(guān)注

0文章

7瀏覽量

6607

原文標(biāo)題:芯片跨時(shí)鐘域設(shè)計(jì)(一)

文章出處:【微信號(hào):全棧芯片工程師,微信公眾號(hào):全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

跨時(shí)鐘域控制信號(hào)傳輸設(shè)計(jì)方案

關(guān)于跨時(shí)鐘域信號(hào)的處理方法

如何處理好FPGA設(shè)計(jì)中跨時(shí)鐘域間的數(shù)據(jù)

兩級(jí)DFF同步器跨時(shí)鐘域處理簡(jiǎn)析

FPGA跨時(shí)鐘域處理簡(jiǎn)介

如何利用FPGA設(shè)計(jì)一個(gè)跨時(shí)鐘域的同步策略?

關(guān)于FPGA中跨時(shí)鐘域的問(wèn)題分析

fpga跨時(shí)鐘域通信時(shí),慢時(shí)鐘如何讀取快時(shí)鐘發(fā)送過(guò)來(lái)的數(shù)據(jù)?

如何處理跨時(shí)鐘域這些基礎(chǔ)問(wèn)題

評(píng)論