大家不要以為APB的master和slave很簡單,不需要了解。這是大錯(cuò)特錯(cuò),為什么呢?

不過設(shè)計(jì)什么模塊,你都要讓它掛在標(biāo)準(zhǔn)總線上,比如你設(shè)計(jì)DMA,你就同時(shí)需要了解AMBA的master和slave設(shè)計(jì)。又比如你是設(shè)計(jì)算法計(jì)算模塊,你的數(shù)據(jù)肯定要放到sram,你當(dāng)然也要了解AMBA的master設(shè)計(jì),將數(shù)據(jù)傳輸?shù)絚rossbar上,進(jìn)而放到指定memory。又比如SOC設(shè)計(jì),肯定需要各種bridge,假設(shè)一個(gè)AHB2APB,你就同時(shí)需要了解AHB slave和APB master。

以APB為例,還是因?yàn)锳PB簡單,但是我們可以從它學(xué)到設(shè)計(jì)的方法和思路。

既然是設(shè)計(jì)就需要spec和狀態(tài)機(jī)。

設(shè)計(jì)spec如下

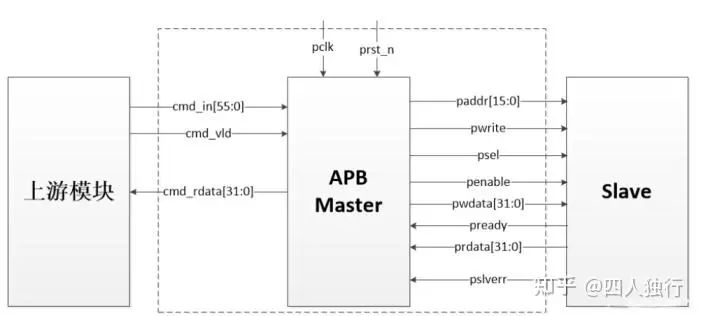

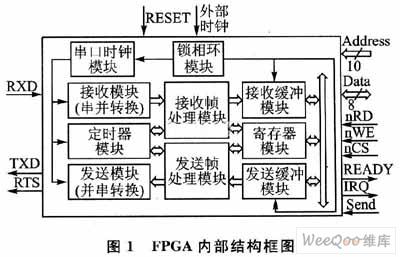

1、模塊規(guī)劃

模塊diagram

2、接口描述

接口描述

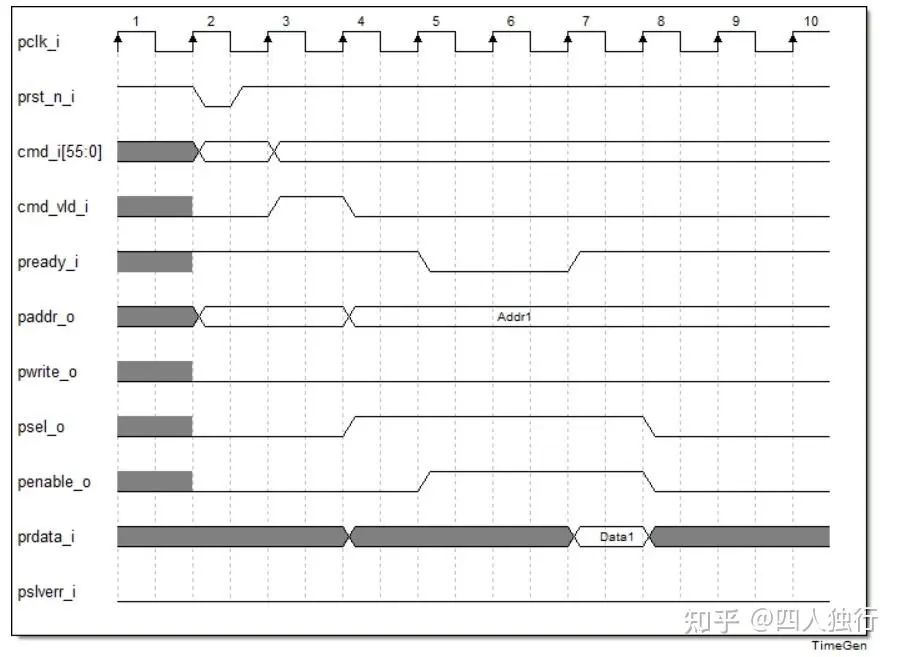

3、時(shí)序描述

讀時(shí)序

讀時(shí)序

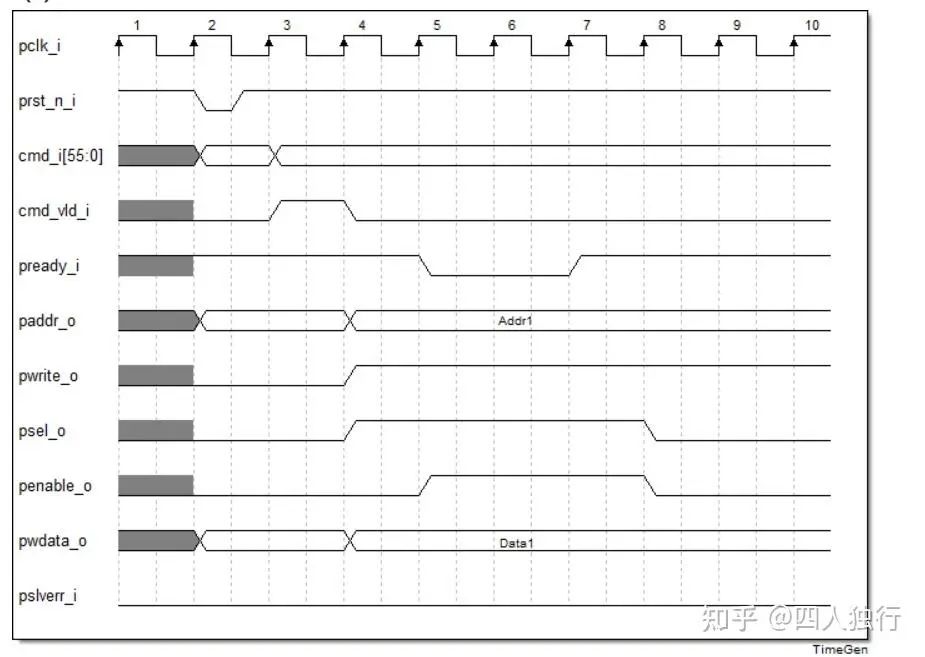

寫時(shí)序

寫時(shí)序

4、FSM

就是之前講的APB協(xié)議狀態(tài)機(jī)。如下圖

APB FSM

模塊規(guī)劃有了,接口有了,時(shí)序有了,狀態(tài)機(jī)有了,就可以開始設(shè)計(jì)coding了,代碼如下:

module apb #( parameter RD_FLAG = 8'b0 , parameter WR_FLAG = 8'b1 , parameter CMD_RW_WIDTH = 8 , parameter CMD_ADDR_WIDTH = 16 , parameter CMD_DATA_WIDTH = 32 , parameter CMD_WIDTH = CMD_RW_WIDTH + CMD_ADDR_WIDTH + CMD_DATA_WIDTH )( //-- clkrst signal input pclk_i , input prst_n_i , //-- cmd_in input [CMD_WIDTH-1:0] cmd_i , input cmd_vld_i , output reg [CMD_DATA_WIDTH-1:0] cmd_rd_data_o, //-- apb interface output reg [CMD_ADDR_WIDTH-1:0] paddr_o , output reg pwrite_o , output reg psel_o , output reg penable_o , output reg [CMD_DATA_WIDTH-1:0] pwdata_o , input [CMD_DATA_WIDTH-1:0] prdata_i , input pready_i , input pslverr_i ); //-- FSM state parameter IDLE = 3'b001; parameter SETUP = 3'b010; parameter ACCESS = 3'b100; //-- current state and next state reg [2:0] cur_state; reg [2:0] nxt_state; //-- data buf reg start_flag ; reg [CMD_WIDTH-1:0] cmd_in_buf ; reg [CMD_DATA_WIDTH-1:0] cmd_rd_data_buf; /*----------------------------------------------- -- update cmd_in_buf -- -----------------------------------------------*/ always @ (posedge pclk_i or negedge prst_n_i) begin if (!prst_n_i) begin cmd_in_buf <= {(CMD_WIDTH){1'b0}}; end else if (cmd_vld_i && pready_i) begin cmd_in_buf <= cmd_i; end end /*----------------------------------------------- -- start flag of transfer -- -----------------------------------------------*/ always @ (posedge pclk_i or negedge prst_n_i) begin if (!prst_n_i) begin start_flag <= 1'b0; end else if (cmd_vld_i && pready_i) begin start_flag <= 1'b1; end else begin start_flag <= 1'b0; end end /*----------------------------------------------- -- update current state -- -----------------------------------------------*/ always @ (posedge pclk_i or negedge prst_n_i) begin if (!prst_n_i) begin cur_state <= IDLE; end else begin cur_state <= nxt_state; end end /*----------------------------------------------- -- update next state -- -----------------------------------------------*/ always @ (*) begin case(cur_state) IDLE :if(start_flag)begin nxt_state = SETUP; end else begin nxt_state = IDLE; end SETUP :nxt_state = ACCESS; ACCESS:if (!pready_i)begin nxt_state = ACCESS; end else if(start_flag)begin nxt_state = SETUP; end else if(!cmd_vld_i && pready_i)begin nxt_state = IDLE; end endcase end /*----------------------------------------------- -- update signal of output -- -----------------------------------------------*/ always @ (posedge pclk_i or negedge prst_n_i) begin if (!prst_n_i) begin pwrite_o <= 1'b0; psel_o <= 1'b0; penable_o <= 1'b0; paddr_o <= {(CMD_ADDR_WIDTH){1'b0}}; pwdata_o <= {(CMD_DATA_WIDTH){1'b0}}; end else if (nxt_state == IDLE) begin psel_o <= 1'b0; penable_o <= 1'b0; end else if(nxt_state == SETUP)begin psel_o <= 1'b1; penable_o <= 1'b0; paddr_o <= cmd_in_buf[CMD_WIDTH-CMD_RW_WIDTH-1:CMD_DATA_WIDTH]; //-- read if(cmd_in_buf[CMD_WIDTH-1:CMD_WIDTH-8] == RD_FLAG)begin pwrite_o <= 1'b0; end //-- write else begin pwrite_o <= 1'b1; pwdata_o <= cmd_in_buf[CMD_DATA_WIDTH-1:0]; end end else if(nxt_state == ACCESS)begin penable_o <= 1'b1; end end /*----------------------------------------------- -- update cmd_rd_data_buf -- -----------------------------------------------*/ always @ (posedge pclk_i or negedge prst_n_i) begin if (!prst_n_i) begin cmd_rd_data_buf <= {(CMD_DATA_WIDTH){1'b0}}; end else if (pready_i && psel_o && penable_o) begin cmd_rd_data_buf <= prdata_i; end end /*----------------------------------------------- -- update cmd_rd_data_o -- -----------------------------------------------*/ always @ (posedge pclk_i or negedge prst_n_i) begin if (!prst_n_i) begin cmd_rd_data_o <= {(CMD_DATA_WIDTH){1'b0}}; end else begin cmd_rd_data_o <= cmd_rd_data_buf; end end endmodule

模塊設(shè)計(jì)的比較簡單,只是實(shí)現(xiàn)APB的基本功能。下面講一下設(shè)計(jì)重點(diǎn):

·一定要做好功課在開始coding。

·Flow control,APB的上級模塊,需要給到流控信號,告知APB master什么時(shí)候開始傳輸,什么時(shí)候結(jié)束。

·FSM,必須完全遵循AMBA的datasheet。

·時(shí)序?qū)R,和FSM一樣,接口時(shí)序要和APB協(xié)議對齊。

·重點(diǎn)中的重點(diǎn),pready的反壓一定要逐級反壓,不能直接送到APB master的上次模塊,這樣會丟數(shù)據(jù)。

testbench如下

`timescale 1ns/1ns module tb_apb; reg pclk_i ; reg prst_n_i ; reg [55:0] cmd_i ; reg cmd_vld_i ; wire [31:0] cmd_rd_data_o; wire [15:0] paddr_o ; wire pwrite_o ; wire psel_o ; wire penable_o ; wire [31:0] pwdata_o ; reg [31:0] prdata_i ; reg pready_i ; reg pslverr_i ; initial begin // rst; pclk_i = 0; prst_n_i = 1; pslverr_i = 0; cmd_i = 56'b0; cmd_vld_i = 0; prdata_i = 32'b0; pready_i = 1; #20 prst_n_i = 0; #20 prst_n_i = 1; // cmd_in_wr(cmd_i,56'h01_FF_EE_DD_CC_BB_AA); cmd_i = 56'h01_FF_EE_DD_CC_BB_AA; cmd_vld_i = 1 ; #20 cmd_vld_i = 0; #31 pready_i = 0; #80 pready_i = 1; #90; //cmd_in_rd(cmd_i,56'h00_AA_BB_CC_DD_EE_FF,prdata_i,32'h12_34_56_78); cmd_i = 56'h00_AA_BB_CC_DD_EE_FF; cmd_vld_i = 1; #20 cmd_vld_i = 0; #30 pready_i = 0; #60 pready_i = 1; prdata_i = 32'h12_34_56_78; cmd_i = 56'h00_AA_BB_CC_DD_EE_FF; cmd_vld_i = 1; #20 cmd_vld_i = 0; #30 pready_i = 0; #50 pready_i = 1; prdata_i = 32'h11_22_33_44; end always #10 pclk_i = ~pclk_i; //-- RST task rst; begin pclk_i = 1; prst_n_i = 1; pslverr_i = 0; cmd_i = 56'b0; cmd_vld_i = 0; prdata_i = 32'b0; pready_i = 1; #20 prst_n_i = 0; #10 prst_n_i = 1; //cmd_i = 56'h01_FF_EE_DD_CC_BB_Ab; end endtask //-- write task cmd_in_wr; output [55:0] cmd; input [55:0] data; begin cmd = data; cmd_vld_i = 1 ; #20 cmd_vld_i = 0; #20 pready_i = 0; #40 pready_i = 1; end endtask //-- read task cmd_in_rd; output [55:0] cmd; input [55:0] data ; output [31:0] prdata; input [31:0] rd_data; begin cmd = data; cmd_vld_i = 1; #20 cmd_vld_i = 0; #20 pready_i = 0; #40 pready_i = 1; prdata = rd_data; end endtask initial begin #1000 $finish; end apb tb_apb( .pclk_i (pclk_i ), .prst_n_i (prst_n_i ), .cmd_i (cmd_i ), .cmd_vld_i (cmd_vld_i ), .cmd_rd_data_o(cmd_rd_data_o), .paddr_o (paddr_o ), .pwrite_o (pwrite_o ), .psel_o (psel_o ), .penable_o (penable_o ), .pwdata_o (pwdata_o ), .prdata_i (prdata_i ), .pready_i (pready_i ), .pslverr_i (pslverr_i ) ); initial begin $fsdbDumpfile("apb.fsdb"); $fsdbDumpvars ; $fsdbDumpMDA ; end endmodule

makefile如下:

LAB_DIR = /home/*/apb DFILES = $(LAB_DIR)/*.v all:clean elab rung elab: vcs -full64 -LDFLAGS -Wl,-no-as-needed -debug_acc+all -timescale=1ns/1ns -fsdb -sverilog -l comp.log ${DFILES} run: ./simv -l run.log rung: ./simv -gui -l run.log verdi: verdi ${DFILES} -ssf ./*.fsdb & clean: rm -rf AN.DB rm -rf DVEfiles rm -rf csrc rm -rf simv.* rm -rf *simv rm -rf inter.vpd rm -rf ucli.key rm -rf *.log rm -rf verdiLog rm -rf novas* rm-rf*.fsdb

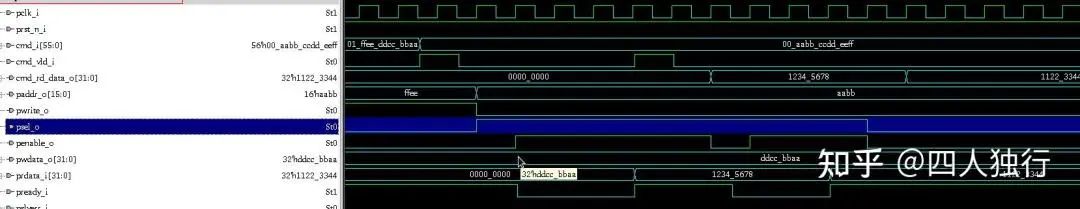

下面是仿真結(jié)果

好了,今天講的主要就這么多,這個(gè)是基礎(chǔ),但也是干貨,對以后設(shè)計(jì)AHB,AXI乃至NOC都非常有幫助。

審核編輯:黃飛

-

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

1891瀏覽量

64601 -

soc

+關(guān)注

關(guān)注

38文章

4165瀏覽量

218259 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

492瀏覽量

27541

原文標(biāo)題:SoC設(shè)計(jì)入門 - APB master設(shè)計(jì)(接口類基礎(chǔ)思維)

文章出處:【微信號:IP與SoC設(shè)計(jì),微信公眾號:IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Modbus多主站問題

CAN主站與從站的功能是什么

Profibus-DP主站通信平臺的設(shè)計(jì)方案

MELSEC iQ R CC Link系統(tǒng)主站/本地站模塊用戶手冊(入門篇)

MELSEC iQ R AnyWireASlink主站模塊用戶手冊(入門篇)

MELSEC iQ R DeviceNet主站/從站模塊用戶手冊(入門篇)

EtherCAT 主站方案橫向?qū)Ρ?/a>

EtherCAT主站方案之橫向比較

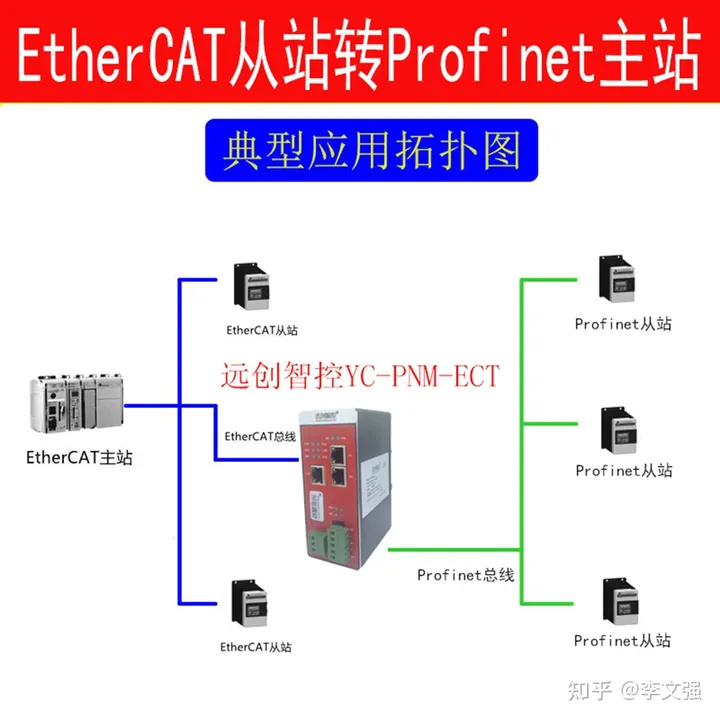

通過Profinet主站轉(zhuǎn)EtherCAT協(xié)議網(wǎng)關(guān)把profient從站設(shè)備接入到EtherCAT主站設(shè)備中

SoC入門:APBmaster設(shè)計(jì)主站設(shè)計(jì)原理與實(shí)踐

SoC入門:APBmaster設(shè)計(jì)主站設(shè)計(jì)原理與實(shí)踐

評論